嵌入式ARM MPcore平台JPEG并行编码的研究

2016-08-31廖醒宇余水来

廖醒宇,余水来

(长春理工大学 电子信息工程学院,长春 130022)

嵌入式ARM MPcore平台JPEG并行编码的研究

廖醒宇,余水来

(长春理工大学 电子信息工程学院,长春 130022)

针对JPEG编码这一典型应用,结合ARM同构多核架构特点,基于JFIF数据交换格式语法层可并行化特点提出一种JPEG并行编码策略。实验结果表明,该方法可以显著提升JPEG编码效率,适用于大分辨率及实时性要求较高的图像压缩应用,同时为视频的并行编码提供了参考。

嵌入式平台;ARM MPcore;JPEG编码;Exynos-4412

引 言

在嵌入式平台上实现JPEG图像编码,按不同的处理芯片可大体包括: FPGA实现[1]、DSP实现[2]、ARM实现[3]。其中FPGA方案虽然速度较快,但功能单一,DSP处理器虽然具备强大数字运算能力,但对系统的控制能力远不如ARM处理器[4]。与此同时,按处理器内核数划分又可分为单核实现和多核实现。相比单核DSP与FPGA方式,采用单核ARM方案在一些实时性要求高的场合往往达不到压缩速率的要求。另外,在嵌入式多核处理器平台上实现JPEG编码算法,目前比较多的方法是采用异构多核架构,即ARM核加DSP核。

在这种结构中,ARM处理器主要负责图像数据读取、预处理以及调度,而DSP主要负责大量数据运算[5]。这种设计方式,虽然在一定程度上可以提高系统性能,但是成本高,并且没有实现真正意义上的并行处理,造成了硬件资源的极大浪费[6]。为此,本文针对ARM MPcore同构多核架构,利用JFIF数据交换格式语法规范可并行化特点,提出一种JPEG并行编码策略,以提高编码效率,满足更高的实时性要求。

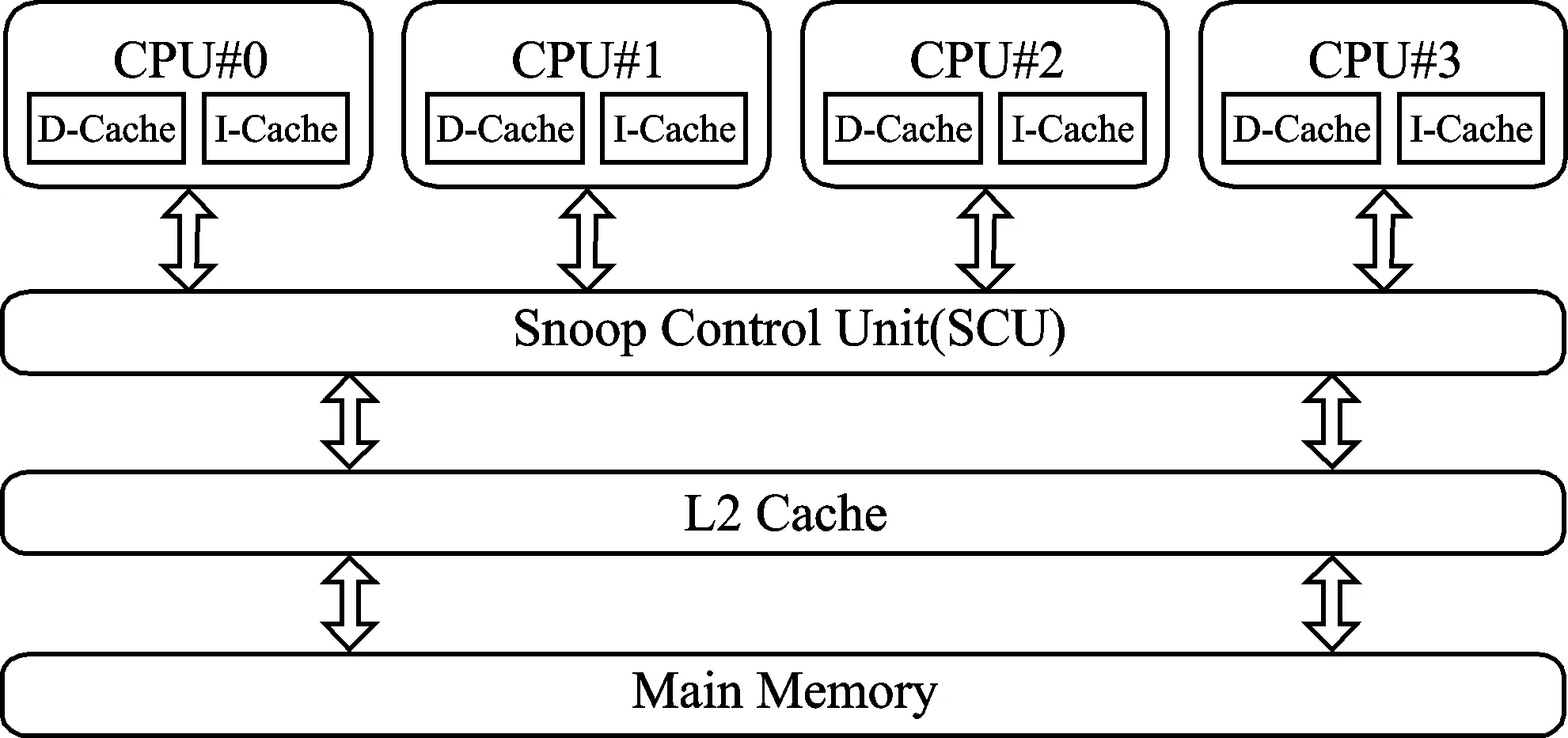

1 ARM MPcore同构多核处理器

ARM系列处理器自ARM11起引入了MPcore(Multi-Processor core)架构,随后的Cortex系列(如A8、A9、A15等)都支持该多核架构。MPcore架构作为一种典型的对称同构多核架构,每个核心都有相同大小的、私有的、由数据缓存和指令缓存构成的一级缓存(L1 Cache),同时多个处理器通过窥探控制单元(Snoop Control Unit)在一个共享的二级缓存(L2 Cache)上进行核间通信。其主要结构示意图如图1所示。

图1 ARM MPcore处理器结构示意图

由于所有处理器采用相同的硬件结构,因此其访问内存空间的权利相同,并且任意进程或线程均可以运行在不同内核上,使得程序的并行化处理成为可能[7]。

2 JPEG并行编码原理与实现

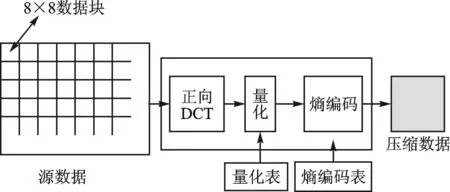

2.1JPEG压缩编码原理简介

JPEG编码标准主要用于静态连续灰度或彩色图像的压缩处理。为了适应不同应用场合要求,其编码处理有基线顺序编码DCT、累进编码、无损编码及层次编码4种操作模式[8]。对于嵌入式系统而言,在考虑运算量和资源占用的条件下,多采用最基本的基线顺序编码模式,该模式主要流程如图2所示。

图2 基于DCT编码的简化流程图

基线顺序编码过程主要由颜色空间转换及采样(图2中未给出)、正向DCT、量化、熵编码4部分组成。由于JPEG文件采用的颜色空间为YCbCr,而大多数图像采集设备及显示设备使用的为RGB颜色空间,为此在编码前需要进行颜色空间转换。同时,由于人眼对图像亮度分量(Y)的敏感度远大于色度分量(Cb/Cr),为此在进行图像压缩时,可对两种颜色分量采用不同采样因子进行采样,如每个像素点采样一个亮度分量值,而每4个像素点只取一个色度分量值,这样在提高压缩率的同时也能有效减少计算量。颜色空间转换后,将每个分量的采样值首先进行8×8分块处理,这些子数据块又称数据单元,然后再将各数据单元中的采样值减去128进行平移以作为二维FDCT(Forward Discrete Cosine Transform,正向离散余弦变换)的有效输入。

对于一个8×8数据单元,经FDCT变换后,能量主要集中在左上角几个系数中,其中(0,0)处系数称为DC系数,而其他63个系数称为AC系数。为了实现更大程度压缩,在FDCT之后,需要进行量化操作。量化是有损压缩中图像质量损失的主要原因,其主要通过对每个数据单元中的DC系数和AC系数进行不同比例的压缩,从而达到更大程度保留低频分量、消除高频分量的目的。量化后的每个数据单元中,除左上角几个系数外,大多数AC系数变为0。为了增加连续0的数目,量化后的每个数据单元中的系数需要进行Zig-Zag之字形重排,使得频率较低的系数在前,频率较高系数(大多为0)在后。随后对每个数据单元中的DC系数和AC系数分别进行DPCM(Differential Pulse Code Modulation,差分脉冲编码调制)编码及行程长度(Run Length)编码获得其中间格式,最后通过Huffman编码将这些中间格式编码成最终的JPEG码流。

2.2并行编码原理

JPEG压缩标准中给出了3种压缩的数据格式:交换格式(JFIF)、图像数据缩略格式、表规范缩略格式。为了不失一般性,本文仅讨论交换格式。标准的JFIF数据交换格式通常为参数、标记以及熵编码后的数据段按一定次序组成的集合,其语法格式如图3所示。

图3 JFIF数据交换格式图

由图3可知,JFIF压缩数据格式以一个SOI(Start Of Image)标记开始,包含一个帧(Frame),并以一个EOI(End Of Image)标记表示结束。其中一个帧由表指标数据、帧头(Frame header)及若干扫描段(对于基线顺序编码模式,有且仅有一个扫描段)组成。而每个扫描段又由表指标数据、扫描头(Scan header)、熵编码段(ECS)、重启标记(RST)组成。而熵编码段则由若干个经熵编码后获得的最小编码单元(MCU)的顺序序列组成。所谓最小编码单元,则根据采样因子的不同,由若干个数据单元组成。综上可知,JFIF是一种嵌套的数据格式。

需要指出的是,扫描段中的重启标记RST必须与定义的重启间隔(DRI)标记段(图中属于misc段)成对出现。也就是说,若JFIF格式中不存在DRI标记段,则Scan中的ECS段是连续的(未插入RSTm);若JFIF格式中存在DRI标记段,则需要在Scan中除最后一个ECS段外,每隔一定数目的MCU需要插入RSTm标记。MCU重启间隔的数目在DRI标记段中定义,而RSTm标记中m的值在0~7 之间进行周期循环。如2.1节所述,基线顺序编码模式是以数据单元为单位依次进行FDCT、量化、Zig-Zag排序、DC系数差分预测编码、AC系数行程长度编码、中间格式Huffman编码。其中由于DC系数采用的是差分预测编码,所以对同一个颜色分量来说,除首个数据单元外,后一个数据单元中编码的DC系数实际上是该DC系数与前一个数据单元中DC系数的差值。而DRI标记段的作用就是定义每隔多少个MCU重新定义新的“首个数据单元”,并在最后一个MCU右边插入一个RSTm,以便解码时知道在该处之后需要重新进行差分解码。

为此,在对图像进行编码时,可将图像数据进行按行或按列分割成若干份进行并行编码,再将各编码为JFIF格式的子图的公共数据部分及熵编码段数据提取,并在两子图熵编码段间插入RST重启标记,最后添加DRI标记段并修改各标记段中一些参数信息,即可获得一张完整的符合JFIF语法规范的编码图像。这种间隔重启功能摆脱了各子图数据间的耦合性,不仅编码后的图像可被标准解码器解码,同时由于JFIF格式中采用由一个X’FF字节与一个非0或X’FF字节组成的2字节代码来表示各个标记,为此在合并提取公共数据或熵编码段数据时,无需进行解码操作,只需找到相应标记,便可直接进行数据提取操作。这些查找、提取操作花费的时间远远小于编码时间,故采用分割-融合的方式在多核架构平台上进行并行编码以大大提高编码速度。

还有观点认为侵犯的客体是公司、企业人员职务行为的廉洁性。笔者认为该观点不可取。商业贿赂犯罪应当区别于国家工作人员贿赂犯罪。考虑到市场经济活动中竞争的特性,还考虑到经营者所从事活动的非公务性,从这两点出发,因此我们不应对普通公司、企业的人员提出较为苛刻的要求,要求其职务行为的廉洁性。

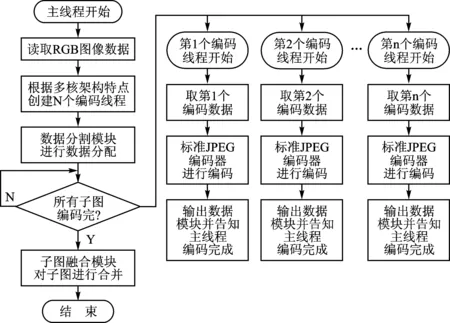

2.3并行编码实现

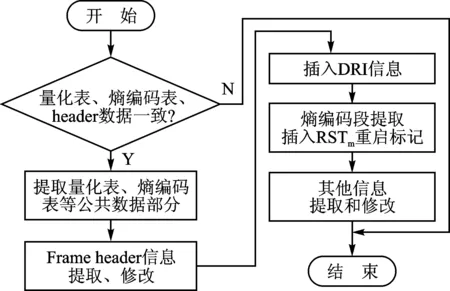

根据以上分析,本文提出一种分割-融合的并行编码策略,其流程图如图4所示。

图4 并行编码方案流程图

算法首先读取RGB图像数据,并创建n个编码子线程,随后在数据分割模块中按列将图像数据分割成n份,并按序分配给各子线程进行并行编码。其中,子线程编码的标准JPEG编码器,本文将第三方开源JPEG编码库libjpeg-turbo-1.4.1移植到嵌入式平台上,通过调用其库函数进行编码。libjpeg-turbo作为高度优化的开源图像编解码库,相比传统的libjpeg库针对ARM Cortex架构做了进一步优化,可获得更快的图像编解码速度。当各子线程编码结束后便告知主线程通过子图合并模块将各子图进行融合,最终获得一张完整、符合JFIF语法规范的编码图。其中子图融合模块是算法实现的关键部分,其流程图如图5所示。

图5 子图融合流程图

模块首先检测输入子图的量化表、熵编码表、帧头中的信息,以确保各子图编码时采用的量化表及Huffman编码表等参数一致;完成检测后,需要提取各个子图的公共信息,例如量化表、熵编码表、各标记段中某些特定信息(如长度、采样精度、水平采样因子、垂直采样因子等)。此外,由于帧头中记录了图像的尺寸信息,因此在进行融合时需要对其进行修改,同时在帧内还需插入DRI标记段并计算MCU重启间隔的数目;最后,提取各子图熵编码ECS信息并插入RST重启标记,合成一张符合JFIF数据交换格式规范的JPEG图像。其中DRI标记段中MCU重启间隔数目计算规则如下:假设各子图的尺寸大小一致,且宽高分别为w和h,此时各子图的 MCU个数相同且与图像各颜色分量水平和垂直采样因子有关,设3个颜色分量的水平和垂直采样因子的最大值分别为Hmax和Vmax。此时重启间隔数目Ri计算公式如下:

由于libjpeg-turbo默认的采样方式为4∶2∶2,即最大水平和垂直采样因子均为2,此时

Ri=w×h/256

3 并行编码性能分析

本文采用迅为iTop-4412嵌入式开发平台。该平台采用Samsung Exynos-4412多核处理器,拥有对称的4核ARM Cortex-A9 MPcore架构,各内核拥有32 KB一级缓存同时共享1 MB二级缓存。嵌入式平台采用Ubuntu12.04操作系统,交叉工具链为arm-none-linux-gnueabi-4.4.1。

3.2性能测试

本文采用计算并行度的方式来评价并行编码的优化性能,其表达式如下所示:

mp=Tp/T1×100%

其中,T1表示算法在串行运行下的时间,Tp表示算法在并行运行下的时间。并行度越小,说明算法并行度越高。

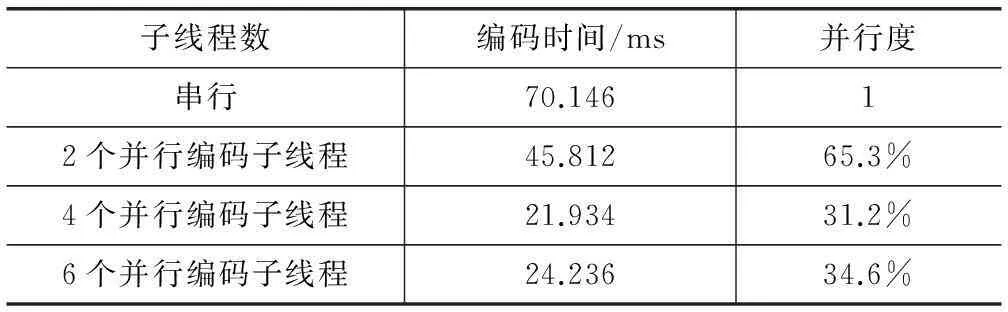

对一幅分辨率为1280×720的24位RGB彩色图像,分别采用串行、2个并行编码子线程、4个并行编码子线程及6个并行编码子线程进行编码测试,其中libjpeg-turbo图像质量因子为80,其结果如表1所列。

表1 不同并行编码子线程数对应编码时间表

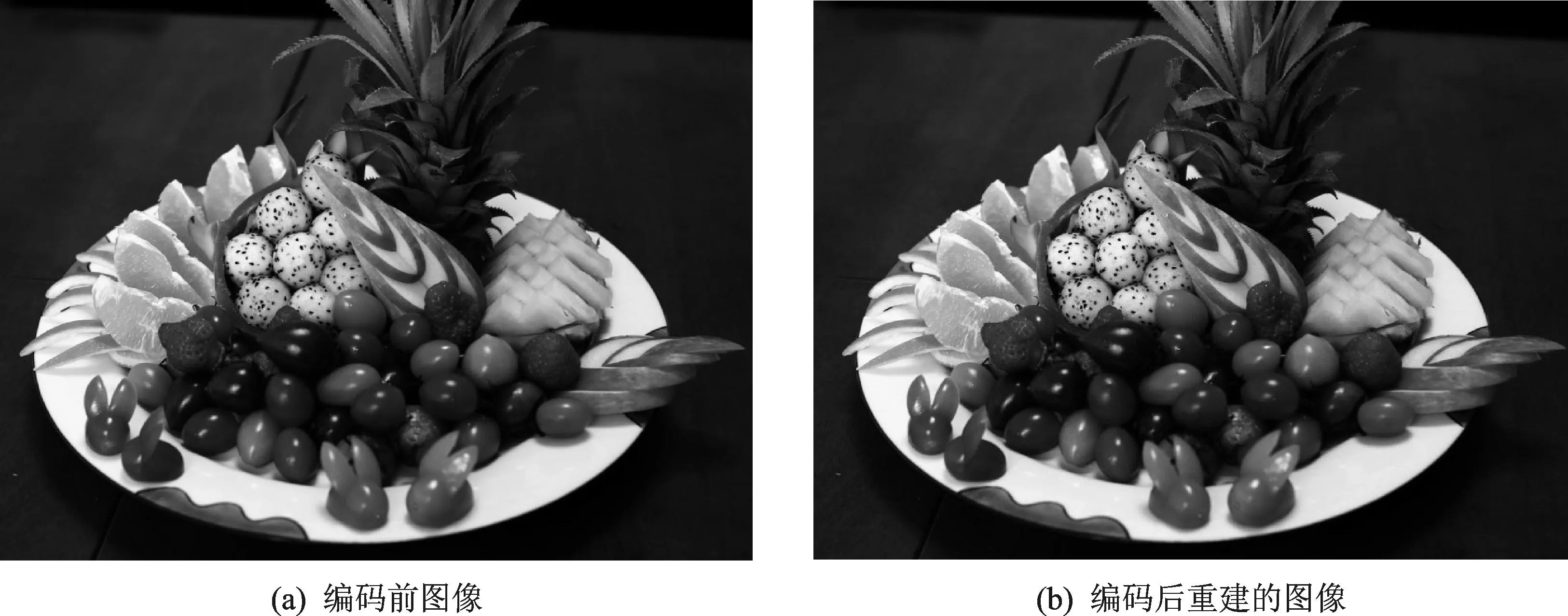

从表1中可以看出,当编码子线程数小于等于4时,并行度分别为65.3%和31.2%,高于理论上的50%和25%。这是由于操作系统对线程的调度及线程间通信以及子图融合模块需要耗费一定时间。同时,虽然理论上并行编码子线程数目越大越好,但由于实际物理核心数为4,当线程数过多时,各线程会对处理器产生竞争关系,导致编码效率降低。编码前后的图片对比如图6所示,两者在视觉上变化不大。

图6 编码前后图片重建后对比图

结 语

通过对ARM MPcore多核处理器硬件架构分析,针对JPEG编码提出一种并行优化策略,操作简便,具有良好的通用性。

本文以4核ARM Cortex-A9 MPcore(Exynos-4412)处理器为实验平台,结合libjpeg-turbo开源编解码库,对一张720P的24位彩色RGB图片进行编码并行度测试,结果表明并行编码策略具有良好的并行度。同时,当并行编码线程数小于物理核心数时,编码速率与并行线程数成正比;而当并行线程数超过物理核心数时,由于过多线程的竞争会导致编码性能降低。

总而言之,多媒体技术一直是嵌入式平台关键技术之一,如何充分发挥嵌入式多核处理器的并行性能,实现程序并行化处理是值得研究的重要方向。

[1] 徐洁.基于FPGA的JPEG图像压缩系统的实现[D].大连:大连理工大学,2013.

[2] 马亮.基于DSP的JPEG视频压缩系统的实现[J].电子设计工程,2009,16(9):82-85.

[3] 张长春,杨浩.基于ARM的JPEG编码器设计与实现[J].微计算机信息,2010(11):99-101.

[4] 王战盟.基于ARM的嵌入式静态图像显示系统的研究与实现[D].广州:广东工业大学,2007.

[5] 程志.基于Omap5910嵌入式平台的并行JPEG压缩算法[J].计算机工程与设计,2008,29(16):4124-4125.

[6] 张琦.多核系统中的程序性能优化研究[D].合肥:中国科学技术大学,2010.

[7] 杨川,杨斌.嵌入式ARM多核处理器并行化方法的研究[J].单片机与嵌入式系统应用,2014(7):9-12.

[8] William B Pennebaker,Joan L Mitchell.JPEG:Still Image Data Compression Standard[M].London:Chapman&Hall,1993.

Research on JPEG Parallel Encoding of Embedded ARM MPcore Platform

Liao Xingyu,Yu Shuilai

(School of Electronic and Information Technology,Changchun University of Science and Technology,Changchun 130022,China)

In this paper,aiming at the typical application of JPEG encoding,a parallel encoding strategy based on JFIF data interchange format syntax combined with the characteristics of the ARM MPcore structure is proposed.The experiment results show that the proposed method can significantly improve the efficiency of JPEG encoding,which is suitable for the high resolution and real-time requirements of image compression applications.It provides a certain reference for the video parallel encoding.

embedded platform;ARM MPcore;JPEG encoding;Exynos-4412

TP311.1

A

(责任编辑:薛士然2015-10-26)