FPGA的eMMC嵌入式阵列存储系统设

2016-08-31周珍龙顾彤王红兵

周珍龙,顾彤,王红兵

(西安电子科技大学 电子信息攻防对抗与仿真技术重点实验室,西安 710071)

周珍龙,顾彤,王红兵

(西安电子科技大学 电子信息攻防对抗与仿真技术重点实验室,西安 710071)

本文实现了一种嵌入式阵列存储系统,以具有体积优势、性能优势以及价格优势的eMMC嵌入式多媒体卡为存储介质,基于FPGA使用硬件逻辑实现读写控制器,并给出软件仿真以及硬件测试结果。同时控制8片存储芯片扩展容量,在速度提高方面使用了GTX高速收发器。和单片存储系统对比,本设计系统具有海量存储、高速读写等特点。

FPGA;eMMC;GTX高速收发器;阵列存储系统;读写控制器

引 言

eMMC(Embedded Multi-Media Card)是嵌入式多媒体卡的简称[1]。当前,移动终端,尤其是手机,平板以及军用控制器等手持设备,对存储系统都要求高速以及海量,并且一个重要条件是体积小。设计基于FPGA的eMMC控制器有以下几个优点:体积小,对便携性要求严格的移动终端有很好的支持力,接口速度达到50 MB,符合便携设备对访问速度的要求,满足大容量系统的需求;控制器采用FPGA硬件逻辑实现,提高系统兼容性。

1 eMMC阵列系统总体方案

该阵列系统主要在Xilinx公司的Virtex 6系列FPGA芯片XC6VLX240中实现控制器模块,生成各级FIFO,以及为控制器、FIFO、eMMC芯片提供各种需求的时钟电路。同时,该阵列系统使用GTX收发器作为数据传输的工具,使得系统具备高传输速率的特点。

本文选择Micron的eMMC芯片,芯片型号为MTFC64GJV DN-4M IT,该芯片遵循JEDEC标准协议5.0。由于当前eMMC芯片的存储容量有限,大容量系统必须使用多个eMMC来达到要求,这里选择8片eMMC芯片,每片eMMC芯片的存储容量为64 GB。对所有芯片的读取方式有并行和串行两种。如果采用串行的存储方式,对芯片一块一块地存储,势必对读写速度有很大限制,因此本文采用并行的方式,对存储芯片的数据位宽扩展,同时对8片eMMC芯片读写,数据并行位宽由单片8位扩展为8×8位的宽度。

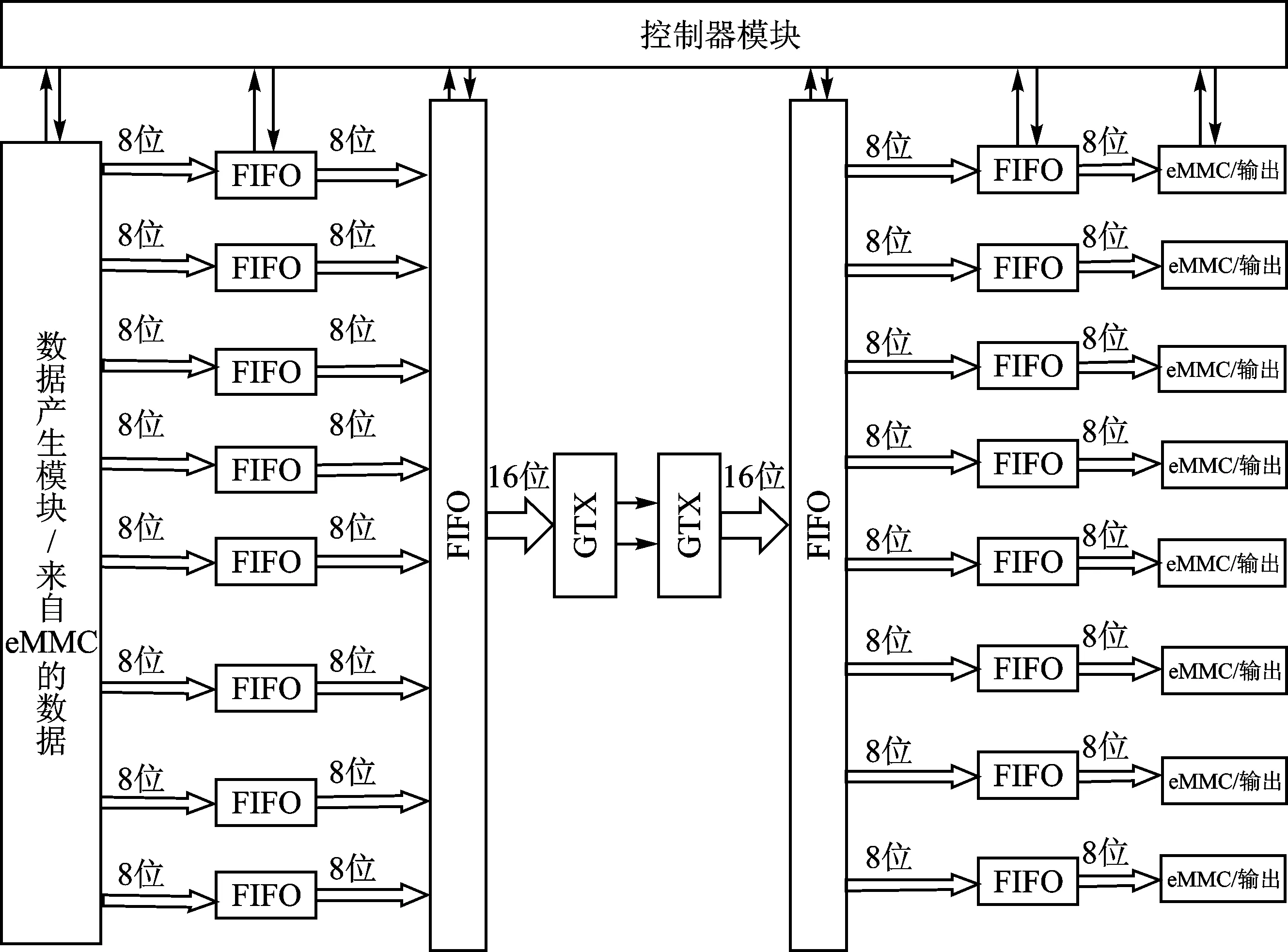

该阵列系统的总体框图如图1所示,包括读和写两个过程。

图1 系统总体框图

其中,控制器模块负责对eMMC芯片、GTX、各级FIFO上电复位,负责整个系统工作期间的协调工作。本文需要实现对eMMC的读和写的功能。图1中,写过程时,左侧发送端为数据产生模块,右侧接收端为eMMC;读过程时,左侧发送端为来自eMMC的数据,而右侧输出端则是将读取自eMMC芯片的数据传输给最终申请数据访问的模块。整个系统对外部体现为接口,体现嵌入式FPGA的可移植性。

2 各模块介绍

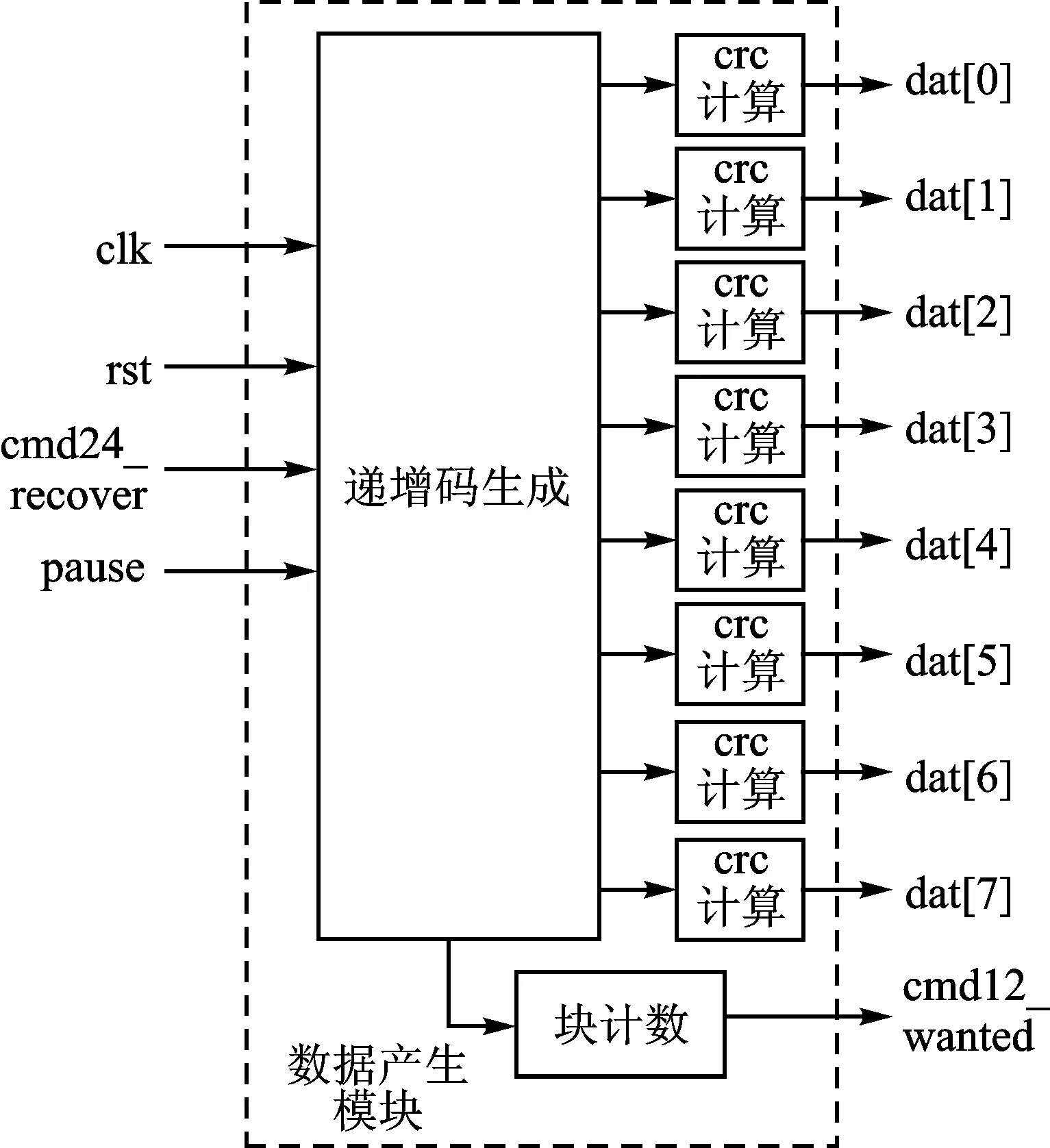

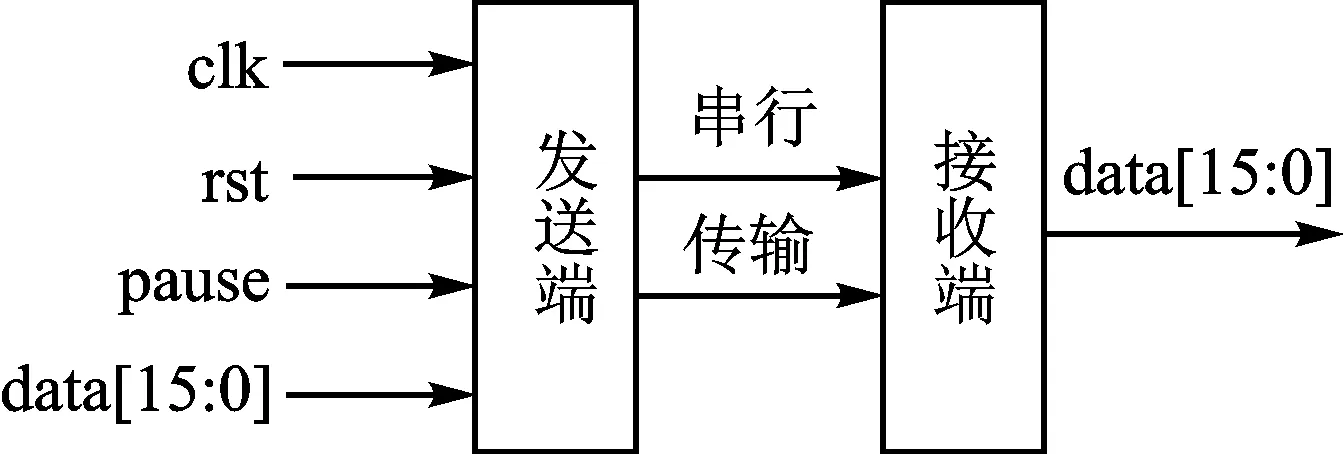

2.1数据产生模块

数据产生模块在数据写过程中不可缺少[2]。本设计方案针对数据存储,选择块长为512字节的数据存储方案。故数据产生模块每次产生的数据为512字节。这里选择常用递增码作为数据源,由于eMMC的数据总线为8位,因此需要两轮00~FF的递增码才能达到512字节的要求。数据产生模块如图2所示。

图2 数据产生模块

其中,cmd24_recover为控制器模块在发送所有的写命令之后发出的命令信号。cmd12_wanted为写指定块数据(每块为512字节)之后反馈给控制器模块的信号,该信号通知控制器模块停止对eMMC的写过程。

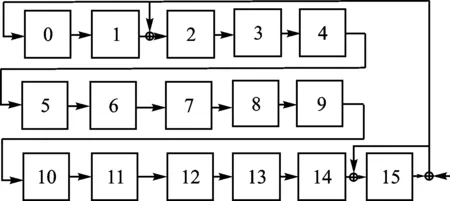

CRC即循环冗余校验码(Cycle Redundancy Check), CRC校验码为16位,生成多项式为17位。数据流左移16位,再除以生成多项式,做不借位的除法运算(相当于按位异或),所得的余数就是CRC校验码。CRC16计算框图[4]如图3所示。

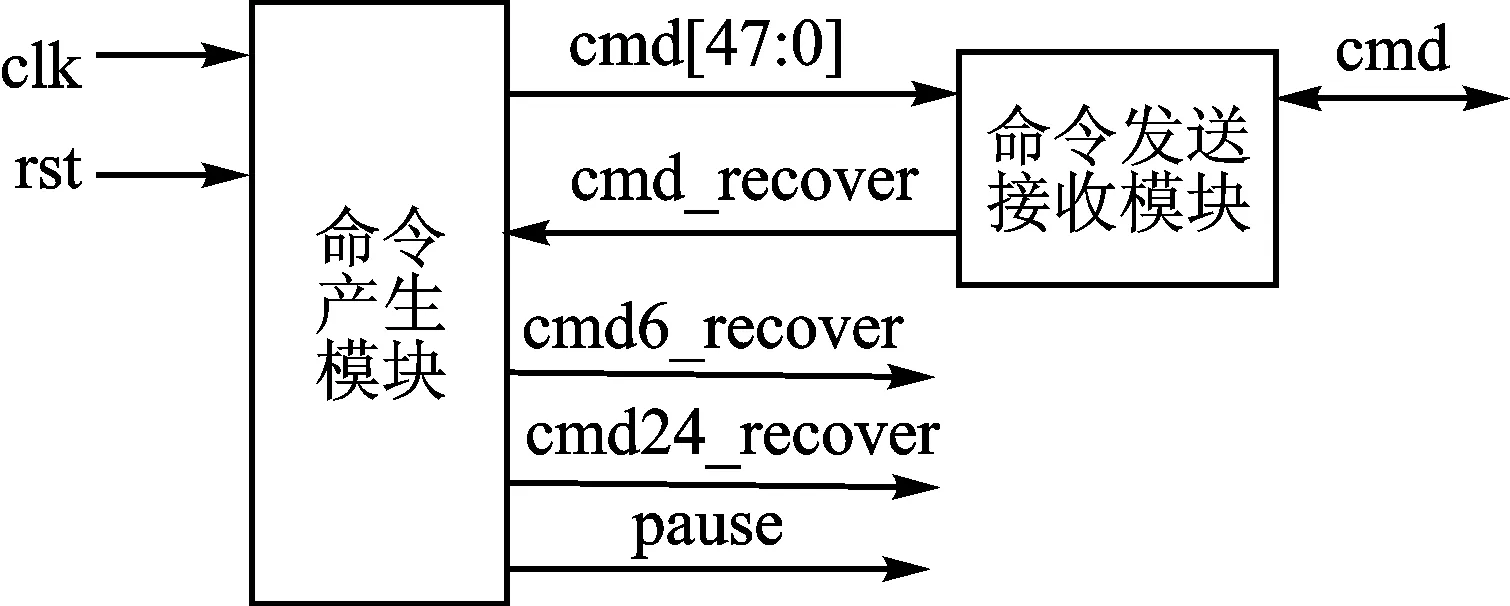

2.2控制器模块

控制器模块不仅需要完成对eMMC的命令发送和命令接收任务,实现eMMC的控制器设计,而且需要实现对各个模块之间数据流动的控制。

命令发送和接收的实现,完全遵照JEDEC标准5.0的设备协议。这里介绍主要的读写命令发送顺序[5]:读命令发送为CMD0、CMD1、CMD2、CMD3、CMD9、CMD7、CMD8、CMD6、CMD6、CMD16、CMD23、CMD18;写命令发送为CMD0、CMD1、CMD2、CMD3、CMD9、CMD7、CMD8、CMD6、CMD6、CMD16、CMD25、CMD12。

图3 CRC16计算框图

由于在eMMC写过程中,芯片有一个编程过程,将数据写入存储逻辑,在该过程中数据的发送必须暂停,因此,整个系统的数据流动应该予以暂停,该过程由控制器模块生成pause信号完成。数据读写过程中,需要时刻发送cmd13命令查询eMMC芯片的工作状态,写过程中尤其重要,其响应指示需要判断产生。控制器模块具体实现方案如图4所示。

图4 控制器模块实现方案

cmd24_recover代表的是上文提到的所有读写命令均发送完毕之后,写过程中通知数据产生模块产生递增码,读过程中通知小FIFO开始接收来自eMMC芯片的数据。pause命令,是在读写过程中,由于芯片需要编程而对整个传输通道暂停的控制命令,该信号传送给其他所有模块。cmd6_recover,在控制器发送完cmd6命令并接收回应之后,通知时钟模块由低速时钟切换到高速时钟。

2.3GTX模块

引入GTX模块主要是针对数据传输速率。eMMC的工作时钟在128 kHz~52 MHz,如果使用阵列存储,使用8片eMMC芯片,要达到50 MHz的要求,每个时钟传输一个位宽的数据,将需要8×8×50 Mbps的传输速率,GTX接收,发送端采用串行通信,其数据端使用16位位宽,传输频率为150 MHz,因此,可以达到16×150 Mbps的传输速率要求,满足eMMC阵列系统对速率的要求。

对于GTX的工作原理,这里只做简单介绍。GTX有收发端,二者通过串行线连接[6],对于系统内的其他模块,主要表现为数据位宽为16位的数据端口,如图5所示。

图5 GTX收发模块

发送端的data连接在发送端的大FIFO,接收端的data连接在接收端的大FIFO。这里需要注意的是,当pause激活时,GTX收发器之间并没有停止数据传输,而是在data线上一直发送43BC码,并且将标识信号charisk_i设置为00。

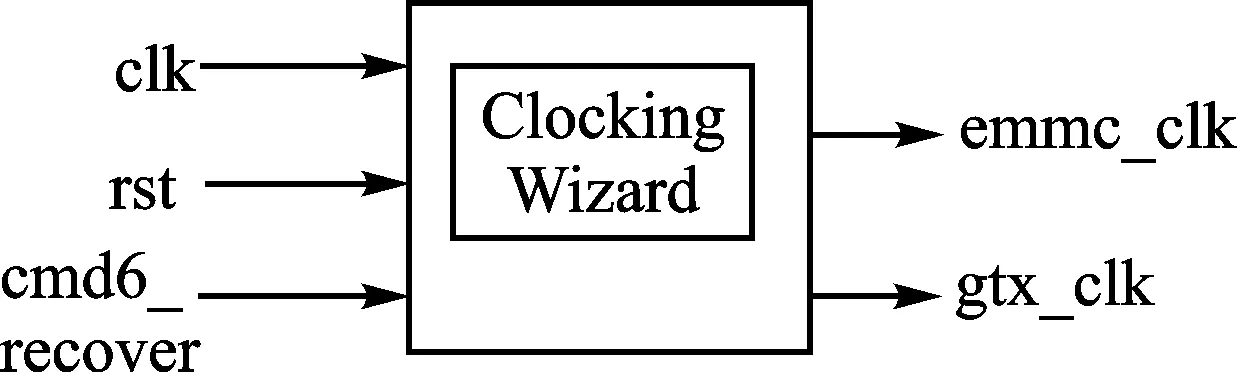

2.4时钟切换模块

时钟源采用FPGA开发板上提供的50 MHz时钟,然后使用ISE自带的Clocking Wizard IP核,定制输出为50 MHz、250 kHz以及150 MHz时钟。该模块接收来自控制模块的cmd6_recover命令,为eMMC芯片提供时钟电路的信号emmc_clk由初始的250 kHz时钟切换到50 MHz,为GTX提供时钟的信号gtx_clk维持150 MHz不变。图6为时钟切换模块的结构框图[7]。

图6 时钟切换模块

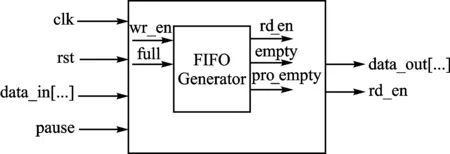

2.5各级FIFO协调工作

FIFO的配置上,读过程和写过程大致是一样的。本文所有FIFO使用ISE自带IP核FIFO Generator工具生成[8],需要注意的是,应该将FIFO的默认值设置为FF。可以将各级FIFO按照顺序分为:第1级FIFO位宽为8进8出;第2级FIFO,位宽为64位进16位出,将数据发送给GTX;第3级FIFO位宽为16位进64位出,接收从GTX发送过来的数据;第四级位宽为8位进8位出。可以从图1中清楚看到各级FIFO分配。整个FIFO系统以GTX分开为左右镜像。各级FIFO模板见图7,这里给出用该模板设计的第1级FIFO在ISE开发工具中的RTL图。

图7 各级FIFO模块

8个第1级FIFO采用逻辑复制,使用ISE自带的FIFO核定制主要模块,外加控制电路设计而成。检测到data[7∶0]为00时(依据eMMC协议,00为数据包的起始位),使能FIFO写,将数据存入FIFO,在pro_empty不为空时,使能rd_en,如果empty不为空,则一直使能rd_en,该信号作为下一级FIFO的写使能。下一级FIFO的读写使能方案同该级FIFO设计。各级FIFO不同的地方在于输入和输出的位宽不同。

3 软硬件验证

3.1ISim软件仿真

ISim软件验证可以缩短系统开发的时间[9],能够直观地显示出设计中存在的问题,因此前期使用ISim软件调试。

(1) crc16模块验证

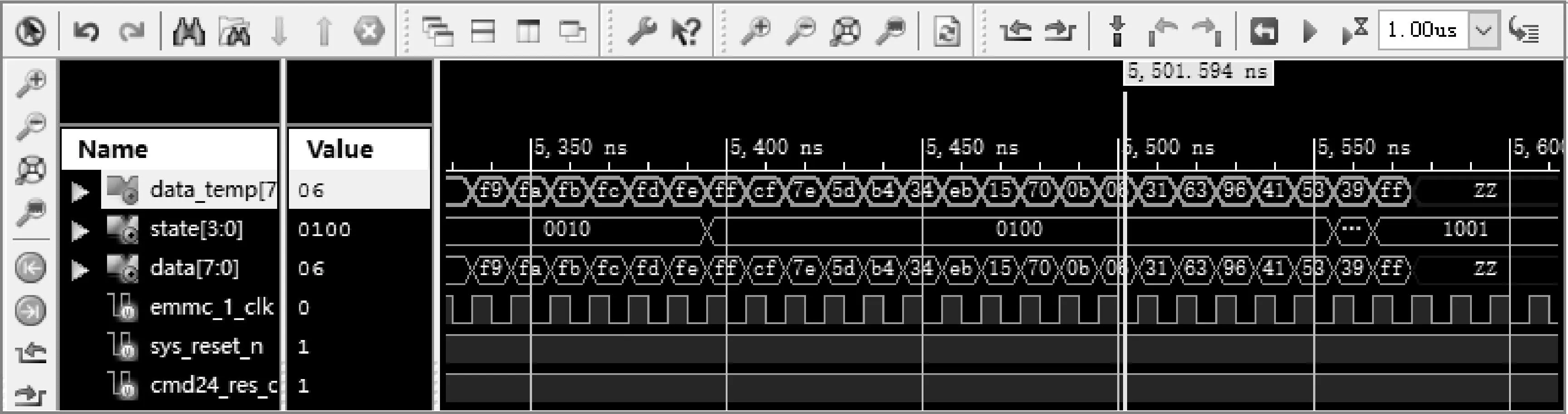

图8为512的数据包(起始位00+00~FF+00~FF)的crc16计算结果,data最后为结束位FF。

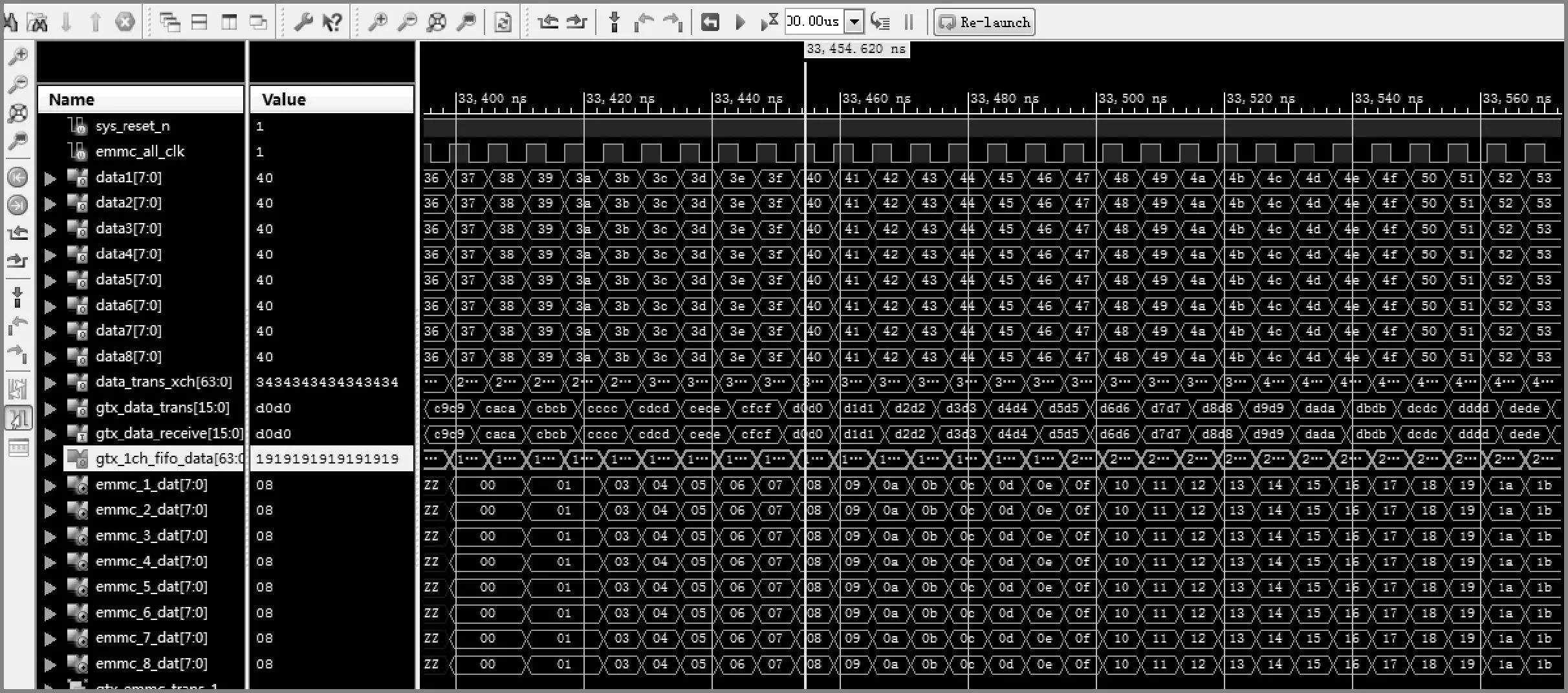

(2) 各级FIFO验证

从第1级FIFO到第4级FIFO,data1~8为第1级FIFO输入,data_trans_xch为第1级FIFO输出拼凑而成的第2级FIFO输入,gtx_data_trans[15∶0]为第3级FIFO输入,gtx_1ch_fifo_data[63∶0]为第3级FIFO输出,emmc_1_dat~emmc_8_dat为第4级FIFO输出,如图9所示。

3.2ChipScope在线调试硬件验证

系统总体验证:最后使用Xilinx的Virtex 6系列FPGA芯片以及Micron的eMMC存储芯片,对设计的阵列存储系统的读写功能进行验证。

写数据验证略——编者注。来自emmc_1_dat~emmc_8_dat数据线上的最低位输出了确认信号0010,表示写入的数据成功,对8片eMMC的写数据操作正常。

图8 crc16模块验证

图9 各级FIFO验证

读数据验证略——编者注。从读出的第13个512字节的数据开始,系统继续从eMMC存储芯片中读取上述写功能写入的数据。

结 语

本文解决单片eMMC对速度以及带宽的限制,使用了GTX以及FPGA硬件逻辑设计满足阵列存储系统的要求。逻辑设计之后通过ISim软件仿真验证了电路的可行性,并且随后将工程生成的二进制文件烧写到FPGA开发板中,实现了硬件级的eMMC阵列存储,通过在线调试工具ChipScope验证读写数据全部正常。该系统在Vintex 6系列FPGA上实现读写功能,并可通过定制GTX核轻松移植到其他包含GTX硬核的FPGA上。本文的系统也有值得改进的地方,比如可以使用更高速的GTH传输数据控制更多的eMMC芯片等。

编者注:本文为期刊缩略版,全文见本刊网站www.mesnet.com.cn。

[1] EMBEDDED MULTI-MEDIA CARD (e•MMC), ELEC TRICAL STANDARD (5.0 Device)[EB/OL].[2015-10]. http://www.jedec.org/sites/default/files/docs/JESD84-B50.pdf.

[2] 周杰,郝立燕.基于FPGA的eMMC控制器及其工作方法:中国,10264666.3[P].2013-09-04.

[3] Tongsheng Zhang, Qun Ding.Design and Implementation of CRC Based on FPGA[EB/OL].[2015-10] http://xueshu.baidu.com/s?wd=paperuri:(7e1382efd173772268d2e 58aa965393c)&filter=sc_long_sign&sc_ks_para=q%3DDesign+and+Implementation+of+CRC+Based+on+FPGA&tn=SE_baiduxueshu_c1gjeupa&ie=utf-8.

[4] 叶懋,刘宇红,刘桥.CRC码的FPGA实现[J].重庆工学院学报:自然科学版,2007,21(3).

[5] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

[6] Xilinx.Xilinx Virtex-6 FPGA GTX Transceivers User Guide,2011.

[7] 罗莉,何鸿军,徐炜遐,等.面向SOC芯片的跨时钟域时钟设计和验证[J].计算机科学,2011,9(9).

[8] 徐光辉,程东旭.基于FPGA的嵌入式开发与应用 [M].北京:电子工业出版社,2006.

[9] 王传新.FPGA设计基础[M].北京:高等教育出版社,2007.

周珍龙(硕士),主要研究方向为基于FPGA的高速数据存储与传输;顾彤(硕士),主要研究方向为图像融合及存储;王红兵(硕士),主要研究方向为基于FPGA的A/D采样及存储。

31Communications Interface(SCI) Reference Guide,2009.

[4] Texas Instrument.TRSF3221E 3-V TO 5.5-V SINGLE-CHANNEL RS-232 1-Mbit/s LINE DRIVER/RECEVIER WITH ±15-Kv IEC ESD PROTECTION,2007.

[5] 陈杰.MATLAB宝典[M].北京:电子工业出版社, 2011.

陈宝欣、陈林军(硕士研究生),主要研究方向为检测技术与自动化装置;沈艳林(博士),主要研究方向为数字信号处理;刘鹏(讲师),主要研究方向为嵌入式控制系统;姜智译(助理工程师),主要从事油库自动化工作。

(责任编辑:杨迪娜收稿日期:2015-12-09)

Zhou Zhenlong,Gu Tong,Wang Hongbing

(Key Lab. of Electronic Information Countermeasure and Simulation,Xidian University,Xi’an 710071,China)

In the paper,an embedded array storage system is proposed.The design uses eMMC embedded multimedia card as the storage medium which has the advantages of volume,performance and price,and it uses the hardware logic based on FPGA to implement the read and write controller.The software simulation and hardware testing are given in the paper.Eight memory chips are used to extend the capacity,and the GTX high-speed transceiver is used to improve the speed.Compared with the single chip storage system,the design has the characteristics of mass storage,high-speed reading and writing.

FPGA;eMMC;GTX high-speed transceiver;array storage system;read and write controller

TP273

A

(责任编辑:杨迪娜2015-10-16)