基于FPGA与ML7204的音频编解码设计*

2016-08-10吴伟张禹

吴 伟 张 禹

(中国电子科技集团公司第二十八研究所 南京 210002)

基于FPGA与ML7204的音频编解码设计*

吴伟张禹

(中国电子科技集团公司第二十八研究所南京210002)

摘要通信系统中的语音编解码多基于DSP来实现,采用相应的DSP硬件设计及软件算法,可以较方便地实现多路语音处理。而在某些小型的G.729格式的通信系统中,采用硬件编解码的模式,结合FPGA来协同设计,可以将语音编解码更为方便地应用在通信系统的终端设备中,大大减少了设备设计的复杂度。

关键词编解码; G.729; 音频处理; PCM

Class NumberTN95

1引言

在通信系统中,需要将通信双方的模拟信号通过数字化方式进行传输、交换,然后送达对方再将数字信号转换为模拟信号。在这一过程中,由于系统带宽的限制,需要对数字化以后的信号进行编码,以减少带宽的占用,在语音通信系统中,常采用G.729的编解码方式。在部分产品的开发设计中,利用ML7204硬件编解码器(code and decode, CODEC)配合现场可编程门阵列(Field-Programmable Gate Array, FPGA)设计,实现了实时与可靠的数据传输,充分控制了研发风险,有效降低了设计成本,缩短了产品开发周期。

2ML7204简介

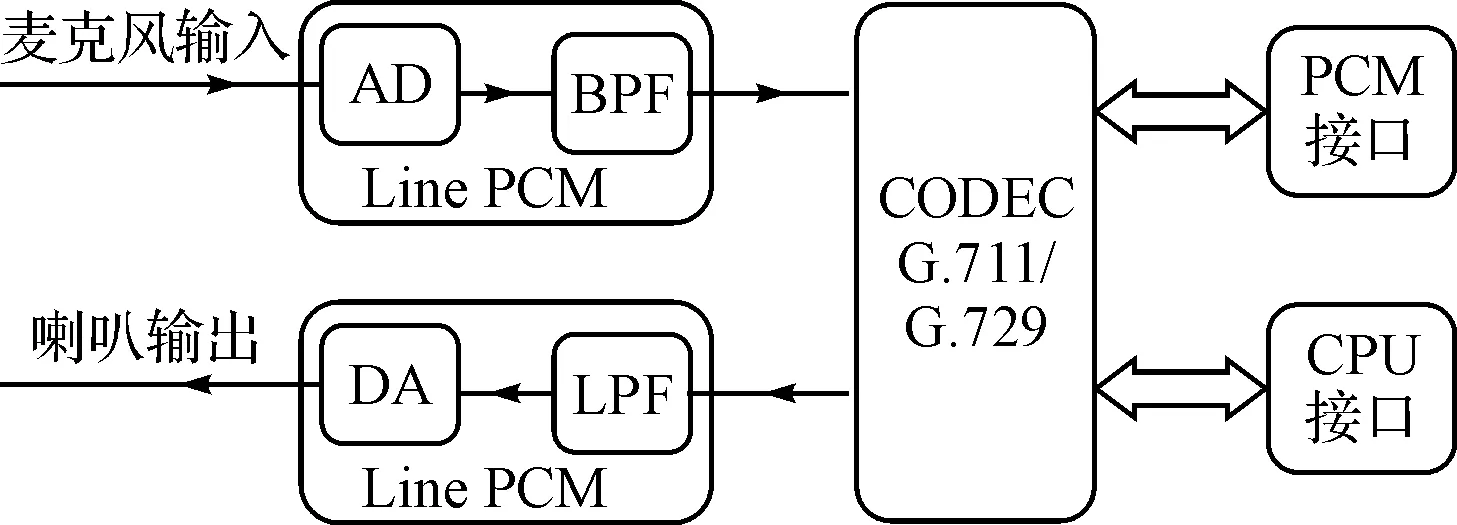

ML7204是OKI公司基于网络电话(Voice over Internet Protocol,VoIP)的场景应用开发的一款面向中小型系统的模块,芯片支持双路G.711-A/μ的编解码或者单路G.729-A编解码。其内部信号处理的流程如下:模拟音频信号通过模拟数字转换器(Analog to Digital,AD)进入CODEC,由数字带通滤波器处理后生成16bits线性脉冲编码调制(Pulse Code Modulation,PCM),进入语音编码模块进行G.711&G.729编码,然后在接收Buffer中缓存生成的数字语音包;从上级接口进入发送Buffer的数字语音包,送达语音解码模块进行G.711&G.729解码,然后通过数字低通滤波器,通过数字模拟转换器(Digital to Analog,DA)还原为模拟信号。信号处理流程如图 1所示。

另外,ML7204还提供了许多面向语音业务的附加功能,包括回声抑制,频移键控(Frequency-Shift Keying,FSK)、双音多频(Dual Tone Multi-Frequency,DTMF)和话音(TONE)的生成与检测等。

图1 CODEC内部处理流程框图

3硬件系统设计

硬件系统的设计采用了FPGA做处理芯片来完成ML7204的初始化配置及后续的数据收发等工作。

ML7204的控制接口为通用异步总线接口,可由中央处理器(Central Processing Unit,CPU)或者其他控制器进行访问。一般通过地址映射的方式,将CODEC内部寄存器交由控制器读写控制,从而将系统需要的模式、 功能一一配置, 完成相关功能,同时收发语音数据。也可采用PCM接口来收发语音数据,以方便和多通道缓冲串行接口(Multi-channel Buffering Serial Port,McBSP)等上级接口互联。

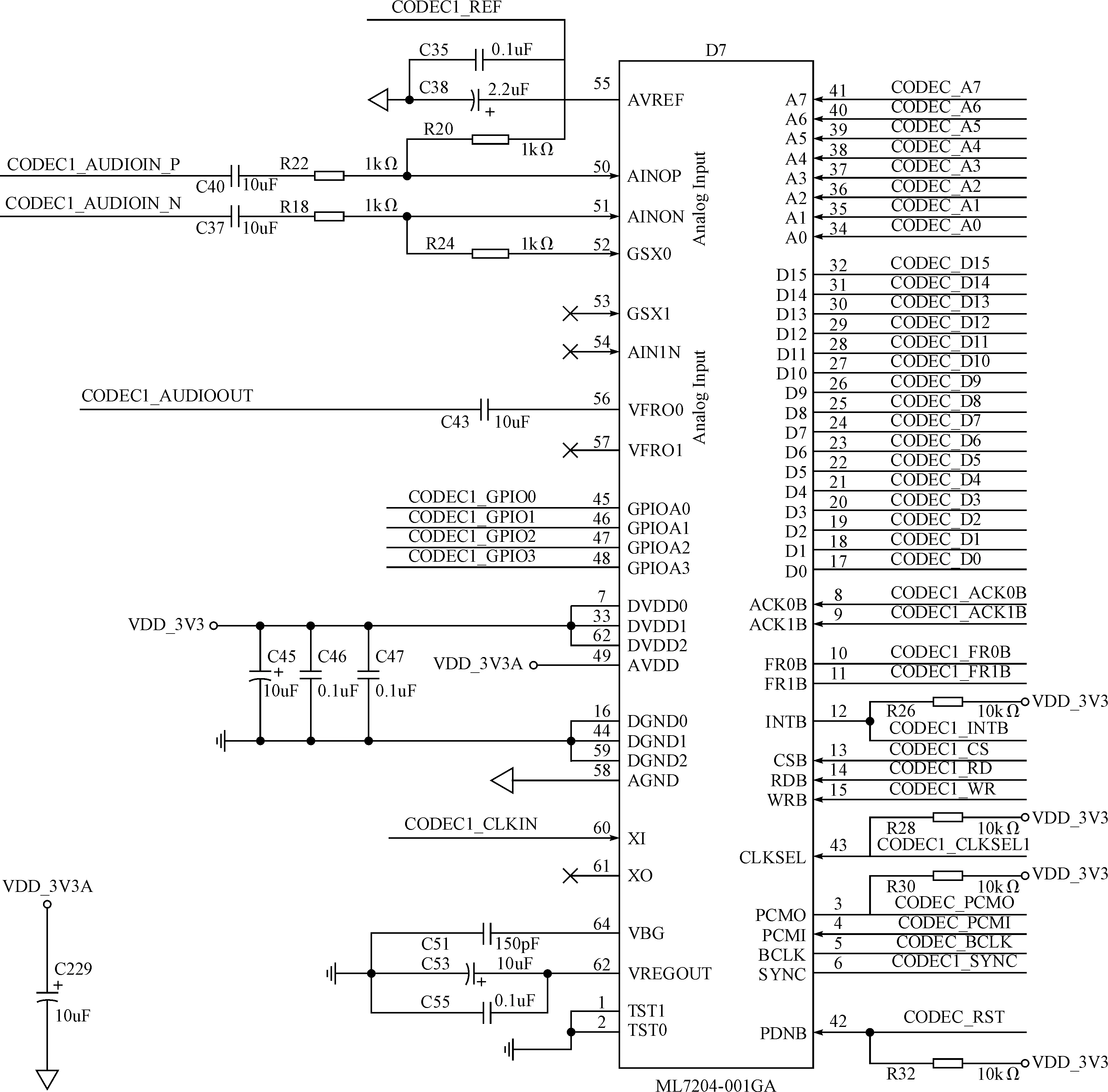

硬件设计上,模拟与数字部分的电源、地线是分离的。在模拟部分,语音输入信号为差分信号,通过10uF电容进行交流耦合,并采用模拟信号的地线引脚AVREF和1kΩ电阻网络对信号进行整流,以提高其信噪比。音频信号输出为单端信号,也采用10uF电容隔断直流分量;数字信号部分,根据硬件管脚的定义,先进行工作模式硬件配置,然后将异步总线的16位数据、8位地址及控制线,PCM接口的信号线等连接至FPGA的输入输出(Input and Output,IO)管脚,完成FPGA与CODEC的硬件互联。ML7204的硬件设计如图2所示。

图2 ML7204硬件原理图设计

4软件系统设计

为完成底层模拟信号与上层数字信号的转换,通过Verilog硬件描述语言设计FPGA程序来实现对ML7204的控制,其中FPGA为主机,ML7204为从机。

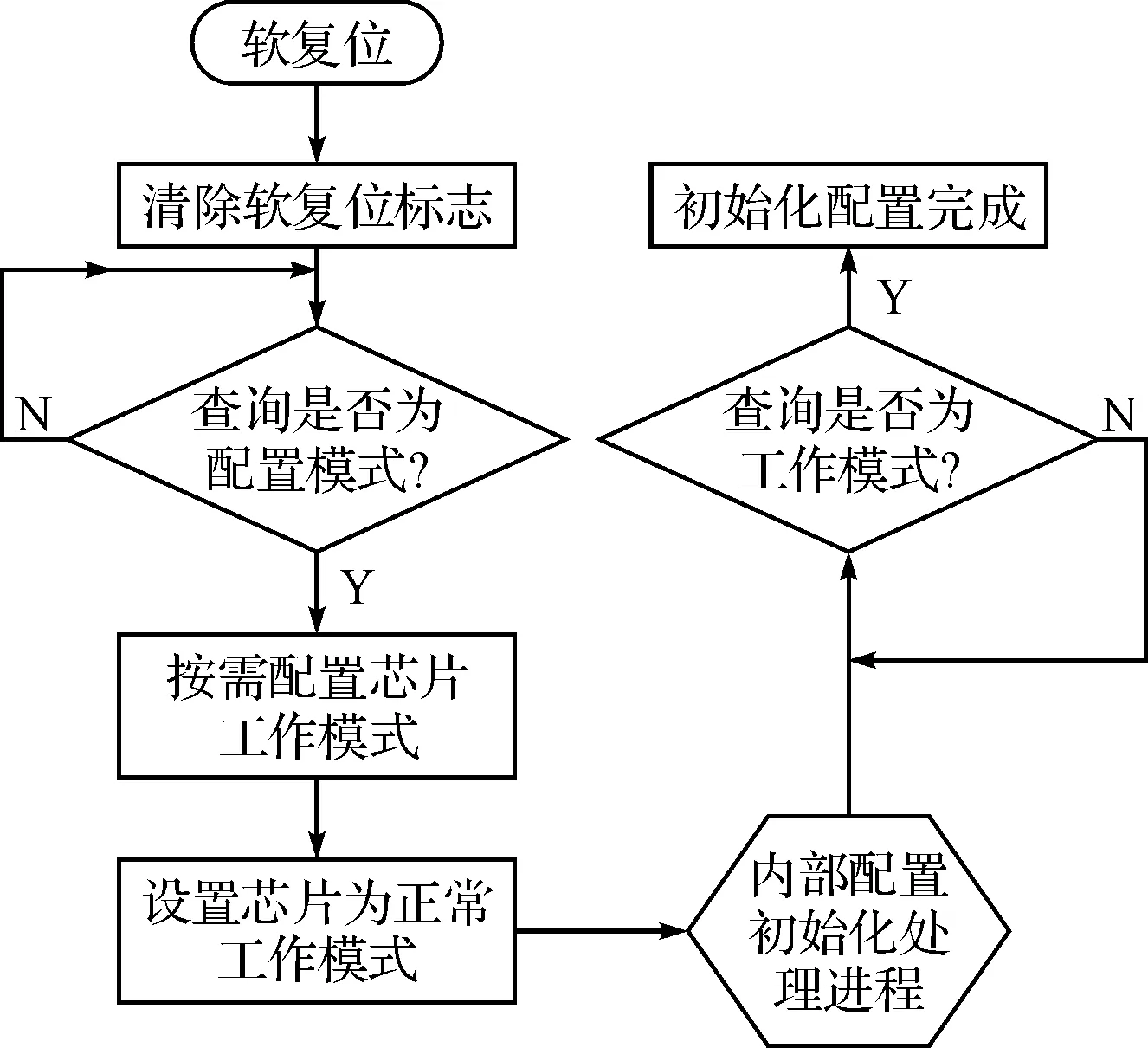

首先,对ML7204进行初始化配置。ML7204内部含有CR0-CR47等基本的控制寄存器以及通过CR寄存器的功能扩展所映射的内部数据空间。CODEC初始化所用的寄存器,除了CR0、CR5用来配合相关的延时、查询等操作以控制芯片时序逻辑外,还需要将CR13、CR31、CR23以及CR10按照功能写入配置字。上述寄存器对应着编解码格式和帧时长、信号路径的控制、编解码器工作使能和语音输出使能等功能控制。

在本次的设计中,依次配置如下:采用G.729-A率编解码,10ms一帧的工作模式;规划音频0通道的模拟输入信号传递路径;使能CODEC-A编解码器,关闭CODEC-B模块;使能音频0的模拟输出信号,关闭音频1的模拟输出信号。该部分的配置仅仅是实现芯片最基本编解码功能,拓展的功能还需添加其他寄存器或内部随机访问存储器(Random Access Memory,RAM)区配置。

ML7204的初始化流程如图3所示。

图3 硬件CODEC软件配置流程图

其次,经过上述对寄存器的配置,CODEC芯片已经正常工作,并开始收发语音数据。当编码器从模拟端收到数据,开始编码并缓存10Bytes后,接收Buffer给出满标志,此时芯片的FR0引脚拉低,FPGA采集到该标志后,执行主机接收数据操作;当Buffer从总线接口收到的10Bytes数据,完全发送给解码器后,发送Buffer给出空标志,驱动FR1引脚拉低,此时FPGA采集到该标志,执行主机发送数据操作。

为更简明便捷地驱动CODEC工作及后续功能扩展,设计了FPGA的状态机,并逐层封装了信号驱动和数据处理的底层操作。在顶层状态机的设计上,除去为状态机基本流程而设计的初始化态和空闲态以外,还分为功能调度、信息处理和底层驱动三大应用部分。

功能调度态的功能为:整合外部程序模块产生的信息,适时调整调度优先级,产生信号量,从而控制FPGA完成状态机在顶层状态的迁移,并提供下一级状态机跳转方向。优先级的动态调整算法由程序的其他模块处理。部分程序伪码如下

mode_sched:

if((schd ==idle) && (work_seq!= null)) /*判断是否有新的调度请求*/

mode_ status<= mode_proc;

else

mode_ status <= mode_schd;

case(schd_order)/*执行调度,根据动态调度算法产生的优先级进行响应,并给后一级状态信息量赋值,选择处理类型*/

order_pri1:

work_seq<= CODEC_initial;

信息处理态的作用是:结合CODEC芯片的初始化流程、数据收发流程设计数据的传递方式组合。状态机执行到该运行态,通过上层传递过来的信号量去选择何种处理类型。处理类型分为CODEC_initial,CODEC_busy,CODEC_idle,CODEC_halt,DATA_send,DATA_recv等。以初始化进程CODEC_initial状态为例,部分程序伪码如下:

mode_proc:

case(work_seq)

CODEC_initial:

case(CONF_seq)

CONF_seq1:

codec_cs<= CHIP_csX;

codec_addr <= CODEC_crX;

codec_sdata <=CONF_data;

work_mode <= mode_drv;

bus_ type<= BUS_wr;

CONF_seq <= CONF_seq2;

底层驱动态接收上层状态机传递过来的异步总线控制参数,通过时序逻辑控制,完成数据读写的操作,控制时序分为BUS_rd和BUS_wr,通过CODEC_BUS_outen信号来控制总线的三态门。操作完毕后,返回上一级状态机,即信息处理态。总线控制时序相对简单,本文不再细述,关键在于和状态机的各级迁移信号结合,并逐层封装起来,给上层状态机逻辑模块调用。

另外还需说明一点的就是先入先出存储器(First In First Out,FIFO)的设计。系统在G.729音频格式,10ms帧长时,每次中断产生10Bytes数据,而在G.711格式,20ms帧长时,每次产生160Bytes。由于CPU调度、底层驱动资源分配等问题,在某些情况下,尤其是在多路CODEC并行工作,CPU负荷加重时,会导致数据的丢失和时延的增大。为充分降低语音的时延和误码率,提高数据传输的效率,本次设计采用FIFO进行数据缓存,同时设计算法适时调整优先级,以保证语音的传输质量。根据上文的配置,在CODEC侧每10ms就会有一个语音数据帧产生,10Bytes,同时拉低FR0信号。状态机在通过各级功能调度后,最终实现该功能的部分伪码如下:

CONF_seq4:

if(fifo_num_cnt CONF_seq <= CONF_seq5; else CONF_seq <= CONF_seq8; CONF_seq5: codec_cs<= CHIP_csX; codec_addr <= CODEC_crX; codec_sdata <=CONF_data; work_mode <= mode_drv; bus_ type<= BUS_wr; CONF_seq <= CONF_seq6; CONF_seq6: fifo_recv_cnt <= fifo_recv_cnt+1; if(fifo_recv_cnt == 0) rxfifo_ery1<= codec_rdata; if(fifo_recv_cnt == 2) rxfifo_wq1<= 1; if(fifo_recv_cnt == 3) rxfifo_wq1<= 0; if(fifo_recv_cnt == 4) fifo_recv_cnt<= 0; CONF_seq<= CONF_seq7; CONF_seq7: fifo_num_cnt<= fifo_num_cnt + 1; CONF_seq <= CONF_seq4; CONF_seq8: fifo_num_cnt<= 0; CONF_seq<= CONF_seq1; work_status<= mode_schd; FIFO采用了FPGA自带的IP核,配置为16Bit位宽,256-words深度。在IP核例化时,读写接口时钟分别根据FPGA主状态机时钟,FPGA与CPU接口控制时钟来选定,同时FIFO的数据、控制接口对接到FPGA相应状态机的模块。 当然上述的程序模块只描述了最基本的模块实现和相互之间的应用关系,在实际的产品工程化中,还牵涉到硬件CODEC更进一步配置,模块调度动态调整算法以及PCM接口模块的程序融合等设计。 5结语 FPGA由于并行处理,实时性高,所以在某些对时延较为敏感的场合尤为适用。本次设计并没有像以前的产品案例中,加入FPGA软核来工程实施,而是采用了Verilog语言来开发,这样对底层逻辑控制较好,适当优化数据通路后,能够在一定程度上提高数据吞吐率,降低延时。对某款设计支持6路CODEC的产品进行测试,以20ms,G.711-A的SIP系统为例,理想实验室环境下,话音时延约为50ms;在音频质量测试子项中,系统的总谐波失真(Total Harmonic Distortion,THD)为-40dB左右。 另外在低成本应用场合,可能仅仅需要处理1到2路音频数据,且也不牵涉到混频算法,数字信号处理器(Digital Signal Processor, DSP)多路编解码的优势并没有得到充分发挥,因此在高性价比设备设计,相关算法技术开发人员不足却需要快速推出市场应用等场合,本次基于硬件CODEC的设计尤为适用,并已在产品应用中产生了较好的经济效益。 参 考 文 献 [1] 杨晓东,郑树强.语音编码在IP调度系统中的应用研究[J].计算机网络,2014(6):61-63. [2] 张忠慧,方元.语音编码方案客观评价[J].计算机应用,2014,34(S1):265-267. [3] 于增贵.ITU-T 8kbps语音编码标准介绍[J].通信技术,1997(4):62-65. [4] 金静,张天骐,万义龙等.TETRA与G.729语音编码算法的比较研究[J].电视技术,2013,37(15):168-172. [5] 杨贵新,谷志峰.G.729语音编码算法研究及基于DSP的实现[J].单片机及嵌入式系统应用,2012(5):9-12. [6] 郭俊利.数字集群通信系统的接入分析与容量估算[J].无线电通信技术,2014,40(1):14-17. [7] 金辉,陈后金,孙江波.VoIP语音编解码器的实现与优化[J].北京交通大学学报,2005,29(2):85-87. [8] 李志国,李乔.车载话音集中控制器中VoIP网关技术实现[J].指挥信息系统与技术,2012,3(2):61-65. [9] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008:166-192. 收稿日期:2016年1月2日,修回日期:2016年2月11日 作者简介:吴伟,男,工程师,研究方向:嵌入式系统的软硬件设计,通信网和以太网接入设备。张禹,男,硕士,工程师,研究方向:模拟电路、电源技术研究,高速A/D、D/A。 中图分类号TN95 DOI:10.3969/j.issn.1672-9730.2016.07.017 Speech CODEC Design Based on FPGA and ML7204 WU WeiZHANG Yu (The 28th Research Institute of China Electronics Technology Group Corporation, Nanjing210002) AbstractSpeech CODEC in voice communication system is usually processed by DSP. Designing DSP hardware circuitry and software arithmetic will solve speech of multi-channels more conveniently. However, in some G.729 format, low-cost information systems, a module of hardware CODEC cooperating with FPGA will realize Speech CODEC more easily in the communication terminal designing and reduce the complexity of embedded system engineering. Key WordsCODEC, G.729, speech process, PCM