基于DSP+FPGA的星载GNSS—R相控阵天线波束控制系统

2016-07-22张德平沈全成汪庆武郭世杰

张德平+沈全成+汪庆武+郭世杰

摘要:针对星载GNSS-R海洋微波遥感器相控阵天线对波束控制提出的要求,提出了一种基于DSP+FPGA的星载GNSS-R相控阵天线波束控制系统,选择高性能的DSP芯片作为核心处理器,实时计算波束控制码,满足了系统的实时性要求。

关键词:波束控制系统;相控阵天线;FPGA;DSP

中图分类号:TN958 文献标识码:A 文章编号:1009-3044(2016)16-0237-03

1 背景

星载相控阵GNSS-R海洋微波遥感器利用中国北斗二代、美国GPS等GNSS星座发射的L波段信号资源,对导航卫星的直射和海面反射信号进行同步接收与实时处理,提供高密度、高精度导航定位解和时延多普勒相关功率数据,可为全球海面风场、海面高程、有效波高等海洋动力环境资料的获取提供高时效微波遥感数据。为了实现对多个海面区域覆盖,星载GNSS-R海洋微波遥感器采用层叠式双面多波束高增益相控阵天线,波束能够快速扫描和变化,空域覆盖面广,要求波束控制系统算法计算精度高、反应时间快。针对上述应用,本文提出了一种基于DSP+FPGA的星载GNSS-R相控阵天线波束控制系统。

2 波束控制原理

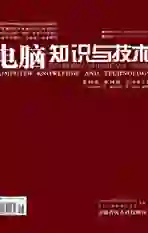

波束控制系统的基本功能是根据不同的波束指向要求,完成阵列中每个单元移相器所需移相码的计算,通过控制电路驱动移相器移相,从而使天线波束指向规定的方向。如图1所示,阵面单元按三角形排列。这种排列可以等效为两个矩阵排列之和。两个矩阵中的单元为了便于区分,分别用圆圈和方块表示。两矩阵相邻单元在y和z轴上的空间相位差为:

所有的修正参数都以码表的形式存于通用存储区当中,通过查表的方式对基本波控码实现各种补偿和修正。

3 系统方案设计

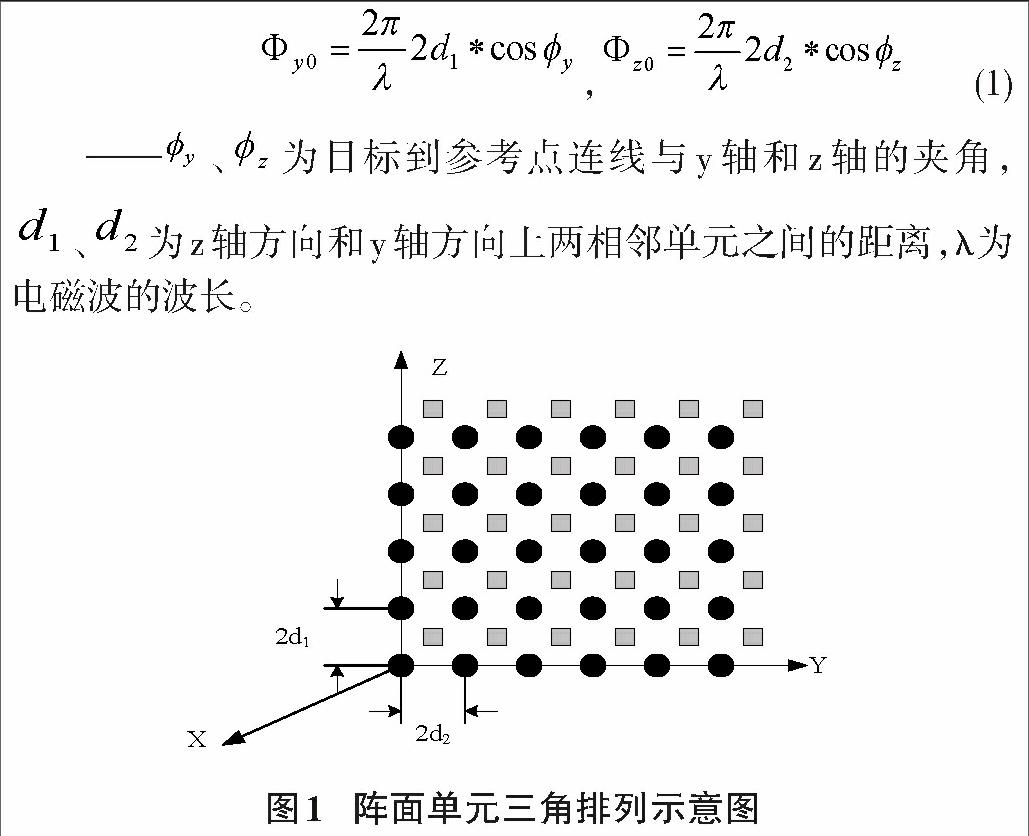

星载GNSS-R相控阵天线包含对天对地两面相控阵天线,采用层叠式结构安装,共有波束控制器I和波束控制器II两个,波束控制器采用“夹心饼干”式安装,安装于两面天线中间,栈接在对天对地两面天线的射频前端底板上,分别完成对天多波束相控阵天线和对地多波束相控阵天线的波控码计算,补偿和配相,使天线波束指向驻留于预定方位,同时分别对两个天线阵面单元实现实时监测。

采用栈接的安装方式,如图2所示,所有控制走线通过印制底板走线,减少了系统控制电缆,有效降低了系统重量,减小了安装空间,提高了系统的可靠性。

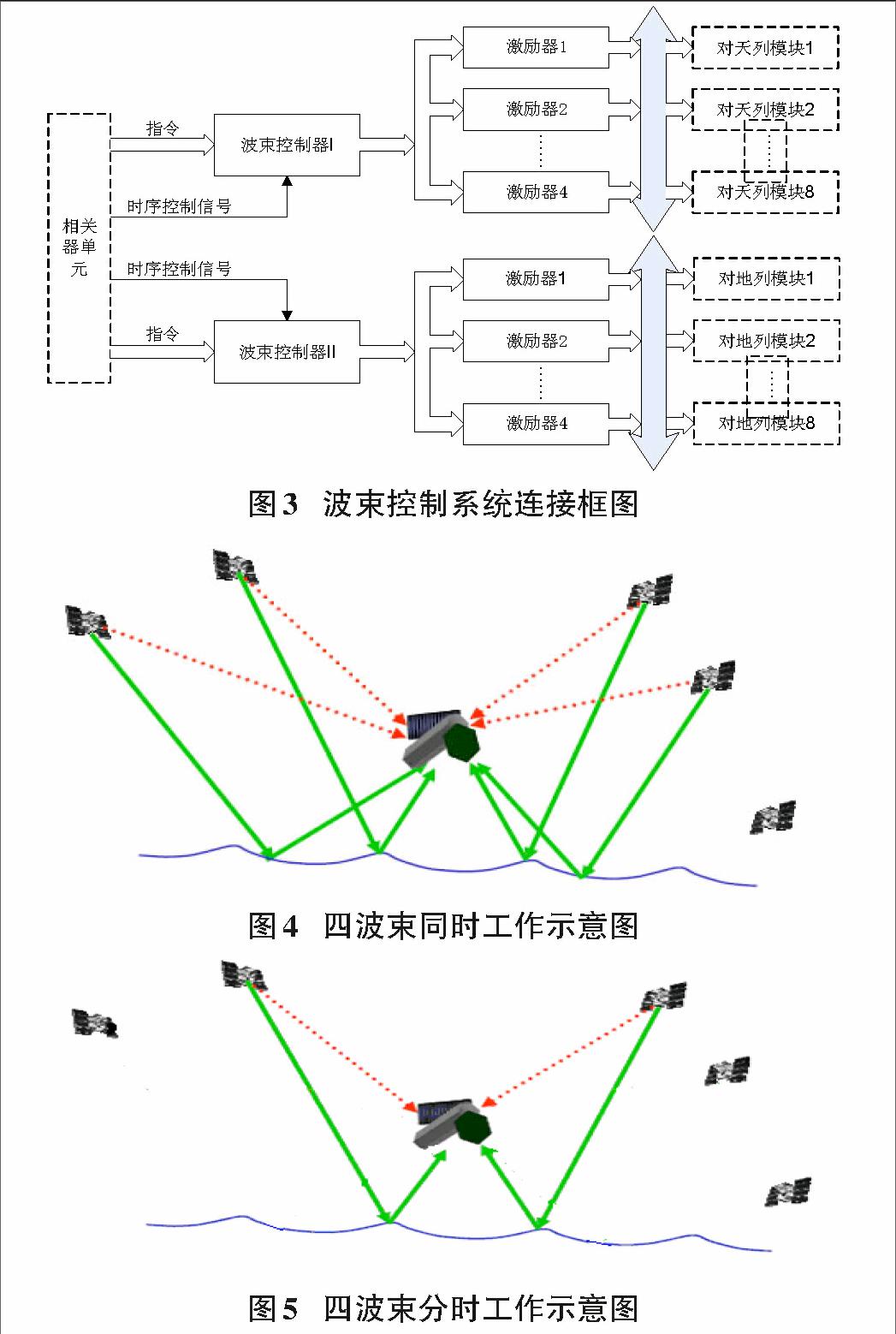

同时,波束控制根据相关器单元的系统状态指令,能够实现对星载双面GNSS-R多波束相控阵天线的多波束分时工作和同时工作进行控制,对地/对天相控阵天线的四个波束既可分时工作也可同时工作,如图4、图5所示。

4 硬件方案设计

波束控制系统主要有三项功能,即波控码计算;波控码的通道分配;阵面监测信息的收集与统计。高性能DSP运算速度快、设备量少、工作方式多、集成度高,且具有高速运算、接口丰富、控制灵活等优点,适合应用于控制系统。FPGA在算法调度,中断和复杂总线机制上没有DSP丰富和灵活,但它擅长于高效的底层计算,资源的灵活配置和工作时序的灵活设计。

综合DSP和FPGA的优点,波束控制器采用DSP+FPGA的设计方案,辅以外围各种接口电路和存储、配置电路。该硬件模块根据需求完成相应的逻辑设计,从而实现波束的实时运算、接口通信设计、相位控制、状态检测和在线数据加载等功能。

在本方案中,DSP选用国产某高性能DSP,该DSP为通用32位浮点处理器,它们采用并行度很高的处理器结构,从而具有许多突出的特点:其浮点运算能力可达1G FLOPS,带有八个功能单元的先进的超长指令字(VLIW)CPU,每周期可执行八个指令;支持8/16/32位数据宽度,支持各种类型的存储器。该DSP的片内存储器包括程序存储器和数据存储器,其中内部程序存储器可作为高速缓存区(Cache)。内部程序存储区和内部数据存储区分别由各自的控制器控制。该DSP通过外部存储器接口(EMIF)使用外部存储器。最重要的是,其有着较强的空间环境适应性。

综合FPGA的优点,在波控系统设计中选择FPGA来实现波控码的格式转换,通道分配以及阵面监测数据的接收等任务。在该波控系统中,FPGA内部根据功能不同将整个任务划分为三个模块来实现配相、阵面监测和本系统自检,其功能框图如图6所示。

配相单元主要以FPGA为核心器件,通过数据地址总线接收DSP的数据。同时,FPGA将处理后的串行波控码以422差分形式向阵面激励器按列配送。送数单元将计算单元算好的波控码进行串并转换后,以422差分形式向对应列激励器配送。

阵面监测与统计单元接收波控系统的自检数据和阵面监测网络的阵面监测数据,根据约定的统计规则对故障进行统计处理。然后通过约定总线接口将处理结果回告中心计算机;监测数据在每个任务周期都将实时回告中心计算机。

5 波束控制软件实现

波束控制软件的控制流程如图7所示,波束控制软件的工作流程由外部调度周期信号同步触发,在一个调度周期内,完成波束控制码的计算,波控配相和状态回告。充分结合DSP和FPGA的处理特点,对波控任务之间的协同处理关系进行详细分析,优化波控系统的架构设计。首先波控数码的计算主要完成基本波控码的计算,频率捷变和相位误差补偿。这些任务的完成需要根据外部波位同步周期信号和频率捷变脉冲信号进行灵活的程序调度。此外波控码计算和补偿的顺序性和实时性的特点要求处理器的要具备比较高的工作频率。所有这些处理需求都比较适合应用DSP来进行处理。对于自定义的阵面波控码通信协议,DSP无法产生特定的接口时序,同时无法做到多通道的并行数码分配。而这一任务特点正符合FPGA时序产生灵活,和并行处理的特点。

波控码的计算由DSP来实现,波控系统的计算单元基于核时钟频率高和内部存储器容量大的特点选用了国产的高性能32位浮点DSP,波控码的计算任务的实现充分考虑了其强大的运算能力、灵活的中断和程序调度机制、功能强大的总线结构以及内置大容量存储器等特点并有灵活的外部存储接口。

配相单元主要完成对波控码的接收、通道分配和格式转换,同时产生天线单元接收所需的同步采样时钟和帧同步信号。地址数据总线接收到的数据存于FPGA内构建的FIFO中,然后对波控码进行分配。分配方式为:行向分配,即首先对第一列的第一个单元分配,接着分配第二列的第一个单元直到第N列的第一个单元分配完毕,又开始新一轮行向分配,即从第一行的第二单元开始,依此类推。

6 结束语

本文结合星载GNSS-R相控阵天线的工程需求,设计了基于DSP+FPGA的星载GNSS-R相控阵天线波束控制系统,以DSP为核心器件的计算单元用来根据波控指令计算波控码,同时进行波控码的各种补偿、拼合以及校验码的计算,以FPGA为核心的配相单元充分地利用了FPGA的时序设计优点来实现波控码的接收、通道分配和格式转换等功能。在配相单元采用了波控码的行向分配方式,实现了各通道对阵面的并行配相。从样机试验的结果来看,这种DSP+FPGA的协同处理结构对大型波控系统的计算和配相是一种有效的设计方法。

参考文献:

[1] 张光义, 赵玉洁. 相控阵雷达技术[M]. 北京: 电子工业出版社, 2006.

[2] Skolnik M I. 雷达系统导论[M]. 北京: 电子工业出版社, 2007.

[3] 吴继华. Altera FPGA/CPLD设计(高级篇)[M]. 北京: 人民邮电出版社, 2005.