高速电路设计中电源完整性的仿真研究

2016-07-21焦喜香中国电子科技集团公司第38研究所安徽合肥230088

焦喜香(中国电子科技集团公司第38研究所,安徽合肥,230088)

高速电路设计中电源完整性的仿真研究

焦喜香

(中国电子科技集团公司第38研究所,安徽合肥,230088)

摘 要:在高速电路设计中,数据传输速度很快且电子元器件工作噪声裕量很小,这就对PCB板电源设计指标提出了很高的要求。本文对高速电路布板后整板电源完整性(PI)以及关键信号线的信号完整性问题进行了设计仿真,实践证明:运用仿真软件对系统进行完整性分析仿真,对于提高整板设计成功率、短设计周期支持作用较大。

关键词:电源完整性;高速电路;信号完整性;HyperLynx

引言

电子元器件朝着微型化、高集成度、多功能化的方向发展,其瞬态切换功率越来越高,工作电压越来越低,噪音裕量变小,相应的PCB板整体电路设计密度更高,速度更快,对电源的要求更加苛刻。在设计复杂程度提高的同时,设计整体PCB整体电路时,势必遇到越来越多影响电源稳定性的各种干扰因素,且目前的信号完整性仿真都是建立在电源系统绝对稳定基础之上的。所以在互连设计时,进行电源完整性分析已成为必然。目前支持仿真的软件有很多,本文主要利用Mentor公司的HyperLynx进行仿真设计。

1 电源完整性分析

电源完整性分析的主要目标就是能够给芯片电路提供干净的电源,消除电源噪声对芯片输出信号的影响。电源噪声对芯片的影响,会引起输出信号的逻辑错误或者产生时序问题。此外,电源地网络和信号网络不是独立的,而是紧紧耦合在一起的。所以电源地的噪声还会通过耦合影响信号线,或者辐射到外面,会产生EMI、EMC的问题等等[1]。

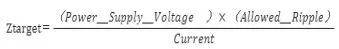

一个电源供给系统(PDS)由电压调整器VRM、 BULK电容、高频退耦电容、电源地平面四个对象构成[2]。一个理想的电源系统其等效阻抗应该为零,即在平面任何地方的电位应该保持稳定不变的,但是在实际运用中存在很大的噪声干扰,甚至有可能影响系统的正常工作。因此电源完整性分析的核心就是设计整个电源供给网络或者其中的一部分,在感兴趣的频率范围内降低整个网络的阻抗,使得电源地网络产生的噪声最小,而电源地网络设计一个主要参数就是目标阻抗,它的定义为:

其中 Power_Supply_Voltage为电源网络的供电电压,Allowed_Ripple为该网络允许的最大纹波,Current为通过的电流值。当前解决电源完整性首先要合理设计PCB叠层,在电源层和地层大面积铺铜,提供低阻抗的路径。对于由于芯片本身内部引起的电源问题最有效的途径就是合理的布置去耦电容[3]。因此解决电源完整性问题的关键应该是选择合适的电容、在合理的位置摆放这些电容,使PDS阻抗在系统的工作频率范围内小于目标阻抗。

2 仿真分析流程

2.1 系统简介

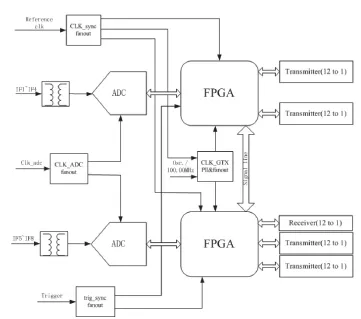

以目前设计的一高速采集系统为例来详细阐述仿真分析的流程。该系统采用高速ADC、高端FPGA以及高速光纤模块为硬件平台来实现数据的采集传输。系统功能框图如图1所示。

图1 系统功能框图

2.2 电源完整性仿真

运用HyperLynx内嵌的功能模块PI来进行电源完整性仿真[4]。PI模块仿真方式分为集总参数仿真和分布参数仿真。集总参数仿真即把整个电源平面看成一个集成点,而分布参数仿真采用频点扫描,可选择要仿真的管脚,看管脚之间的交互影响。一般我们在进行电源Net仿真时,选择集总参数对整个网络进行阻抗分析更加有效。集总参数仿真也可导出到预分析环境中进行增减电容,替换电容,改变安装方式,改变叠层等What-If分析方法来进行该供电网络的PCB优化设计。

首先设置板级的分析数据库,将PCB板图设计数据直接读入,确定板材材料,明确PCB叠层关系,设置各电源网络的直流电压,导入去耦电容模型或设置去耦电容参数包括ESR和ESL。根据设计要求确定电源平面的噪声容限,一般按照电源网络的5%来定义,最大动态电流一般按照芯片工作最大电流的50%来计算要仿真的电源网络目标阻抗。

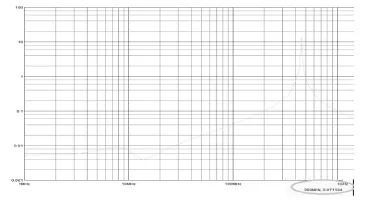

先对FPGA中关键的内核电压进行仿真。通常用钽电容来进行板级低频段去耦,可以用几个或多个电容并联以减小等效串联电感。在高频段,把去耦的频率范围分成3到4个频段。在本系统中FPGA实际工作频率为300MHz,在低频段选择多个470uf的钽电容并联,然后高频段利用公式计算出所需要的去耦电容容值。要考虑利用多个陶瓷小电容并联简单有效的减小阻抗,同时容值间隔不能太大,要有效控制反谐振点阻抗的幅度。通过计算,我们可以选择2.2uf和0.1uf的电容组合为该电源网络高频段进行去耦设计。

图2为FPGA内核电压网络频率—目标阻抗曲线图,从图中可以在为300MHz时,最大的阻抗为0.071124,即纹波电压最大为71mv。在实际设计时允许阻抗在目标阻抗线上一点,因为仿真的时候没有考虑芯片本身内部的滤波设计。因此可以看出电容设计基本上是可以满足阻抗设计要求的。

图2 FPGA内核电压网络频率目标阻抗曲线图

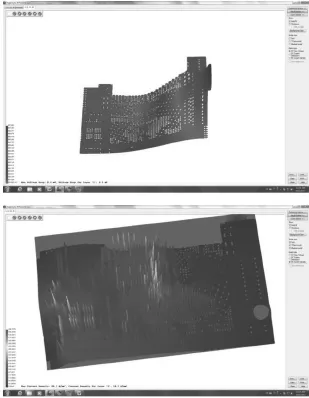

同时还可对电源平面可进行压降和电流密度的仿真,防止器件出现失效过大的电压降,导致器件逻辑出错;或因过高的电流密度导致PCB损坏。从图3可以看出,该电源网络最大压降为0.4mv,表层最高电流密度为14.7A/mm2,是能够满足设计要求的。

3.2 信号完整性仿真

根据上一章节对电源完整性仿真的结果,同时可以对主要网络的信号完整性进行仿真,从而更直接的验证电源完整性设计的合理性。对于本系统电路来说,由于要实现带宽400MHz的中频采样,后期传输速率很大,因此要着重关注光纤数据的传输。选取其中一对光纤输出差分线,导入到前仿真中,然后提取过孔的S参数模型,如图4所示。

图3 电源网络电压压降和电流密度仿真

图4 GTX信号线导入前仿真设计

图5 光纤传输线仿真眼图结果

图5为传输速度为8Gbps的数据传输眼图仿真结果,眼图过渡良好,眼部充分张开,说明接收器侧的FPGA可以轻松地解读数据,能够很好的实现8Gbps的数据传输。

3 实际测试结果

在本系统实际测试中,运用光缆实现测试数据自回环,通过计算机端的FPGA逻辑分析软件Vivado来观察光模块的工作状态。

测试结果如图6所示,可以看出光模块可以很好的实现8Gsps的数据传输,无误码出现。

图6 光模块传输数据率8Gsps的测试结果

4 结束语

本文简要的介绍了利用电路仿真工具进行电源完整性以及信号完整性仿真的方法和流程,并结合项目中的电路设计进行仿真,并对结果进行了验证。实践证明:通过软件对电路PCB板进行电源完整性以及关键信号线进行仿真,可以有效的缩短设计的周期,降低设计的难度,提高设计的可靠性。

参考文献

[1] 高性能PCB 的SI/PI 和EMI/EMC仿真设计 Ansoft培训手册.

[2] 申伟,唐万明,王杨.高速PCB的电源完整性分析[J].现代电子技术,2009,311(24):213-218.

[3] (美)伯格丁(Bogatin,E.)著.李玉山等译.信号完整性分析[M].北京:电子工业出版社,2005.

[4] 张海风等编著.HyperLynx仿真与PCB设计[M].北京:机械工业出版社,2005.

[5] 堵军,高辉,张益平.电路设计中的信号完整性分析和研究[J].电子与封装,2013,13(8):25-29.

Simulation Research of Power Integrity in Hign-speed Digital Design

Xixiang Jiao

(No.38 Research Institute.CETC, Hefei, Anhui, 230088, China)

Abstract:In the design of high speed circuit, the data transmission speed is very fast and the electronic components work noise margin is very small, therefore It is an enormous challenge to get a well-regulated power supply.This paper introduces the emulation design and analysis of power integrity and signal integrity of high-speed circuit boards, packages and high-speed serial links.Based on the simulation tool,the problem for the power supply of whole circuit and key signal line are taken as the research obiects.The practice has proved that emulation used simulation tool can speed design, improve the success of circuit boards and decrease cost.

Key words:Power Integrity; Hign-speed Circuit; Signal Integrity; HyperLynx

中图分类号:TN86

文献标识码:A

文章编号:2095-8412 (2016) 02-226-04

DOI:工业技术创新 URL: http//www.china-iti.com 10.14103/j.issn.2095-8412.2016.02.028

作者简介:

焦喜香(1982-),女,工程师,博士,从事雷达数字收发方面的设计与研究。