基于嵌入式系统的Nor Flash数据安全保护设计

2016-07-09吴有肇杨立衡

吴有肇,杨立衡

(1.TCL多媒体科技控股有限公司全球研发中心,广东 深圳 518067;2.深圳信息职业技术学院学报,广东 深圳 518172)

基于嵌入式系统的Nor Flash数据安全保护设计

吴有肇1,杨立衡2

(1.TCL多媒体科技控股有限公司全球研发中心,广东 深圳 518067;2.深圳信息职业技术学院学报,广东 深圳 518172)

摘 要:在各种嵌入式系统产品中,特别是各种“智能”产品中,Nor Flash作为重要的记忆体器件,存放着系统正常启动、运行的关键程序和用户数据,其数据内容的正常读写对整个系统的正常工作和可靠性而言及其重要;然而在设计和应用实践中经常发生Nor Flash内数据被异常改写或丢失的现象,导致系统无法启动或启动后系统异常运行。本文提出了一种软硬件结合方法实现对Nor Flash 的数据内容进行保护,提高了嵌入式系统的可靠性。

关键词:Nor Flash;数据保护;交流开关机

引言

随着便携式电子产品的普及,Nand Flash以其价格低廉的优势被越来越多的用于大容量数据存储[1-2]。相较而言,Nor Flash拥有的高传输效率、高可靠性和易于使用等优点[3-6],在嵌入式系统产品中,大量使用了Nor Flash存放一些非易失性存储程序和数据,其数据的正常读写直接影响到整个系统的稳定性和可靠性。实际工作中,Nor Flash数据读写异常往往是因为在数据保护方面的设计缺陷导致数据被异常改写、丢失或无法提供补救措施导致的。嵌入式系统中,处理器与Nor Flash一般通过SPI总线接口进行通讯[7-10],SPI总线命令简单易用。本文基于SPI接口的Nor Flash内部框架、数据保护机制设计了一套软件和硬件的数据内容保护方案,实现了对Nor Flash的存储阵列进行有效地保护[11-16]。

1 Nor Flash内部框架及数据保护机制

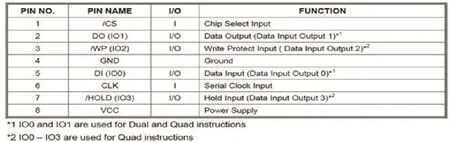

Nor Flash一般采用SPI接口,SPI接口是一种事实标准,并没有标准协议,大部分厂家都是参照Motorola的SPI接口定义来设计的,但正因为没有确切的版本协议,不同厂家产品的SPI接口在技术上存在一定的差别,容易引起歧义,有的甚至无法直接互连(需要软件进行必要的修改),SPI接口共有4根信号线:设备选择线、时钟线、串行输出数据线、串行输入数据线。常见器件的接口定义如下图1定义,包含片选信号/CS、串行输入DI、串行输出DO、时钟信号CLK、写保护/WP、电源VCC、地GND及保持/HOLD等信号引脚。

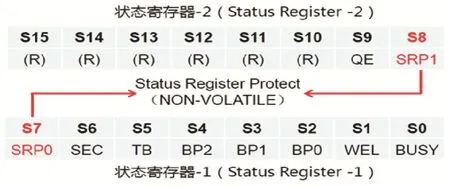

以2M Bytes存储容量器件为例,其整体框架如图2所示。其中/WP写保护引脚通过内部的写控制逻辑单元保护状态寄存器(Status Register),写保护脚为低电平有效;状态寄存器的设定值决定了Flash存储阵列受写保护的方式。状态寄存器共两个字节,分别为状态寄存器-1和状态寄存器-2,其状态位定义见如图3。

图1.Nor Flash器件引脚定义Fig1. Pin definition of Nor Flash

其中S6、S5、S4、S3、S2五个比特位决定了存储阵列的数据受保护方式。

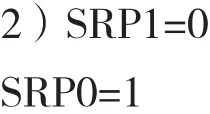

其中SRP1、SRP0比特位决定了状态寄存器受保护的状态,与/WP位结合使用的保护方式统计为图4:

图2.Nor Flash 框图Fig 2. Block Diagram of Nor Flash

图3.状态寄存器Fig 3.Status Register

图4 状态寄存器保护Fig.4 Status Register Protection

① /WP 拉高能写、拉低能写,则为(1)

② /WP 拉高能写、拉低不能写,则为(2)

③ /WP 拉高、高低都不能写,则可能为(3)、(4)

④ 若为(3),重启后SRP1、SRP0为00,可写

⑤ 若为(4),永远不可写

2 数据异常案例分析

以Nor Flash在数字电视产品中的应用为例,Nor Flash存储数据经常发生的异常为数据被改写,系统无法正常启动或启动后运行异常,现象为DTV信源下交流关开机后死机,具体表现为机器无声有像,显示的动态开机LOGO画面为绿色且显示在画面左右两边,显示的字符“智能系统启动中,请稍候……”显示在画面左右两边,且字符不会自动消失。经过分析,此问题为系统启动的mboot的代码数据被破坏,软件除了升级之外不会去写代码对应的地址范围内(代码区)的数据,所以判断是Flash中的数据被破坏了。考虑到数据被破坏可能的因素在硬件的/WP引脚和软件设定的状态寄存器两个方面,分别从软件和硬件两个方面进行分析:

2.1软件分析

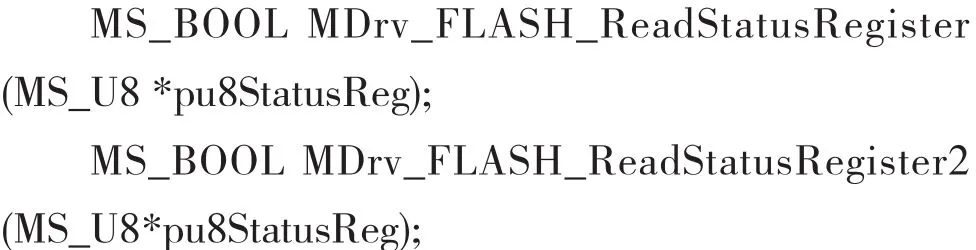

为确认状态寄存当前的设定值及受保护方式,在写Flash(如更换Project ID的操作)前后用以下函数读状态寄存器:

结果:

StatusRegister-1的值为0x80,

StatusRegister-2的值为0x00,

写前后状态寄存器的值一样。

通过查阅图4,我们知道状态寄存器保护位定义的状态寄存器保护方法为:

1)软件保护:如(1),此时无论WP为何种状态,WEL=1时状态寄存器可被写;

2)硬件保护:如(2),此时状态寄存器可写与否取决于WP电平的高低;

3)上电保护:如(3),只有重新上电时才可以被写;

4)永久保护:如(4),只能写一次,之后永久保护;

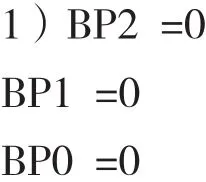

SRP1、SRP0等状态寄存器的初始值由mboot设定,软件预抄写时已设定了初始默认值。为了解状态寄存器块保护位定义的存储阵列受保护方式,可查阅Nor Flash芯片规格,如图5。

由以上可知,此案例中:

存储阵列无保护,即存储在存储阵列Block内的代码或用户数据可能被异常改写为保护存储整列,BP2/BP1/BP0需按需求改写,能否改写取决于SRP1/SRP0的设定值。

图5 存储整列保护Fig.5 Memory Array Protection

状态寄存器为受硬件保护方式,状态寄存器能否被改写,取决于WP脚的设定

2.2硬件分析:

硬件电路设计如图6:

R258、R231为NC,R207接地,写保护脚硬件拉低。WP=0,状态寄存器无法被改写和配置。

图6 硬件设计Fig.6 Hardware Design

2.3数据异常原因分析总结

1)BP2、BP1、BP0在器件出厂时默认设定为0,所有存储阵列不受保护

2)SRP1、SRP0 mbbot默认设定为(0,1),状态寄存器的改写取决于WP引脚电平

3)WP引脚硬件强制设定为0(接地),状态寄存器被强制保护无法改写,BP2~BP0无法改为可保护存储阵列的定义值。

这种情况下,无法单独使用软件更改状态寄存器设定值的方法来保护存储阵列内的数据!

2.4Nor Flash 数据保护电路设计及验证:

硬件电路更改参考图6,要求如下:

R258、R231连接,R207 断开。

(1)R258连接GPIO口,由GPIO口控制WP的高低电平变化;

(2)R231上拉主要目的是考虑GPIO的驱动能力不足,删除207对地下拉。

软件设定存储阵列为全部受保护方式。

改善验证如下:

(1)WP写保护脚受程序控制。

不写状态寄存器时,/WP脚为低电平;

改写状态寄存器时,/WP脚受控拉高;

(2)经硬件改动后,写Flash操作前后读状态寄存器,结果为:

StatusRegister1=0x9C(BP2~BP0都为1,整改Flash Block受保护)

StatusRegister2=0x00。

可以看出,主动写操作前整个Flash的数据是受保护的;写数据前将WP拉高,临时改变状态寄存器值使存储阵列不受保护(可写);将/WP拉低,已写入的状态寄存器值受保护;写数据后,将/WP拉高,改变状态寄存器值使存储阵列全部受保护;将/WP拉低,已写入的状态寄存器值受保护。

3 Nor Flash数据保护设计指引

3.1硬件设计指引:

(1) /WP引脚直接上拉(无GPIO控制)

这种方法针对GPIO数量不足的情况,将/WP脚直接上拉至3.3V,状态寄存器不受保护;

风险:状态寄存器和存储阵列值的改变需以指令方式更改,同时出现状态寄存器和存储阵列数据被异常改写的几率几乎为零,基本没有风险。

(2)/WP用GPIO口控制

①将/WP脚连接至GPIO并上拉至3.3V:

● 针对GPIO驱动不足的情况;

● GPIO初始化为低电平。

风险:上电GPIO未完成初始化瞬间可能有导致状态寄存器被改写,这种概率极小,且同时存储阵列数据被改写的可能性就更小,基本没有风险;

②将/WP脚连接至GPIO(初始化为低电平)并下拉至GND(针对GPIO驱动力强的情况)。

风险:无理论上的风险,但要求GPIO有足够的驱动能力。

3.2软件设计指引:

(1)总体流程如图7;

图7 软件流程图Fig.7 Software Flow Chart

(2)逻辑描述:

①主动写操作前:

读取状态寄存器判断;

确保存储阵列是受保护的;

②写数据前:

a、拉高/WP(GPIO控制的情况)

b、设定状态寄存器值,使存储

阵列不受保护(可写);

c、拉低/WP(GPIO控制的情况)

③写入数据;

④写数据后:

a、拉高/WP(GPIO控制的情况)

b、设定状态寄存器值,使存储阵列受保护(不可写);

c、拉低/WP(GPIO控制的情况)

(3)保护判断:

状态寄存器的设定应根据实际应用来做,特别是SEC/TB/BP2/BP1/BP0根据实际设定来判断。Flash状态寄存器的出厂Default值为0x00.

设定原则:

①软件保护:

● 一般在无GPIO控制/WP的情况

● SRP1=0、SRP0=0

②硬件保护:

● 一般在有GPIO控制/WP的情况

● SRP1=0、SRP0=1

③上电保护:

● 只能在每次上电时设定一次状态寄存器

● SRP1=1、SRP0=0

④永久保护:

● 只能设定一次状态寄存器,之后不可改;

● 一般是用于存放一些重要的Key等等

● SRP1=1、SRP0=0

⑤BP2、BP1、BP0 不能同时为“0”

4 小结

Nor Flash数据保护的重点在于对数据保护机制的深刻理解和设计合理的数据保护方式,让硬件或软件能安全合理地保护状态寄存器,同时合理地设定状态寄存器,以使存储阵列能被有效地保护。

参考文献(References):

[1] 陈超文,彭国杰,王忆文等. 基于PLB总线的NOR Flash控制器设计[J]. 微电子学与计算机,2014,31(5),83-86.

CHEN Chaowen,PENG Guojie,WANG Yiwen, et.al. Design of NOR FLASH Controller Based on PLB General Bus[J]. Micro Electronics and Computer,2014,31(5),83-86.(in Chinese)

[2] EYEE Hun NAM,BRYAN Suk Joon Kim. An Out-of-Order Flash Memory Controller Architecture[J]. IEEE Transactions on Computers,2011,60(5):652-666

[3] HARRIS david money, harris sarah l. digital designand computer architecture[M]. USA: Morgan Kaufmann, 2007.

[4] IEEE Computer Society. IEEE Recommended Practicefor Softawre Requirements Specifications[S]. IEEE Std830-1998: Los Alamitos, CA, 1998.

[5] 杜伟庆,苏凯雄. 嵌入式系统中NOR Flash 的分块管理与实现[J]. 计算机与数字工程.2009,(12),80-85

DU Weiqing,SUKaixiong.Blockbased Management and Implementation of NOR Flash in Embedded System[J]. Computer & Digital Engineering.2009,(12),80-85(in Chinese)

[6] Walter J S. A unified Algorithm for Elementary Functions[ C]. AFIPS Spring Jo int Computer Conference,1997, ( 38) : 379~ 385

[7] 李明明,王全忠,郭伟,等.一种NOR FLASH 控制器验证平台的研究[J]. 现代电子技术,2015,38(10):162-165.

LI Mingming,WANG Quanzhong,GUO Wei,et,al. Research on a verification platform for NOR FLASH controller[J].Modern Electronics Technique, 2015,38(10):162-165(in Chinese)

[8] HILDERMAN V,BAGHI T. Avionics certification:a complete guide to DO-254(hardware)[M]. America:Avionics Communi-cations Inc,2007.

[9] Cadence. OVM class reference[M/OL]. [2010-12-08]. http://www. docin.com.

[10] ACZYNSKI J. Verification methods for field programmable gate array (FPGA) designs[J]. Elektronik Industrie,2004,35(11):58-61.

[11] 张欢庆,高丽. 嵌入式Linux中Nor Flash设备驱动研究[J]. 商丘职业技术学院学报,2012,11(2):43-46

ZHANG Huanqing, GAO Li. Research on the Embedded Linux NOR Flash Device Driver[J]. Journal of Shangqiu Vocational and Technical college.(in Chinese).

[12] EYEE HunNAM,BRYAN Suk joon kim. An Out-of-Order Flash Memory Controller Architecture[J]. IEEE Transactions on Computers,2011,60(5):652-666

[13] Li J H. Zhang X, Yu M. A 1.2-V Piecewise Curvature-Corrected BandgapReference in 0.5 m CMOS Process[J]. Very Large Scale Integration (VLSI)Systems. IEEE Transactions on. 2011. 19(6): 1118-1122.

[14] Bendali A. Audet Y. A 1-V CMOS current reference with temperature and process compensation[J]. Circuits and Systems I: Regular Papers, IEEE Transactions on,2007,54(7): 1424-1429.

[15] Razavi B. Design of analog CMOS integrated circuits[M]. Tata McGraw-HillEducation, 2002.

[16] Leung K N,Mok P K T, Leung C Y. A 2-V 23卞A 5.3-ppm/。Ccurvature-compensated CMOS bandgap voltage reference[J]. Solid-State Circuits.IEEE Journal of, 2003,38(3): 561-564.

【责任编辑:高潮】

【信息经济研究】

Design of data safety protection for Nor Flash based on embedded system

WU Youzhao1, YANG Liheng2

(1. TCL Multimedia Technology Holdings Ltd. Global R&D Center, Shenzhen 518067, China;2. Journal Editorial Department, Shenzhen Institute of Information Technology, Shenzhen 518172, China)

Abstract:In the products especially in the Smart products based on embedded system,Nor Flash is used to storing the key programs and user data for system's booting up and running, the normal read/write operation of the data in Nor Flash is very important to the whole system. The data in the flash is usually written abnormally and cause the system booting up or running failure. This article design of the peripheral circuits to protect the data in NOR flash and improve the reliability of the system.

Key words:Nor Flash; data Protection; AC power on/off

中图分类号:TP333

文献标识码:A

文章编号:1672-6332(2016)01-0053-05

[收稿日期]2015-11-26

[作者简介]吴有肇(1984-),男(汉),福建宁德人,工程师,本科,主要研究方向:液晶电视嵌入式系统硬件方案及电路研究。E-mail:evanwu201404@163..com