DTMB多通道调制器的设计与实现

2016-07-06贾旭光潘长勇

贾旭光,佟 璐,阳 辉,潘长勇,

(1.清华大学 信息技术研究院,北京 100084; 2.数字电视国家工程实验室(北京),北京 100191)

DTMB多通道调制器的设计与实现

贾旭光1,佟璐2,阳辉1,潘长勇1,2

(1.清华大学 信息技术研究院,北京 100084; 2.数字电视国家工程实验室(北京),北京 100191)

摘要:在地面数字电视基站建设中,为了满足覆盖区域多套标清和高清节目的传播要求,常常需要配置多台数字电视激励器。为了简化基站设施建设,提高硬件复用,提出了一种多通道数字电视调制器解决方案,实现仅用一台激励器即可完成基站建设。以五通道DTMB调制器为例完成了在FPGA芯片上的实现。经过实际测试满足设计要求,具有较大的实用价值。

关键词:DTMB;调制器;多通道;FPGA

地面数字电视不同于有线数字电视和卫星数字电视,是通过在地面建立发射基站进行数字电视信号的广播传输。一台数字电视激励器只能传输有限的标清或高清节目,无法满足人们对几十套节目的收视需求。因此,在现有地面数字电视基站建设中,常常需要配置多台数字电视激励器,将各台调制器分别调制到不同的VHF/UHF频段上,在射频进行合并接天线发出,完成多套节目的无线广播。

在城市郊区和农村,频谱资源较为丰富,数字电视广播可用频段较为集中,基于该现状,本文提出了一种多通道数字电视调制器的设计方案。本设计支持多路DTMB信号调制,每一路均支持全部的DTMB调制模式。本文以五通道为例详细介绍了多通道调制器的设计与实现。五通道调制器共包含5个DTMB基带调制模块和一个多通道合并模块。DTMB基带调制模块完成对输入TS码流的DTMB调制和基带信号输出,多通道合并模块完成对5个通道的DTMB基带信号的上采样、低中频调制和合并输出,合并输出经过正交调制上变频到射频频段,最后接天线发出。

1DTMB标准介绍

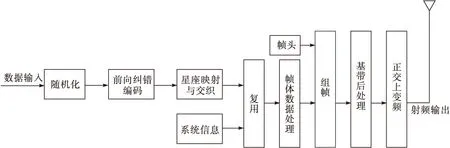

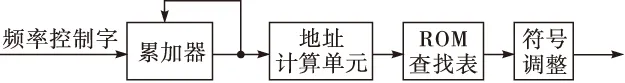

DTMB是我国具有自主知识产权的地面数字电视标准,并于2011年被国际电信联盟ITU纳为地面数字电视国际标准。DTMB以时域正交频分复用(Time Domain Synchronous-Orthogonal Frequency Division Multiplexing, TDS-OFDM)调制技术为核心,形成了一套完整的自有知识产权体系,在帧结构、调制技术和接收机同步技术上具有鲜明的技术特点[1]。DTMB支持单载波和多载波调制,0.4、0.6和0.8编码码率,三种帧头模式以及QPSK、16QAM和64QAM等多种调制模式,能够传输5.414~32.486 Mbit/s速率的码流。本设计需要对DTMB调制器的输出做进一步处理和合并。DTMB调制器的功能框图如图1所示。

图1 DTMB调制器功能框图

DTMB调制器完成从输入TS流到地面数字电视广播信道传输信号的转换。具体流程如下:将接收到的TS码流进行随机化处理,以保证传输数据的随机性,接着对数据进行信道编码,DTMB采用两级编码结构(内码采用LDPC,外码采用BCH),经过编码的数据通过星座映射为符号,对符号进行时域卷积交织,交织后的符号与系统信息TPS结合经过频域交织后组成帧体数据,帧体数据添加帧头组成基本信号帧。最后经过基带后处理SRRC脉冲成型滤波和正交上变频后变成带宽为8 MHz的频带信号,通过天线发出。

2多通道合并单元设计与实现

多通道合并单元完成对5路DTMB调制器输出信号的合并,DTMB调制器的符号速率7.56 MSymol/s,经过4倍上采样和SRRC滤波后,基带信号输出时钟为30.24 MHz。在该时钟模式下,系统仅能将基带信号调制到±8 MHz两个频点上。为了完成5路信号的合并,至少需要5个频点才能完成信号搬移,从而需要对输入基带信号进行上采样。本设计对DTMB基带信号再次进行4倍上采样,最终合并后的信号采样时钟为120.96 MHz。该时钟模式下,可支持将5路信号根据实际频谱占用情况调制到15个频点中的任意5个上。同时,考虑到后级功放在宽频谱范围内无法保持增益一致,添加功率调整模块进行预校正。功率调整模块可与上采样模块交换,上采样后工作时钟增加4倍,功率模块在高时钟模式下面向FPGA实现时有较大的时序压力,因此对输入信号先进行功率调整。多通道合并单元主要包含4个模块,分别为功率调整、上采样、低中频调制和合并限幅。多通道合并单元架构图详见图2。

图2 多通道合并单元架构图

2.1功率调整

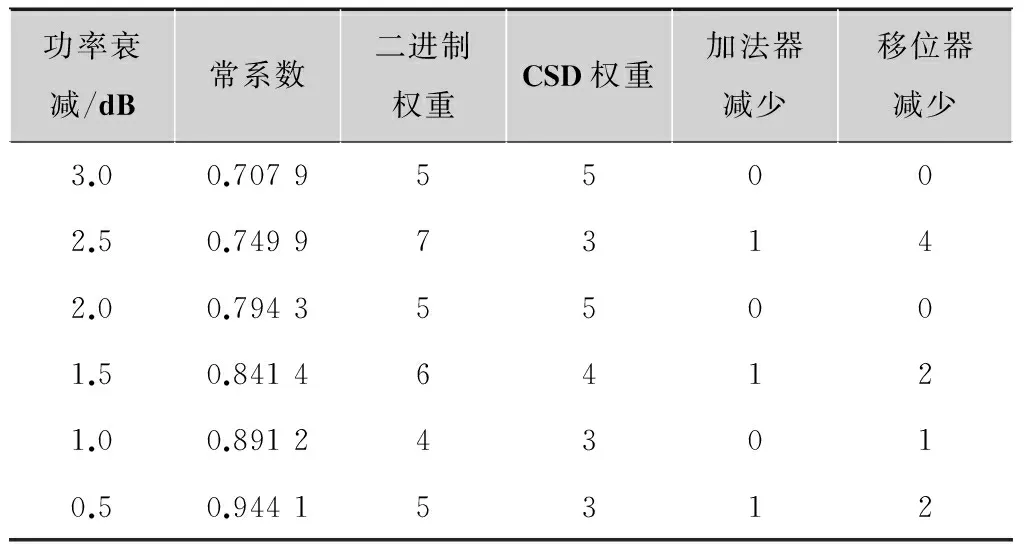

一个二进制数中非零元素的个数记为该数的权重。一个数的CSD编码是唯一的,CSD码中任意两个非零位不相邻,且含有的非零位是所有数制表示法中最少的,即权重最小。系数经CSD编码后,权重最小,能最大幅度地减小运算过程中加法器的数量。

如表1所示,每路经过CSD编码的常系数乘法器和二进制编码相比,共节省加法器3个,移位器9个,五通道调制器共需要10个功率衰减模块(每个通道IQ各需要一个),因此,总共节省30个加法器和90个移位器。随着通道数的增长和功率衰减步进的减小,采用CSD编码的设计对加法器和移位器的节省优势将越来越明显。

表1加法器和移位器资源节省对比

功率衰减/dB常系数二进制权重CSD权重加法器减少移位器减少3.00.707955002.50.749973142.00.794355001.50.841464121.00.891243010.50.94415312

2.2上采样

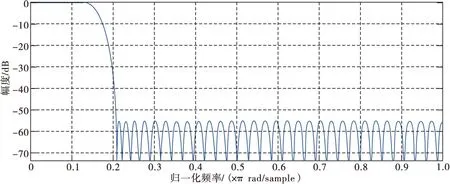

本设计对基带信号进一步进行4倍上采样,系统工作时钟为120.96 MHz。4倍上采样通过每两个采样点插入3个零实现,经过内插后,需要级联低通滤波器抑制镜像频谱,常用的滤波器有CIC滤波器、半带滤波器和奈奎斯特滤波器。CIC滤波器具有不需要乘法器,占用资源少的特点,然而,CIC滤波器阻带衰减差,通带平坦度差,在实际应用中,常常需要级联多个滤波器和添加补偿滤波器使用,从而增加了实现复杂度。半带滤波器通带和阻带对称,常与CIC滤波器级联使用。奈奎斯特滤波器具有归一化的直流增益和平坦的通带特性[3]。奈奎斯特滤波器使用较低的滤波器阶数就可以得到较大的阻带衰减。固定系数奈奎斯特滤波器的设计和实现也比较简单,因此常常被用在抽取和内插器中。

奈奎斯特滤波器的频率传递函数为

(1)

式中:β为滚降因子,取值范围在[0,1],1/T为采样率。奈奎斯特滤波器的单位冲激响应为

(2)

奈奎斯特滤波器有5个主要参数:波段数L,滚降因子β,过渡带带宽TW,阻带衰减AST和滤波器阶数N,且3 dB截止频率为π/L。本文设计的奈奎斯特滤波器参数为:波段数L=6,滚降因子β=0.25,阶数N=74。从图3中可以看出阻带衰减高达55 dB,满足项目要求。

图3 奈奎斯特滤波器频率响应

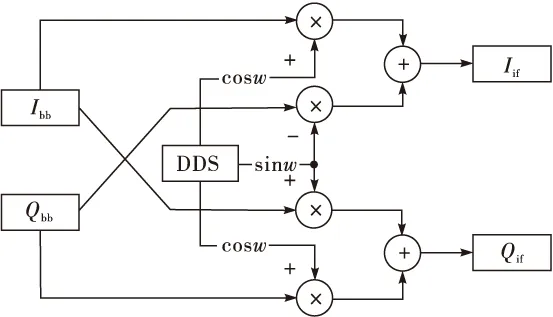

2.3低中频调制

DTMB基带信号经过4倍上采样后,采样时钟提升为120.96 MHz,因此可以将基带信号分别调制到±8 MHz、±16 MHz、±24 MHz、±32 MHz、±40 MHz、±48 MHz和±56 MHz频点上,加上零中频共有15个频点可供选择。在实际应用中经常存在连续频段被占用的问题,因此,本模块还要根据实际频谱占用情况将5路信号灵活调制到15个频点中的任意5个上。本文采用直接数字式频率合成器(Direct Digital Synthesizer,DDS)产生调制到如上15个频点所需的正交频率信号。每一路基带信号对应一个DDS模块,通过对DDS模块频率控制字的配置,实现对该路基带信号15个频点的任意调制。DDS结构框图如图4所示。

图4 DDS结构框图

频率控制字控制累加器的步进,由于本设计对初始相位没有要求,所以舍弃了相位控制字。累加器位宽为32位,位宽越高,输出频率精度越高。截取累加器高12位送入地址计算单元。为了节省片上ROM资源,ROM查找表只存储四分之一的正弦波形,地址计算单元根据高2位地址信号决定寻址地址。符号调整单元同样根据高2位地址信号对ROM查找表的输出进行正负和翻转调整,地址计算单元和符号调整联合实现仅存储四分之一周期波形就能够输出完整的正余弦信号。

假设DTMB调制器的基带信号输出为Ibb+jQbb,中频信号为cosw+jsinw,则低中频调制信号输出为[4]

Iif+jQif=Ibb×cosw-Qbb×sinw+

j(Qbb×cosw+Ibb×sinw)

(3)

式中:w为低中频频率。

每一路基带信号低中频调制实现框图如图5所示。

图5 低中频调制实现框图

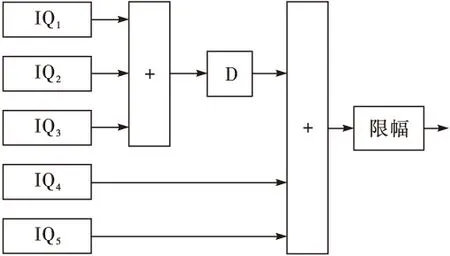

2.4合并限幅

本设计中的功率调整和上采样中的奈奎斯特滤波器单元均采用了大量了组合逻辑和触发器资源。加法器的输入为5路位宽为16的数据,采用合理的加法树结构和流水单元能有有效减少组合逻辑路径,减小FPGA时序约束压力。本设计采用三叉树结构优化加法器。最终对加法器的输出进行限幅处理,输出到DA经过正交调制和功率放大到射频输出。三叉树加法器结构如图6所示。

图6 三叉树加法器结构

3DTMB多通道调制器测试结果及分析

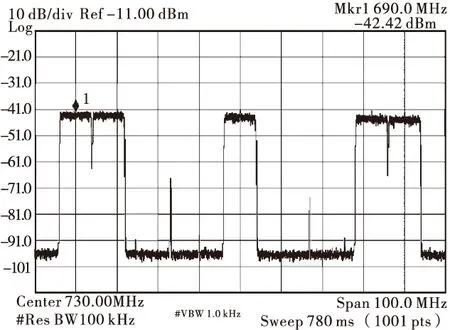

本文将第一路和第二路DTMB基带信号分别调制到-40 MHz和-32 MHz频点,对第三路不做调制,对第四路和第五路分别调制到+32 MHz和+40 MHz频点,然后将多通道调制器的输出正交调制到730 MHz的载频上,用频谱仪观测得到频谱图如图7所示。

图7 多通道调制器频谱图(截图)

通过对每路DTMB信号进行解调,MER正常,解调正常,接收图像无马赛克。该设计测试通过。图8为五路解调端星座图(调制方式分别为16QAM,QPSK和64QAM)。

从频谱图和解调端星座图可以看出,本文设计的五通道DTMB调制器很好地满足了设计要求。与采用5台独立调制器在射频频段进行合并的传统方案相比,本设计在数字域完成对多路调制器信号输出的合并,使用DDS模块产生所需低中频时钟,能够精确地控制搬移频点的时钟精度,有效减少相邻频段间的干扰。同时,整机只采用了1个DA芯片和正交调制芯片,所需硬件资源和整机功耗也大大减少,有效地提高了系统的稳定性。

4小结

本文以五通道调制器为例,详细介绍了多通道调制器的设计方案,通过对基带信号进行功率调整,上采样和低中频调制等一系列后处理,将多路基带信号成功合并为一路信号输出,极大地减少了DA和正交调制等芯片的使用,仅用1台多通道调制器即可完成农村

图8 五路解调端星座图(截图)

以及城市郊区地面数字电视基站的覆盖要求。经测试,本文设计的五通道调制器与5台独立调制器相比,在成本和功耗大大降低的同时,性能几乎无差异,具有很大的实用价值。

参考文献:

[1]杨知行. 地面数字电视国家标准DTMB技术解读[J]. 中国数字电视,2006(11):30-33.

[2]HE S S, TORKELSON M. FPGA implementation of FIR filters using pipelined bit-serial canonical signed digit multi-

pliers [J]. IEEE custom integrated circuits conference, 1994(5):81-84.

[3]卢莹莹,潘长勇,彭克武. 低复杂度可变带宽全数字调制器[J]. 清华大学学报(自然科学版),2009(8):1193-1196.

[4]PROAKIS J G. 数字通信[M]. 5版. 北京:电子工业出版社,2009.

责任编辑:闫雯雯

Implementation and design of DTMB multi-channel modulator

JIA Xuguang1, TONG Lu2, YANG Hui1, PAN Changyong1,2

(1.ResearchInstituteofInformationTechnology,TsinghuaUniversity,Beijing100084,China;2.NationalEngineeringLab.forDTV(Beijing),Beijing100191,China)

Abstract:In the construction of digital terrestrial TV broadcasting station, more than a couple of digital TV modulators are needed to meet the demands of broadcasting multiple SD and HD programs of coverage area. To simplify the construction of station and multiplex the hardware, this paper provides a solution of multi-channel digital TV modulator. Only one exciter is needed to fulfill the construction of the station. A five channel digital TV modulator is implemented on the FPGA as an example. The solution meets the design requirements by testing and has great practical value.

Key words:DTMB; modulator; multi-channel; FPGA

中图分类号:TN948

文献标志码:A

DOI:10.16280/j.videoe.2016.06.020

基金项目:质检公益性行业科研专项经费资助项目;科技部科技伙伴计划资助项目

收稿日期:2015-11-02

文献引用格式:贾旭光,佟璐,阳辉,等. DTMB多通道调制器的设计与实现[J].电视技术,2016,40(6):111-114.

JIA X G, TONG L, YANG H, et al. Implementation and design of DTMB multi-channel modulator [J].Video engineering,2016,40(6):111-114.