FPGA模型设计与手写代码资源效率的研究*

2016-07-05邢玉磊

邢玉磊,赵 刚

(四川大学 电子信息学院,四川 成都 610065)

FPGA模型设计与手写代码资源效率的研究*

邢玉磊,赵刚

(四川大学 电子信息学院,四川 成都 610065)

摘要:为了进一步研究FPGA开发工具DSP Builder基于模型设计的实用性。通过两种方法创建了基于M序列的2ASK调制解调系统:一种是在DSP Builder中利用模块进行建模的方法,通过自动生成HDL代码,下载到由南京润众科技有限公司提供的RZ8681现代通信技术试验平台上的FPGA硬件仿真模块中,并由安捷伦示波器测出了系统中的信号,对建模过程中的硬件资源利用率进行了记录;另一种通过手写VHDL代码实现了该系统,也记录了系统编译后所消耗的资源。对比两种方法,得出了基于DSP Builder的模型设计可以很好地提高在FPGA上开发DSP的效能,是一种很实用的工具。

关键词:DSP Builder;二进制幅移键控;M序列;现场可编程门阵列;手写代码;资源效率

0引言

随着电子系统设计的飞速发展,FPGA开发人员难免在系统设计中面临一系列的开发瓶颈。只有掌握了先进的设计思想与开发工具,才能在激烈的市场竞争中赢得先机。传统手工作坊式的开发模式已很难适应目前产品的大代码量、快速上市与可靠性等的要求。为了解决这些问题,把可视化的基于模型设计思想引入到FPGA的应用研究之中,在国外已深入人心,并得到广泛的应用。Altera公司为了适应这种新技术浪潮,也实时推出并持续升级了自己的基于模型设计产品—DSP Builder工具。该工具通过整合MATLAB、Simulink等系统级开发工具,利用VHDL和Verilog HDL语言的设计流程,随着算法的进步,它可以提供一个友好的DSP设计环境,快速创建硬件仿真,缩短开发周期。特别地采用DSP Builder高级模块库后,让Altera工具、IP核、第三方工具能更好地无缝连接,代码的RTL级验证与QuartusⅡ工程的生成只是点一下鼠标的事情,这既节约了时间还降低了开发成本和风险。然而在国内外的网络[1]上普遍流传着采用基于模型设计所生成的HDL代码占用资源较多的传闻,本文通过实验验证了此问题。

1基于DSP Builder 的2ASK算法实现

1.12ASK系统原理

调制信号为二进制数字信号时,这种调制成为二进制数字调制。在2ASK中,载波的幅度只有两种变化状态,即用数字信息“0”或“1”的基带矩形脉冲去键控一个连续的载波,使其间断输出。“1”表示有载波输出,“0”表示无载波输出,它是研究其他数字调制技术的基础[2]。

(2)ASK时域表达式为:

e2ASK(t)=a(t)cosωct

(1)

式中,ωc为载波角频率,a(t)为单极性NRZ矩形脉冲序列,其表达式为:

(2)

式中,g(t)是持续时间为Tb、幅度为1的矩形脉冲,常称为门函数;an为需要传输的二进制数字,可表示为

(3)

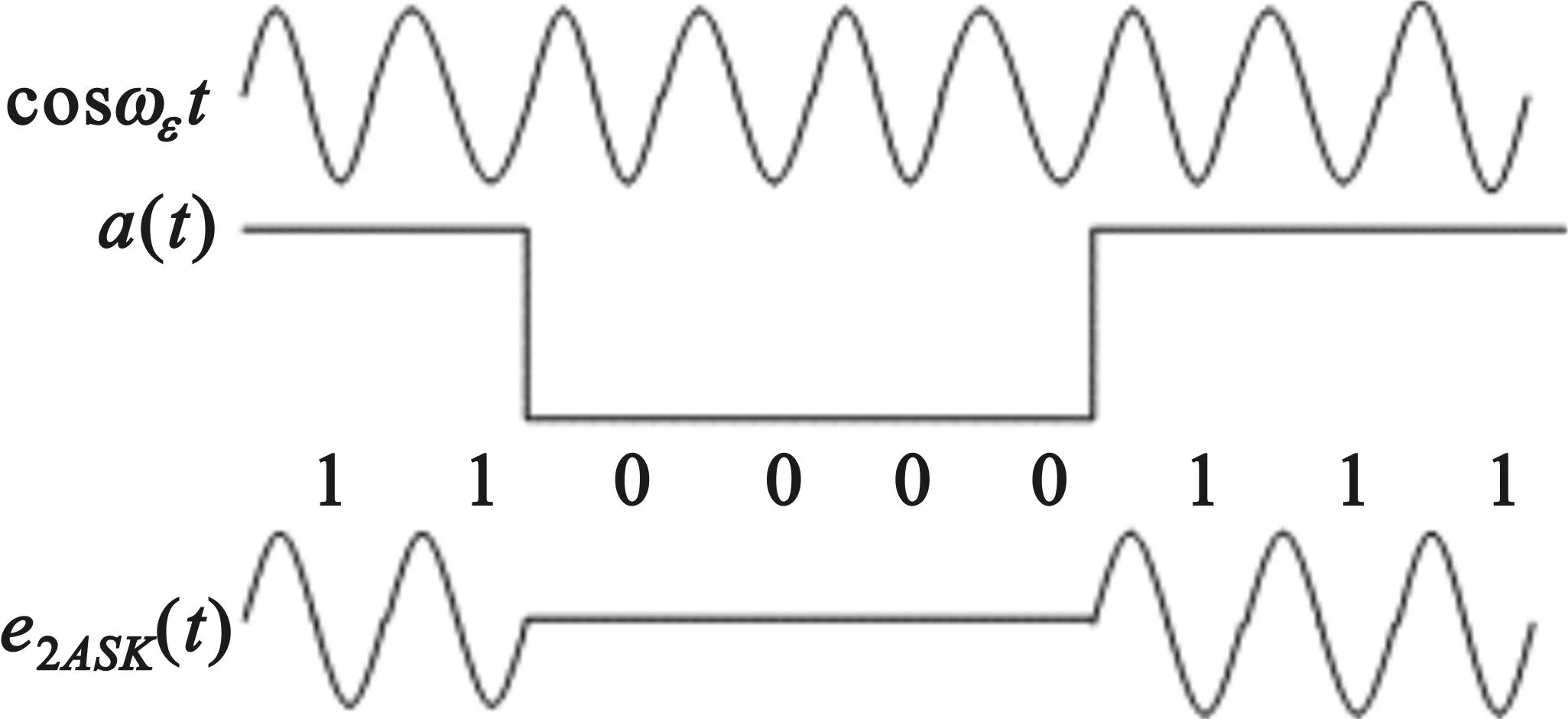

cosωct、a(t)和e2ASK(t) 的波形示例图如图1 所示,通过载波幅度变化作为控制信息,频率和初始相位不变[3]。

图1 载波、矩形脉冲和2ASK波形示例

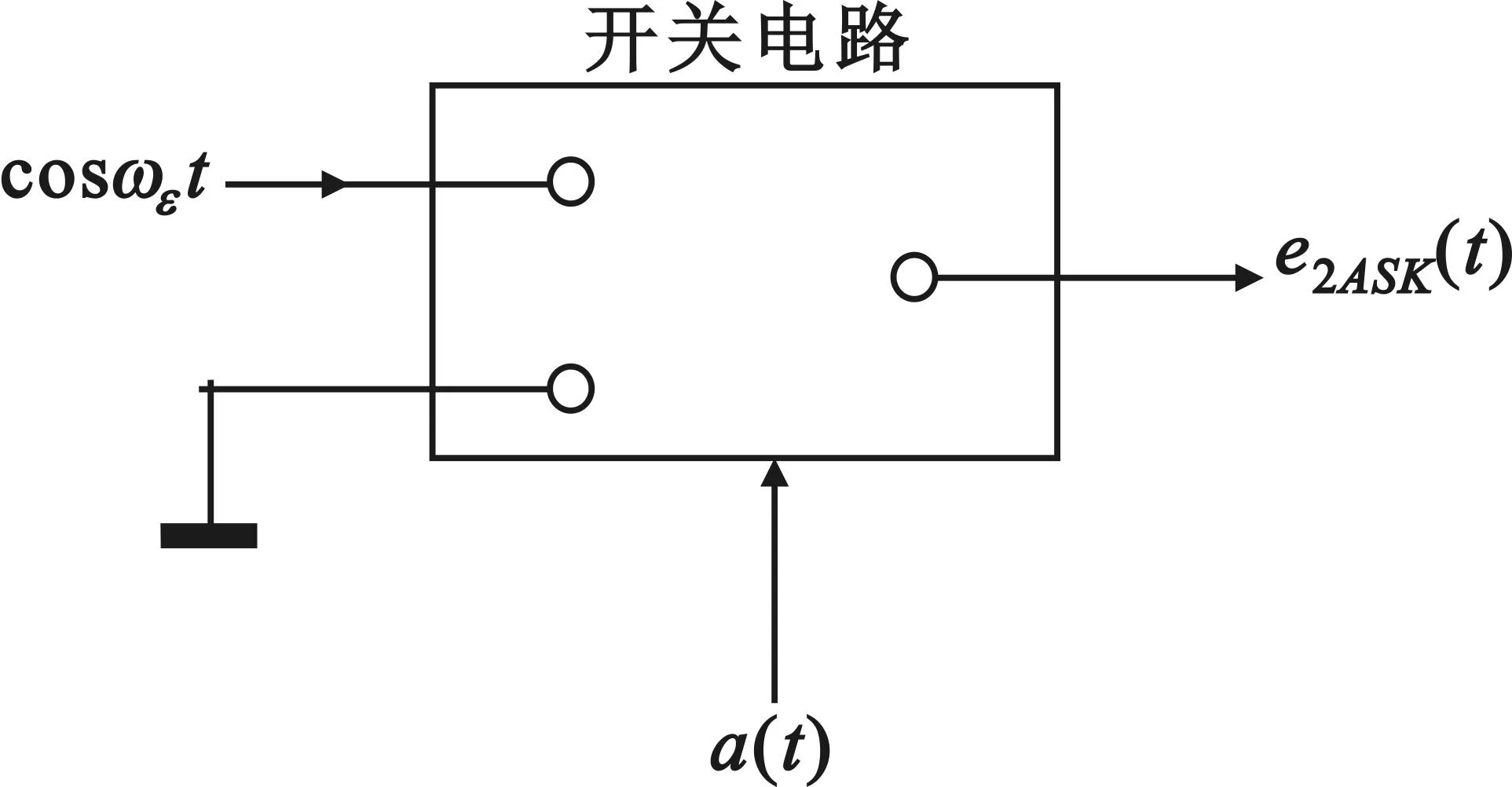

2ASK信号的实现方式有两种,模拟相乘法和数字键控法,本文采用键控法实现。数字键控法就是用开关电路控制输出调制信号,当开关接载波就有信号输出,当开关接地就没信号输出,其电路如图2所示。

图2 2ASK键控法

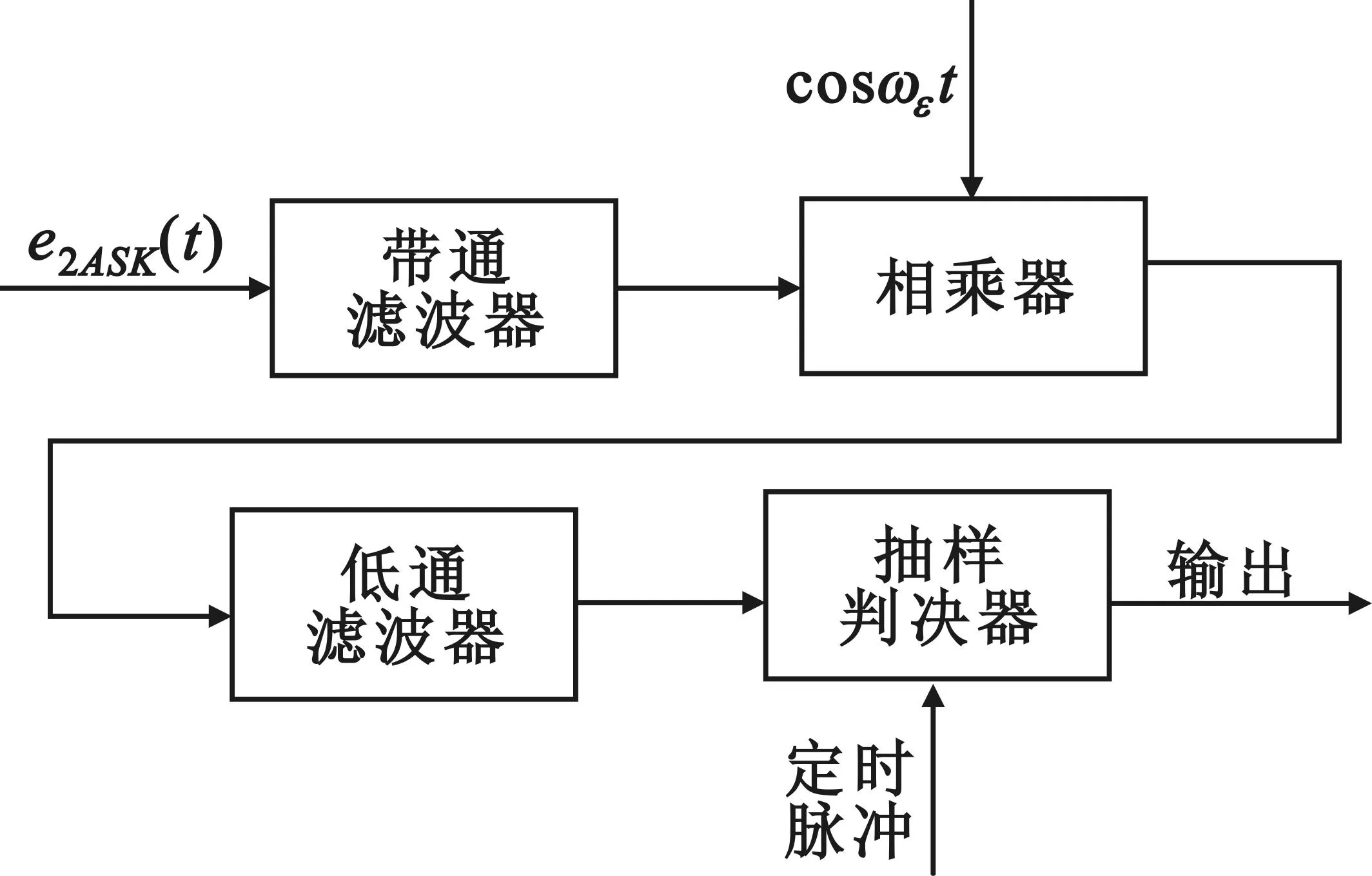

2ASK的解调方法有两种,相干解调法和非相干解调法,本文采用相干解调法。相干解调的检测器组成原理如图3所示,输入信号与相干载波在乘法器中相乘,然后由低通滤波器滤出基带波形,最后通过抽样判决器恢复出基带数据。判决输出需要位同步脉冲,有利于提高数字信号接收性能[4]。

图3 相干解调法

1.2M序列产生的原理

M序列是最长线性反馈移位寄存器序列,是一种常用的二元伪随机序列。它可由线性反馈移位寄存器生成。主要有3种特性:平衡性、游程特性和相关性。它的统计特性与白噪声的统计特性相似。

由于M序列自身具有的多种抗噪声特性,使得经过这种编码方式的信号可以在接收端方便地将信道传输过程中所加入的随机噪声信号滤除,准确地恢复出原始信号,从而在无线通信中有很强的抗干扰能力[5]。由于具有该特性,因此在通信中具有广泛的用途,例如在扩频通信中的加密、扰码、同步等。

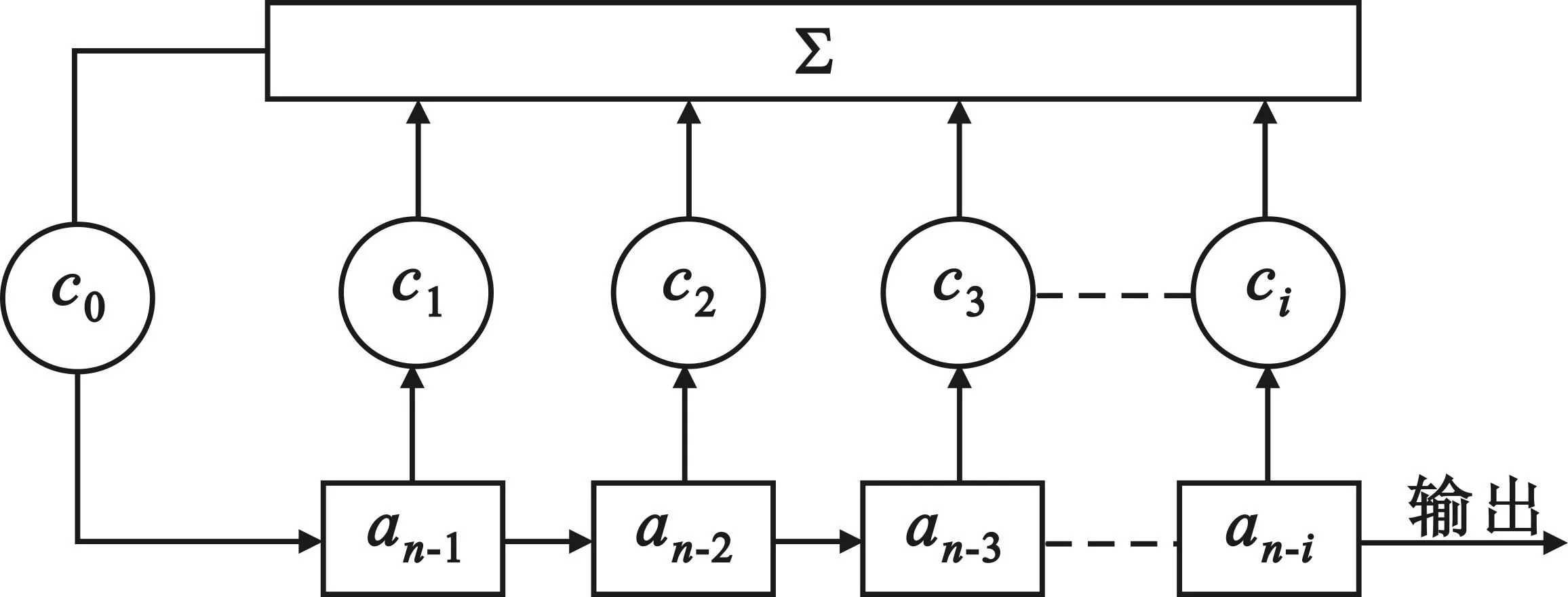

M序列的产生比较简单,可以利用n级移位寄存器产生,图4为简单序列发生器。利用D触发器级联的方式就可以完成移位寄存器的功能,即可实现M序列产生器的设计。在时钟触发下,每次移位后各级寄存器状态会发生变化[6]。其中任何一级寄存器的输出,随着时钟节拍的推移都会产生一个序列。其中an-i为移位寄存器中每位寄存器的状态,ci为第i位寄存器的反馈系数。ci=1表示有反馈,ci=0表示无反馈。

图4 反馈移位寄存器的结构

图5为一个四级反馈移存器[7]。若其初始状态为(a3,a2,a1,a0)=(1,0,0,0),则移位一次时,由a3和a0模2相加产生新的输入a4=1⊕0=1新的状态变为(a4,a3,a2,a1)=(1,1,0,0),这样移位15次后又回到初始状态(1,0,0,0)。

图5 四级反馈移存器

随着移位时钟节拍,各级移位寄存器的状态转移流程如表1所示。由表1可以看出,对于n=4的移位寄存器共有24=16种不同的状态。

表1 M序列发生器状态转换

若初始状态为全“0”,即(0,0,0,0),则移位后得到的仍为全“0”状态。在实际的系统设计中,当系统清零后,D触发器输出状态均为低电平,在“模二加”运算后添加“非门”可以避免输出全“0”信号。所以除了全“0”状态外,4级移位寄存器只有15种可用状态。即由任何4级反馈移位寄存器可以产生周期最长为15的序列。一个n级反馈移位寄存器产生的最长周期等于2n-1。这种最长的序列称为最长线性反馈移位寄存器序列,简称M序列。

1.3基于模型的2ASK调制解调实现

利用MATLAB/Simulink工具箱中的DSP Builder定点库对系统建模仿真,可以自动生成VHDL代码。它的设计流程一般为:(1)利用Altera库及与之对应的Simulink库建立系统模型。在建立模型时,只需将库中的模型直接拉到Simulink中,之后对这些模块进行参数化。(2)在Simulink中进行仿真。建立模型后,直接在Simulink中仿真,仿真输入信号源及输出结果均以图形化表示,用户可以直观地看到效果。(3)添加Signal Complier模块到模型中,产生HDL代码。在得到VHDL文件后,通过对产生的VHDL文件进行自动流程综合、编译、仿真和配置下载等操作[8],可以快速完成设计。

DSP Builder自动流程可以自动调用QuartusⅡ等EDA软件,完成综合、网络表生成和QuartusⅡ适配,并完成对FPGA的配置下载过程[9]。整个流程中用户都需要进行仿真,仿真包括Simulink仿真以及HDL代码仿真。前者的仿真保证了模型功能的正确,使后续步骤有意义,后者的仿真可以验证系统功能的正确性。

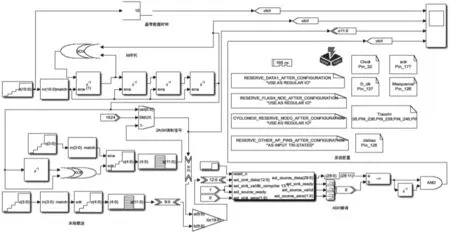

2ASK调制解调系统的DSP Builder电路模型如图6所示。系统的主时钟周期为100 ns,频率为10 MHz;其中M序列部分是15位的二进制序列“111101011001000”, 基带数据时钟为32 kHz;产生正弦载波模块的查找表参数配置为:查找表地址为5位(25=32),表中数值为12位,查找表具体数值为(sin(2*pi/2^5:2*pi/2^5:2*pi)+1)*1023),式中之所以取5,是因为总线是5位,填其他数将不会产生正弦波[10];低通滤波器采用在速度、性能等方面都已得到优化的Altera的IP核,采用布莱克曼窗函数法[11],采样频率为500 kHz。系统配置部分由Quartus II Global Project Assignments控件和QuartusII Pinout Assignment控件组成,通过参数配置,可以使系统从建模到芯片下载实现在一个开发环境下完成,而无需另单独在Quartus II软件中进行引脚配置和下载[12]。

图6 2ASK电路模型

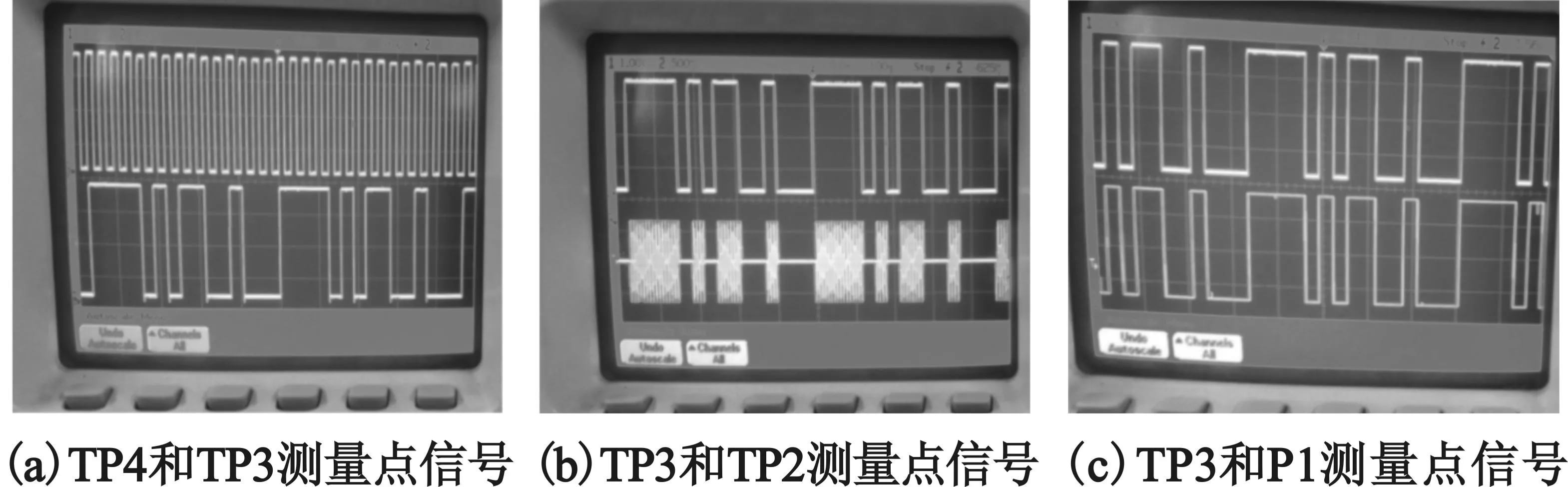

图7 各测量点信号波形

在Simulink环境下对所建系统模型进行仿真后,结果符合预期的效果。然后双击仿真系统中Signal Compiler控件,选择CycloneⅢ EP3C40Q240C8芯片按照步骤完成编译、连接和编程的操作过程,然后在开发板上用安捷伦示波器观测TP4、TP3、TP2和P1测量点的输出波形。其结果如图7所示,其中图(a)为基带数据时钟信号和基带M序列信号,图(b)为基带M序列信号和2ASK调制信号,图(c)为基带M序列信号和2ASK解调信号,且解调出来的信号局部产生了吉布斯现象。

2模型设计与手工代码结果比较

经过传统手工方式编写了2ASK调制解调系统的代码,其中M序列代码量22行,2ASK调制信号产生模块代码量(含载波信号)183行,解调端判决器模块(含FIR滤波器、比较器)153行,解调顶层模块56行,手工代码2ASK总代码量约414行。基于DSP Builder建模设计的2ASK调制解调系统产生的代码量大于4 500行,通过QuartusⅡ13.1编译[13]后两种途径资源利用率和最大频率比较结果如表2所示。

在《基于模型的设计——Qsys篇》一书中,作者通过流水灯实验也得出了类似的结论,手写代码21行,系统综合后占用资源41个LE,Fmax=87 MHz,建模生成的代码大于220行,综合后占用资源36个LE,Fmax=77 MHz。

表2 2ASK手写代码与建模实现编译结果对比

3结语

通过实验结果可以看出,表面上自动代码的长度远远超过手写代码的长度,但综合后的结果令人满意。说明建模代码不论在资源占用上,还是在最大频率上,都可以和手写代码媲美,模型代码已经接近手写代码的水平。对于大型项目,模型代码超过手写代码所占用的资源将成为可能,基于模型设计开发FPGA的方法可以走向实用阶段。这将大大压缩开发周期和降低开发成本,使推出的新产品具有竞争优势。

参考文献:

[1]刘杰.基于模型的设计—Qsys篇[M]. 北京:机械工业出版社,2012.

LIU Jie. Model-based Design—Qsys[M]. Beijing: China Machine Press, 2012.

[2]达新宇,陈树新,王瑜.通信原理教程[M]. 北京:北京邮电大学出版社,2012.

DA Xin-yu,CHEN Shu-xin,WANG Yu.Communication Theory Tutorial [M].Beijing: Beijing University Posts And Telecommunications Press,2012.

[3]王晓玲. 基于MATLAB/Simulink的2ASK传输系统设计与分析[J]. 苏州市职业大学学报,2015,26(04):10-13. WANG Xiao-ling. Design and Analysis of 2ASK Transmission System Based on MATLAB/Simulink [J]. Journal of Suzhou Vocational University,2015,26(04):10-13.

[4]程钦,潘玲佼,任艳玲.一种伪随机控制的2ASK调制解调电路实现[J].江苏理工学院学报,2014,2 (06):51-55.

CHENG Qin, PAN Ling-jiao, REN Yan-ling. Pseudo Random Control 2ASK Modem Circuits[J]. Journal of Jiangsu University of Technology,2014,2(06):51-55.

[5]CAI Guang-hui, ZHU Ruo-xin, LI Wen-long. A Design of Direct Sequence Spread Spectrum Module with Variable Bandwidth based on FPGA[J]. Applied Mechanics and Materials, 2014, 513(517): 3332-3335.

[6]孟倩,沈忠华,陈克非.由GF(q)生成扩域上m序列的方法及在WG序列中的应用[J]. 密码学报,2015,2(06):515-525.

MENG Qian, SHEN Zhong-hua, CHEN Ke-fei. A Method of Generating M-Sequences over GF(qn) from GF(q) and the Application in WG Sequence[J]. Journal of Cryptologic Research, 2015, 2(06):515-525.

[7]潘晓英. 基于线性反馈移位寄存器和分组密码的伪随机数生成方法[J]. 通信技术,2015,48(02):228-231.

PAN Xiao-ying. Pseudo-Random Number Generation Algorithm based on Linear Feedback Shift Register and Block Cipher [J].Communications Technology, 2015,48(02):228-231.

[8]付莉,高兴泉. 基于DSP Builder的电子技术仿真实验平台[J]. 实验技术与管理,2015(01):134-137.

FU Li,GAO Xing-quan. Simulation Experimental Platform for Electronic Technology Course based on DSP Builder [J]. Experimental Technology and Management, 2015(01):134-137.

[9]赵刚,张垒,路明.计算机系统的自主设计[M]. 北京:电子工业出版社,2011.

ZHAO Gang, ZHANG Lei, LU Ming. Self-Designed Computer System[M]. Beijing: Publishing House of Electronics Industry,2011.

[10]李鹏飞,李金平,陆小菊.基于Matlab与DSP Builder的2PSK调制解调器设计与仿真[J]. 计算机科学,2012,39(10):33-35.

LI Peng-fei, LI Jin-ping, LU Xiao-ju.Design and Simulation of Modem based on Matlab and DSP Builder[J].Computer Science,2012,39(10):33-35.

[11]Altera Corporation. FIR Compiler User Guide. [EB/OL](2013-11-19)[2016-02-11]. http://www.altera.com/content/dam/literature/ug/fircompiler_ug.pdf.

[12]Altera Corporation. DSP Builder Guide Volume 2. [EB/OL](2014-07-12)[2016-02-11]. http://www.altera.com/literature/ug/ug_dsp_builider.pdf.

[13]张凤娟,盛利元,刘洋洋. 基于DSP Builder的移相键控调制解调系统设计[J].微电子学,2013,43(01):37-46.

ZHANG Feng-juan,CHENG Li-yuan,LIU Yang-yang. Design of PSK Modulation/ Demodulation System based on DSP Builder [J]. Microelectronics, 2013, 43(01):37-46.

FPGA Model Design and Resource Efficiency of Handwritten Code

XING Yu-lei, ZHAO Gang

(College of Electronics and Information Engineering, Sichuan University,Chengdu Sichuan 610065,China)

Abstract:To further investigate the practicality of FPGA development tools by DSP Builder based on model design, 2ASK modem system based on the M sequence is constructed in two methods. And for one method,the module in the DSP Builder is used to anstruct the model, through automatically generating HDL code, and downloaded into FPGA hardware simulation module on RZ8681, a modern communication technology test platform provided by Nanjing Runzhong Sci. &Tech. Co., Ltd. The signal of the system is measured with Agilent oscilloscope,and the utilization of hardware resource in the modeling process also recorded. For the other method 2ASK modem system is implemented by writing VHDL code, and the resource comsumption after compiling also recorded. The comparison of these two methods indicates the model design based on DSP Builder could improve the effectiveness of DSP development on FPGA,and this model is a very practical tool.

Key words:DSP Builder; 2ASK; M sequence; FPGA; handwritten code; resource efficiency

doi:10.3969/j.issn.1002-0802.2016.04.024

*收稿日期:2015-11-01;修回日期:2016-03-05Received date:2015-11-01;Revised date:2016-03-05

中图分类号:TN311

文献标志码:A

文章编号:1002-0802(2016)04-0504-05

作者简介:

邢玉磊(1988—),男,硕士研究生,主要研究方向为基于FPGA的信号处理;

赵刚(1962—),男,教授,硕士生导师,主要研究方向为电路与系统设计自动化、扩频通信。