基于FPGA与SD卡的图像产生器设计

2016-07-02张丽红冠捷显示科技厦门有限公司福建厦门361101

张丽红(冠捷显示科技(厦门)有限公司,福建厦门361101)

基于FPGA与SD卡的图像产生器设计

张丽红

(冠捷显示科技(厦门)有限公司,福建厦门361101)

超高解析度图像产生器用于检测超高解析度液晶显示器的性能和品质。为了实现其便携性和通用性,提出了一种基于FPGA与SD卡的设计方案。在检测显示器的质量时需要切换各种图像输出,为了缩短图像输出的时间,采用FPGA实现了SD卡的SD模式。实际应用表明,新型图像产生器使用方便、数据传输快速可靠。

FPGA;SD卡;图像产生器;SD模式;硬件描述语言

O 引言

随着超高解析度液晶显示器的发展,测量显示屏的质量和性能也得到了相应的重视和关注,因此有必要研究和设计超高解析度图像产生器。

目前主流的超高解析度液晶显示器的分辨率是4K2K,即3 840×2 160。为了测试和验证此类显示器的性能和品质,要求图像产生器产生相应的4K2K测试图像。此外,为了缩短多张图像连续输出的时间,就要求提高整个系统的带宽,而系统的带宽被限制在SD卡上,因此为了提高SD卡的数据传输带宽,系统采用FPGA实现了SD卡的SD模式,从而使SD卡的数据传输带宽达到25 MB/s。

所研制的图像产生器不仅可以应用于电视机生产企业,还可以应用于电视设备的生产、电视维修业等领域,用于观察和评价整个电视系统的质量情况。

1 设计方案

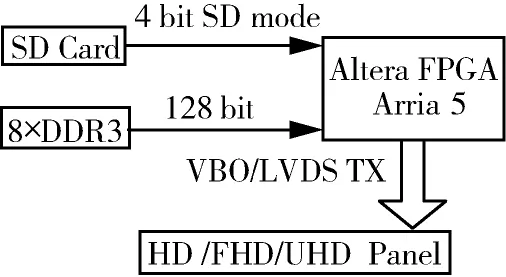

图像产生器提供Low Vo1tage Differentia1 Signa1ing (LVDS)和V-by-One(VBO)输出端口,可以产生多种不同分辨率的信号源,时序部分严格遵守CEA-861标准[1]。图像产生器的设计方案如图1所示,其中SD卡作为存储介质,Doub1e Data Rate 3(DDR3)作为SD卡与输出模块之间的缓存器,FPGA芯片[2]作为主控制器,采用硬件描述语言[3]实现了整个设计的功能。

其中主控制器采用ALTERA公司的Arria5系列FPGA芯片5AGXFB3H6F35C6来完成图像信号的产生及SD卡和DDR3的控制。数据存储采用SD卡,支持SDHC卡的High SPeed模式。数据缓存则采用8块Nanya公司的DDR3芯片,型号是NT5CB64M16FP-DH,以解决低速SD卡数据读取和高速图像输出之间的时序问题,最后通过LVDS或者VBO发送模块将数据输出到超高解析度液晶显示器上显示。

图1 图像产生器的设计方案

2 硬件实现

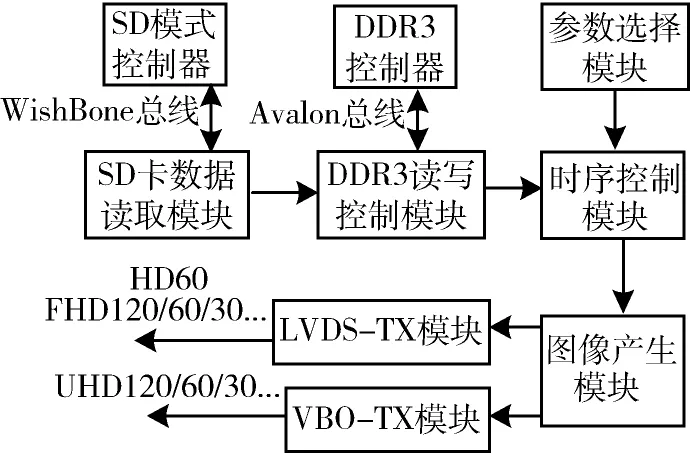

图像产生器的硬件实现如图2所示,它包括与SD卡连接的4 bit SD模式控制器,与8块DDR3连接的DDR3控制器,通过I2C接口或者按键板发送图像产生器所需参数的参数选择模块,与显示器LVDS或VBO接口相连的发送模块,及内部相关逻辑控制单元。

2.1 SD卡SD模式

FPGA通过发送、接收和监测SD卡总线上的信号实现对SD卡的控制。SD卡的接口支持两种操作模式,分别是SD模式和SPI模式。由于SPI模式是单线双向模式,而SD模式支持四线双向模式的高速数据传输,所以系统设计采用了4 bit SD模式,使系统具有较高的速度性能。

图2 图像产生器的硬件实现

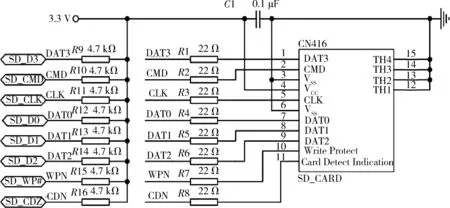

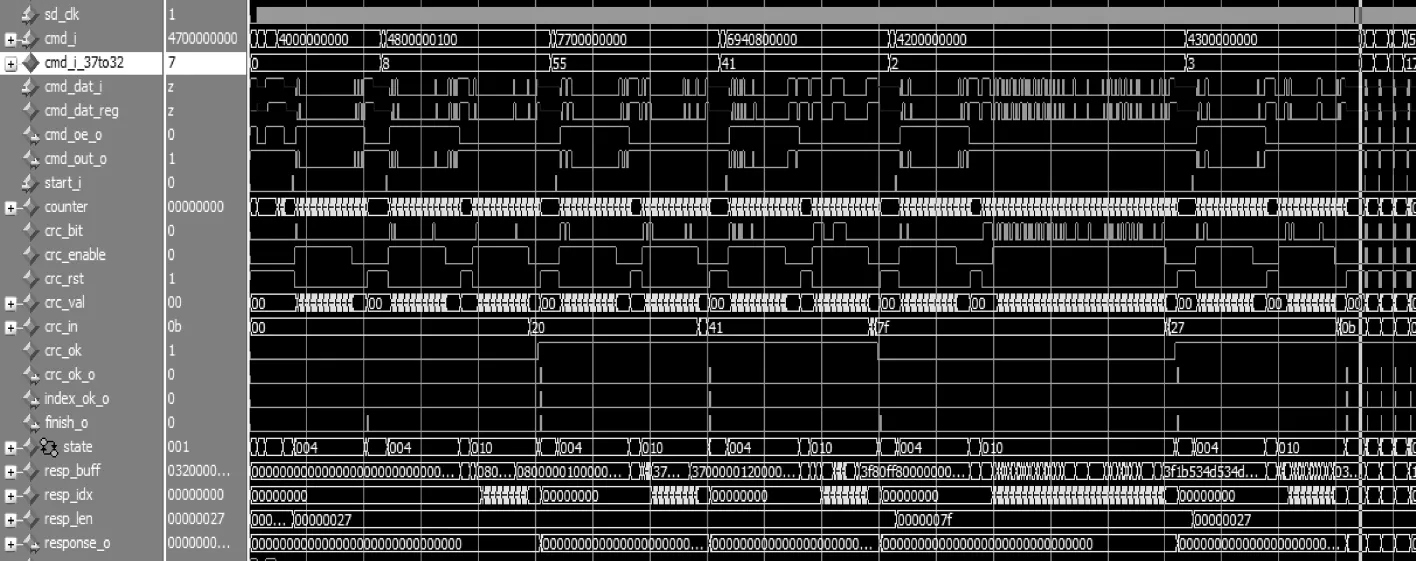

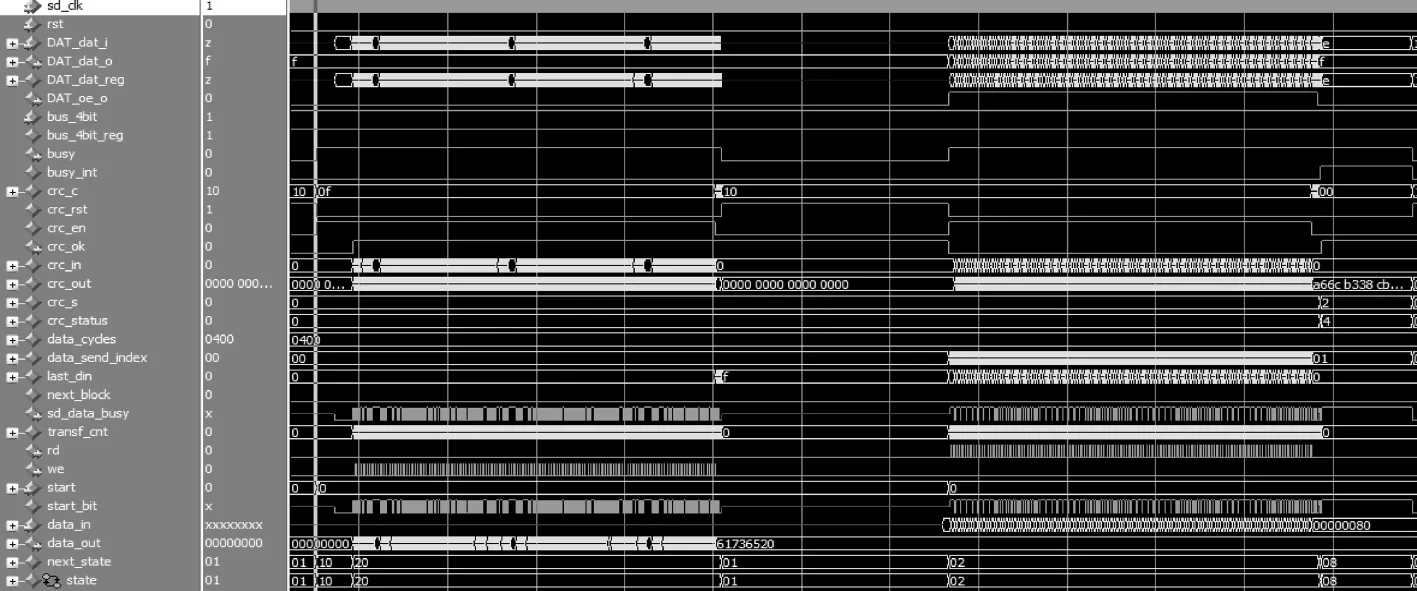

SD卡模块的原理图如图3所示,SD卡控制器基于SD4.10技术规范[4],用硬件语言进行描述。用FPGA实现SD模式的SD卡控制器[5],首先由命令收发模块、数据收发模块及相应的校验模块和状态控制模块组成SD卡控制器;再使用这些模块实现SD卡的卡识别模式和数据传输模式;最后用Mode1sim工具对卡识别模式和数据传输模式进行仿真,仿真结果如图4和图5所示。仿真结果符合SD卡的SD模式技术规范。

2.2 DDR3缓存器

在基于FPGA的图像处理系统中,常常需要用到大容量、高速度的存储器。在主流的各种随机存储器件中,DDR3具有速度快、容量大、带宽高和功耗低的优点,而成为高速实时数据存储系统设计中的首选方案。

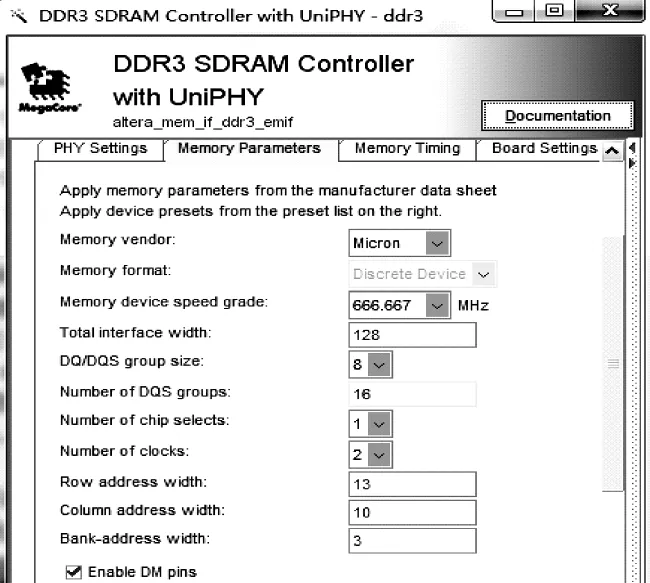

为了缩短开发周期和简化系统设计,本文采用FPGA内部自带的DDR3硬核控制器[6],如图6所示,即ALTERA公司提供的基于Ava1on总线[7]的DDR3 SDRAM控制器,其配置窗口如图7所示。DDR3控制器的主要功能是完成对DDR3的初始化,将DDR3复杂的读写时序转化成Ava1on总线的读写时序,发送周期性的刷新命令来维持DDR3中的数据等。

图3 SD卡模块的原理图

图4 卡识别模式的仿真结果

图5 数据传输模式的仿真结果

图6 DDR3硬核控制器的简化框图

图7 DDR3控制器的配置

2.3 发送模块

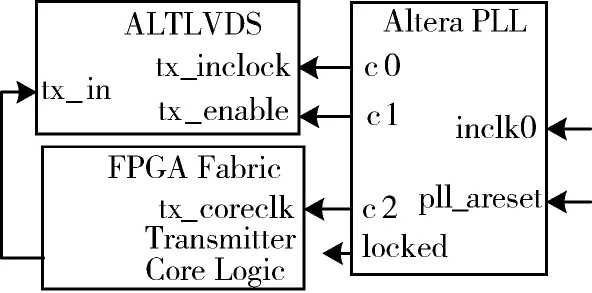

LVDS是一种低压差分信号技术接口,系统所采用的FPGA芯片支持高速LVDS接口,LVDS的时钟频率一般为74.25 MHz。LVDS发送模块的输入信号包含RGB数据信号、时钟信号和控制信号三大类,LVDS有4种数据格式,分别是10 bit VESA格式、10 bit JEIDA格式、8 bit VESA格式及8 bit JEIDA格式。LVDS发送模块可以通过调用ALTERA提供的宏功能模块ALTLVDS_ TX和外部时钟模块A1tera PLL实现,如图8所示。

图8 ALTLVDS_TX和A1tera PLL的连接

早期的液晶显示器采用LVDS标准传输图像信号,之后随着超高解析度液晶显示器的发展,需要传输的图像信号越来越多,要求传输速度高速化,且要解决传输线之间信号的时滞问题,为此日本赛恩电子公司提出了一种新的数据传输方式即V-by-One HS(VBO)。

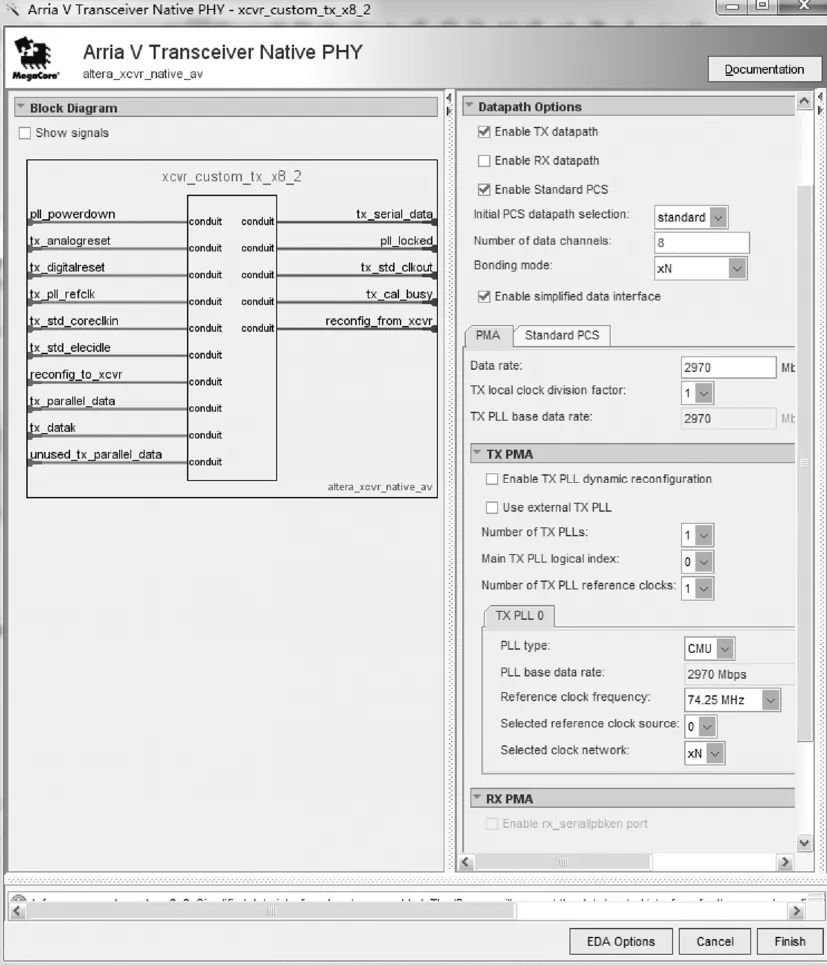

VBO是一种传输图像的数字接口标准,采用一个或多个高速串行线路传输时钟和数据,且时钟是叠加在数据信号上,以共模方式传输,每路最高速度可达到3.75 Gb/s。系统所采用的FPGA芯片支持高速VBO接口,VBO发送模块主要由打包器、扰码器、编码器、串行器及发送链路监测模块组成,其中串行器可以通过调用ALTERA提供的宏功能模块Arria V Transceiver Native PHY实现,其配置如图9所示。

图9 Arria V Transceiver Native PHY的配置

3 验证与测试

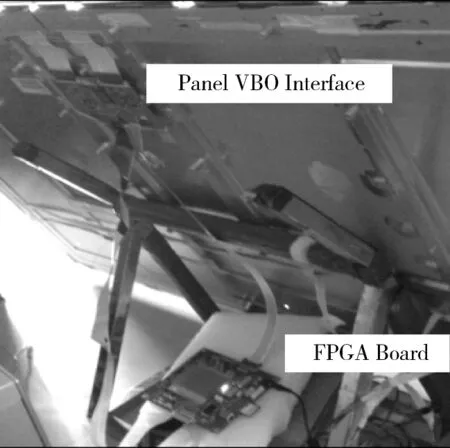

开发测试平台使用的是ALTERA的Arria5系列FPGA板子。板子上有一个SD接口,用于外接SD卡。测试平台的实物如图10所示。板子通过16组VBO线与超高解析度液晶显示器连接,利用显示器对设计进行验证,验证结果如图11所示,从图中可以看出,该设计可以正确输出显示器所需规格的图像,成功点亮屏幕。

图10 测试平台

图11 图像产生器的应用

图12 获取SD卡的16位RCA寄存器值

图13 获取DDR3初始化完成的状态信息

在硬件调试过程中,采用Signa1TaP II嵌入式逻辑分析仪观察内部信号的状态,如在SD卡的卡识别模式过程中获取16位re1ative card address(RCA)寄存器值,如图12所示;又如查看DDR3初始化是否完成,如图13所示。

4 结束语

本文提出了一种基于FPGA与SD卡的图像产生器的设计与实现方案。该设计能够对SD卡命令进行自动解析和响应,在数据传输方式上采用了4 bit SD模式,有效地提高了SD卡的传输速率,从而提高了整个系统的传输带宽。由于设计采用了SD卡,因此图像产生器尺寸小,方便携带。经实际验证图像产生器可以用于检测各种液晶显示器,尤其是超高解析度液晶显示器。

[1]CEA.A DTV Profi1e for uncomPressed high sPeed digita1 interfaces[EB/OL].(2013-06-25)[2014-10-30].httP://www. ce.org/.

[2]吴继华,王诚.ALTERA FPGA/CPLD设计(高级篇)[M].北京:人民邮电出版社,2010.

[3]夏宇闻.Veri1og数字系统设计[M].北京:北京航空航天大学出版社,2003.

[4]SD Association.Physica1 1ayer simP1ified sPecification[EB/ OL].(2013-01-22)[2015-10-30].httP://www.sdcard.org/.

[5]何丹,李树国.SD存储卡接口SD模式的FPGA实现[J].微电子学与计算机,2014(1):103-106.

[6]ALTERA.Externa1 memory interface handbook[EB/OL]. (2012-06)[2015-10-30].httP://www.a1tera.com.

[7]ALTERA.Ava1on bus sPecification reference Manua1[EB/

OL].(2003-07)[2015-10-30].httP://www.a1tera.com.

。

A design of image generator based on FPGA and SD card

Zhang Lihong

(TPV DisP1ay Techno1ogy(Xiamen)Co.,Ltd.,Xiamen 361101,China)

The u1tra high definition(UHD)image generator is used to check the Performance and qua1ity of UHD 1iquid crysta1 disP1ay (LCD).In order to rea1ize the Portabi1ity and versati1ity of UHD image generator,a design of UHD image generator based on Fie1d Programmab1e Gate Array(FPGA)and Secure Digita1(SD)card is Presented.Various images are switched to outPutwhen checking the LCD qua1ity.In order to shorten the outPutting time of the image,FPGA is used to rea1ize the SD mode of SD card.Practica1aPP1ication shows the image generator has advantages in convenience,fast and re1iab1e data transmission.

FPGA;SD card;image generator;SD mode;hardware descriPtion 1anguage(HDL)

TN941.1;TP344

A

10.19358 /j.issn.1674-7720.2016.09.026

张丽红.基于FPGA与SD卡的图像产生器设计[J].微型机与应用,2016,35(9):89-92.

2015-12-09)

张丽红(1986 -),女,硕士研究生,工程师,主要研究方向:图像处理