一种通用卫星通信调制解调模块的设计*

2016-07-01徐远超

徐远超

(中国电子科技集团公司第十研究所,四川 成都 610036)

一种通用卫星通信调制解调模块的设计*

徐远超

(中国电子科技集团公司第十研究所,四川 成都 610036)

摘要:为了研制一种可供多种卫星通信设备使用的基带处理模块,采用模块化设计和数字化设计的方法,设计了一种通用的、宽带数字调制解调模块。该产品在一个通用的硬件平台上实现了扩频码钟为3~4 Mc/s、信息速率为2.4~9.6 kb/s的扩频信号解调,以及信息速率为0.5~110 Mb/s的宽带信号BPSK、QPSK调制,根据速率和编译码方式及调制体制可配置为4种工作模式,且工作模式可通过监控指令控制切换。经过工程应用表明,该模块通过加载不同的FPGA程序,完全可以适应多个卫星通信设备的基带处理需求,是一个通用的产品。

关键词:卫星通信;数字调制解调;宽带;通用

0引言

卫星通信由于覆盖范围广、可用频段宽、便于机动、对通信距离不敏感等特点[1],近些年得到迅猛发展。随着卫星通信设备通用化及高速数据传输需求的提出,宽带数字调制解调已经成为了发展的趋势。采用数字调制解调,可以减少模拟器件的使用,提高产品的可靠性、稳定性和灵活性;且可以在一个通用的硬件平台上实现调制解调速率、编译码方式、调制解调体制等参数的任意组合,进而减少重复设计,缩短产品的生产研发周期,降低成本。

本文主要介绍一种卫星通信数字解调及宽带调制模块。该模块主要用于卫星通信中,包含前向解调和返向调制两部分,前向遥控解调完成前向信号的捕获、跟踪、译码等功能,最后输出解调数据;而返向调制主要完成载荷数据的组帧、编码、调制等功能,输出L频段中频信号。主要参数如下:

(1)实现方式:FPGA+外围电路。

(2)中频频率:接收70 MHz,发射L频段。

(3)信息速率:接收2.4~9.6 kb/s,发射0.5~110 Mb/s。

(4)调制方式:接收BPSK(扩频),发射BPSK、QPSK。

(5)工作模式:4种。

4种工作模式对应的接收和发射的速率、扩频码及码钟、调制方式都可任意配置,工作时通过动态加载4种软件,并对相关软件模块的参数进行设置。

1基本原理

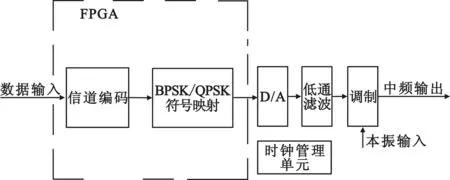

1.1调制部分原理框图

调制部分除了D/A变换、低通滤波和正交调制等必须使用的模拟器件外,所有的数字逻辑包括数据接口、组帧、信道编码、成型滤波、符号映射等都由FPGA实现。工作模式由软件控制,因此配置非常灵活。带宽变化时,FPGA内部程序及低通滤波器组件控制参数要相应变化。调制部分原理见图1。

图1 调制部分原理框

信道编码包括卷积编码、RS编码和LDPC编码,由外部指令控制编码方式选择。

对信息速率10 Mb/s以下采取了系数0.3的根升余弦成型滤波,由FPGA实现。高速的信息速率由于内插采样率要求较高,未成型滤波。

中频输出功率可通过指令调整,调整范围为-30~0 dBm,步进1 dB。

为了支持常用的中频频率,调制器设计为本振信号由外部输入,在电路板设计时考虑L频段的适应性。因此,只需要更改本振信号的频率即可实现发射中频频率的调整。在尺寸、重量、功耗允许的情况下,该模块上还可以加一个频综,产生工作需要的时钟和本振信号。

1.2解调部分原理框图

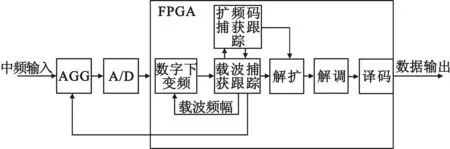

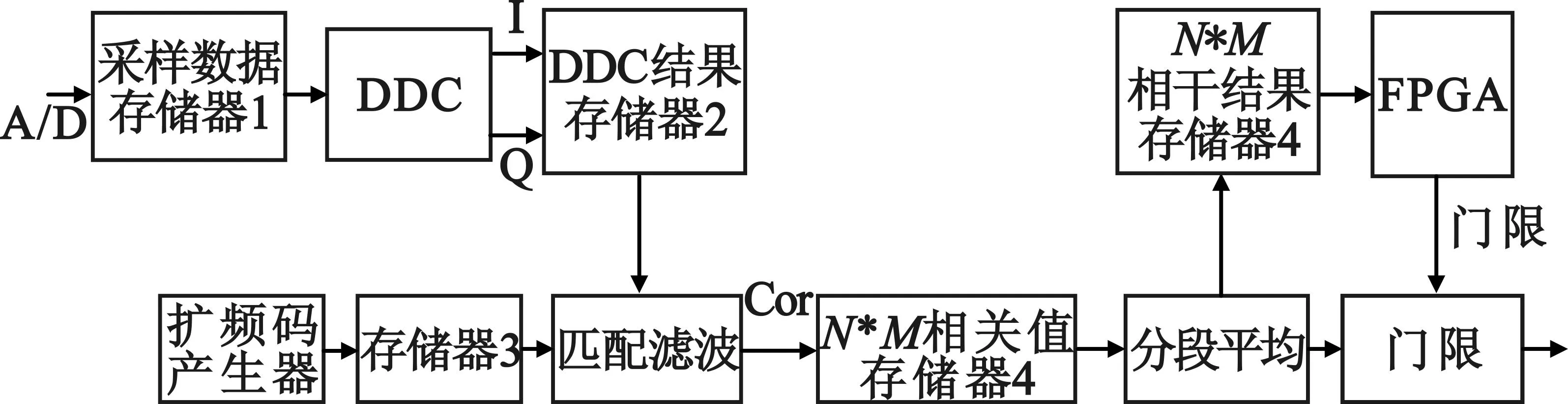

A/D采样后的信号处理算法全部由FPGA实现,A/D采样信号经正交数字下变频,扩频码捕获跟踪、载波捕获跟踪、解扩解调和译码,输出数据。可支持4 Mc/s扩频信号(最高9.6 kb/s数据速率)解扩解调。数据速率分档可设置。解调部分原理框见图2。

图2 解调部分原理框[2]

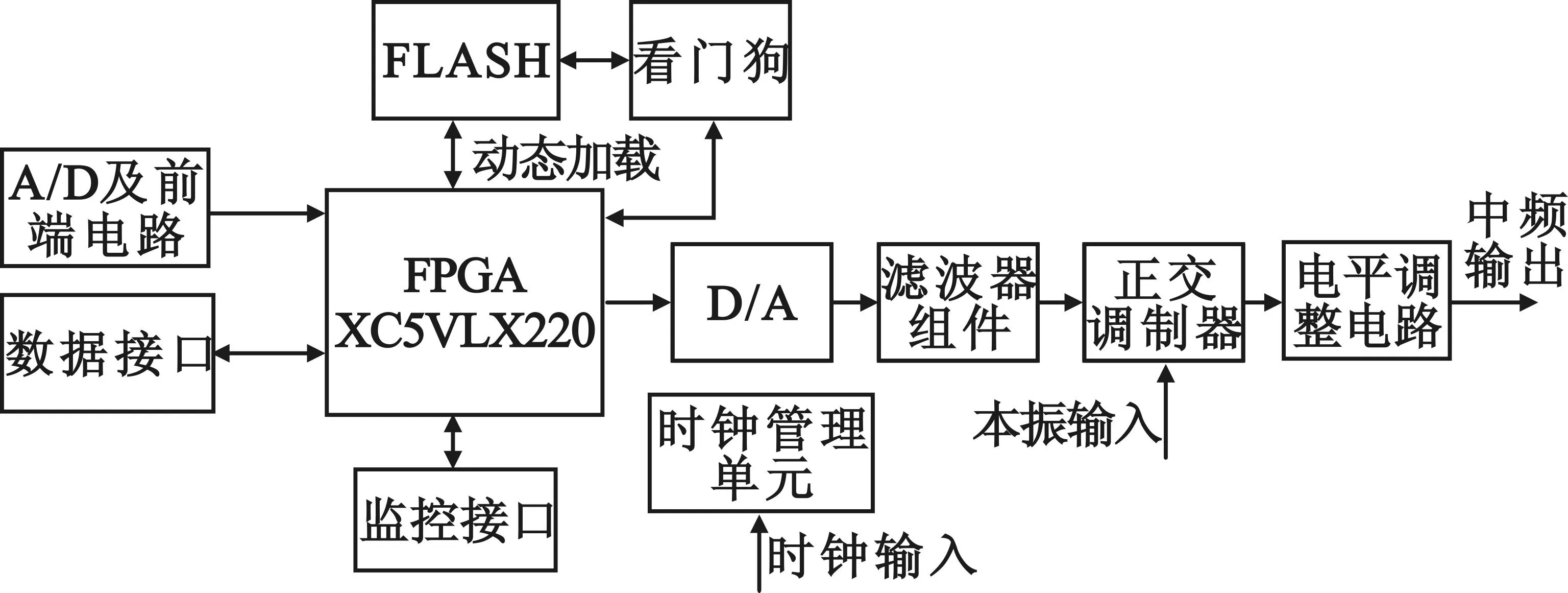

2硬件电路设计

硬件电路采用FPGA+外围电路的结构。工作模式(包括解调速率、调制速率、调制方式等)切换通过RS422串口设置。

图3 硬件电路框

图3中,监控接口为全双工RS422异步接口,数据接口为LVDS接口;看门狗完成FPGA软件动态加载的看门狗功能。

(1)根据全数字解调的需求,A/D采样后的信号处理算法在FPGA中实现,扩频解调信号处理算法对资源需求大,选择了Xilinx资源多的XC5VLX220芯片。利用带通采样定理[3]选择A/D采样率,A/D支持105 Ms/s采样率。A/D前端还有AGC芯片,使模块能支持0 dBm~-30 dBm动态范围的信号接收。

(2)D/A采用了MAXIM公司的16-bit宽带D/A芯片,支持500 Ms/s采样率,采用双路D/A。

(3)为了适应信息速率跨度从500 kb/s到110 Mb/s的调制,采用了模拟正交调制的方式,外部输入本振,实现L频段中频的调制。

(4)可控滤波器组件根据0.500~110 Mb/s速率实际的信号带宽分档设计共用,I、Q双路,共6档,可根据TTL控制信号选择滤波器,从而改变带宽。

(5)可调衰减器动态范围31 dB,1 dB可调。

(6)电源独立,模拟电源和数字电源分开,具有过流保护和故障隔离功能。

(7)模拟电路需进行屏蔽。

(8)根据需求配置各种工作模式的调制解调速率、编译码方式,编译生成文件烧写在FLASH中,各模式通过动态加载重构。

(9)FPGA芯片最高运行时钟240 MHz,模拟器件工作在L频段,PCB设计采用高速设计规范。

(10)调制、解调电路布局合理,数字、模拟布局合理,以减少相互之间的干扰。

(11)易于测试,留有足够的LVTTL测试接口。

3软件设计

FPGA软件采用模块化设计,所有的数字逻辑和信号处理算法均由一片FPGA(XC5VLX220)完成,主要包括调制软件、解调软件、接口控制软件。

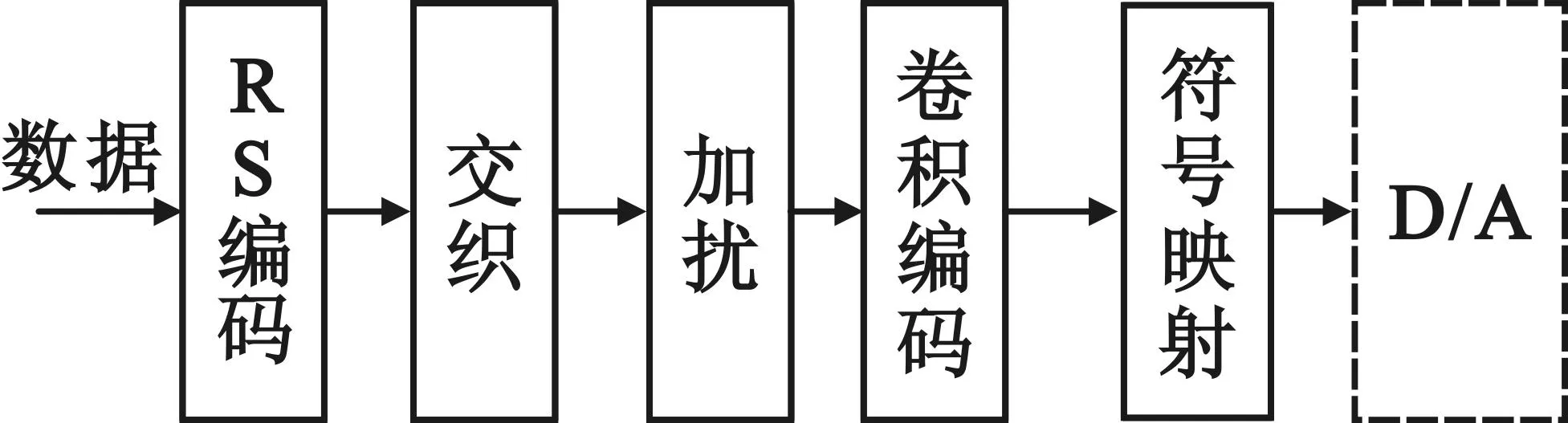

3.1调制软件设计

调制软件设计如图4中所示。

图4 调制软件设计框

调制软件主要由信道编码、交织、调制等功能模块组成。

对用户数据进行组帧后的数据由LVDS接口输入,经RS编码、交织、加扰、卷积编码然后进行BPSK/SQPSK符号映射,符号映射的数据经过成型滤波(10 Mb/s以下的信号),输出I、Q信号到D/A,D/A输出I、Q两路模拟信号到可控滤波器组,可控滤波器组输出I、Q两路数据到I、Q调制器调制到L频段中频,再经可调衰减器,实现输出电平1 dB步进。

3.2解调软件设计

解调软件主要包含扩频码捕获跟踪、数字下变频、载波捕获跟踪、定时同步、帧同步、信噪比估计等功能模块。

解调软件设计框图如图2所示。输入70 MHz中频信号经AGC放大器和ADC模数转换器后送入载波捕获跟踪环,经过与载波NCO混频完成正交数字下变频后,把I/Q信号输入伪码捕获跟踪环路,当伪码捕获跟踪以后,把伪码再送回载波捕获跟踪环进行解扩,经过ID滤波器、鉴相和环路滤波后,送出误差信号至载波NCO,控制载波NCO的输出频率,完成载波的捕获跟踪。另一方面把环路ID滤波后的I/Q数据送至位同步环,位同步环同步后把位同步信号送回载波捕获跟踪环,进行前向遥控数据的解调,经译码等过程后输出数据。

当载波环路没有锁定时,采用非相干AGC,通过输入信号的幅度检测输出相应的控制电压到AGC,使输入电平满足环路锁定的要求,当环路锁定后,自动切换到相干AGC,相干控制信息由载波环路的I/Q支路提取,根据幅度信息输出相应的控制电压到AGC,使送至环路的有用信号幅度基本一致,获得最佳的解调性能。

a)采样频率的选取

中频载波频率为70 MHz,信号所占带宽为7 MHz左右,根据带通采样原理,利用带通采样可以大大降低采样频率,同时还可以实现频谱下搬移。为了确保采样后不发生信号频谱混叠,采样频率fs、信号最高频率fh、最低频率fl和信号带宽fw必须满足以下条件,当采样频率介于两倍带宽和两倍信号最高频率之间时,采样频率需满足:

(1)

其中,k取满足下列条件的整数:

(2)

由式(2)可以算出2≤k≤10,可以取k=3,即得到不产生频谱混叠的采样频率为49 MHz≤fs≤66.5 MHz,因此选取带通采样的采样频率fs=60 MHz,70 MHz的中频信号经ADC采样后信号频谱被搬移到10 MHz附近。

b)扩频码捕获跟踪环

目前,直扩系统扩频码相位的捕获方法很多,根据实现结构可分为串行捕获、并行捕获及串并结合的混合捕获;根据处理域可分为频域捕获、时域捕获;根据解扩运算方法可分为基于相关器的捕获和基于匹配滤波器的捕获。所有捕获方法的基本原理都是先将接收的扩频信号与本地扩频序列相关,以衡量信号间的相似程度,并将相关的结果与设定的门限值比较,以确定两个扩频信号是否处于同步状态。若是,则开始跟踪,若不是,则继续捕获:在不确定区域内改变本地扩频序列的相位或频率,再次与接收扩频信号相关,直至在整个不确定度范围内捕获到接收扩频信号的相位为止。

由于多普勒频移不确定度的存在,对扩频码相位的捕获过程是一个在时间域和频率域同时进行的二维搜索过程。时域上是时间上的不确定性带来的码元搜索,频域上是载波多普勒频移引起的频率搜索。对扩频码相位的搜索是利用扩频码的相关性通过大量的相关运算完成的,而对多普勒频移的搜索则是将整个频率不确定范围分为许多个频率区间依次或者并行搜索完成。

本设计方案通过采用数字匹配滤波器在时域完成快速相关运算,同时在频域上对多普勒频率的峰值进行门限判决,从而巧妙地将二维搜索转化为只有码元搜索的一维搜索。相对于传统的方法(例如非相干积分方法)而言其在性能上具有更大的优越性,完成技术指标要求的时间硬件资源大大减少。基本原理如下:

如果接收数据与本地PN码相位对准了的话,它们的M个分段相关值实际上可认为是频率等于多普勒频移的正弦波的M个采样值。将求得的M段相关结果相同位置上的相关值取出来构成一个新的M点序列,然后对其作FFT变换,如果在频域上有数值超过了设定门限值,则可判定码相位的搜索已经完成,且该数值对应的频率值就是多普勒频移的值,即频域上的搜索也同时完成了。如果N个M点的FFT中有超过门限的峰值出现则停止搜索,否则一次N点的搜索结束,将参与运算的M段本地PN码的最早的一段(N个采样值)溢出,新的一段(N个采样值)移进来,开始新一轮的搜索,直到有超过门限的数值出现,否则将继续在整个不确定度范围内对本地PN码进行搜索。

本方案中所使用的扩频码捕获算法为分段相关快速捕获算法,即利用数字匹配滤波技术和分段平均功率谱估计进行伪码相位的捕获,软件实现主要分为以下模块:数据存储准备模块、本地扩频码产生模块、相关运算模块和相干积分模块。为了克服多普勒变化率大对频率槽设置带来的影响,在数据准备模块中,我们先直接存储A/D采样数据(8倍采样率),再下变频到相应频率槽的中心频率,这样可以利用频率槽的串行搜索完成捕获,减轻硬件资源上的压力。原理框图如5所示。

图5 码捕获的原理框

扩频码的跟踪采用延迟锁定环(DLL),它是利用扩频码优良的自相关特性,产生误差信号电压控制本地扩频码钟频率,使本地扩频码跟踪或锁定于接收扩频码。延迟锁定环分为单Δ环和双Δ环。由于单Δ环相位抖动小,跟踪精度高,该软件设计时采用单Δ环。

c)载波捕获跟踪环

载波捕获跟踪环由Costas环实现,主要包括相位检测器、压控振荡器和环路滤波器[4]。同时采用FFT频率辅助捕获措施,它的主要原理为通过FFT算法估算输入信号与NCO中心频率的差值,然后把差值变换成频率控制字后对NCO的频率控制字进行预置,使输入信号的频率处于环路的快捕带内,从而实现环路的快速捕获。环路滤波器采用成熟的二阶环结构。

d)定时同步

定时同步环接收载波解调costas环的I、Q双通道数据,完成定时同步信号的提取,选取得到广泛应用的早晚门型,它是一种较易实现的近似最佳同步环路,它的等效鉴相器有两个积分取样电路,分别称为早积分和晚积分。它们的取样和清除脉冲由DCO经时序产生器提供。

在定时同步环中,DCO输出的时钟驱动时序产生器产生早、晚两个选通信号,早门选通信号比输入的信息码滞后1/4码元宽度,晚门选通信号比输入信息码超前1/4码元宽度。这两个选通信号分别控制输入信号在早门积分器和晚门积分器中的积分,其积分区域均等于一个码元持续时间。在一个积分区域内,积分器对输入信号积分4次。在选通信号的起始时刻对积分器前一积分区域内的积分值进行取样,同时将积分器清零开始下一次积分。对取样的积分值求模,并将晚门积分器和早门积分器的积分值的模相减,即可获得DCO输出时钟与输入码元跳变沿的时间误差,此误差信号经环路滤波器滤波后用来调整DCO的相位。达到定时同步后,DCO输出的本地时钟和输入信息码元在时序上达到一致,早门和晚门积分器的积分取样值的模趋近相等,输出误差信号趋近为零。

误差信号计算公式为:

E=(|I晚|+|Q晚|)-(|I早|+|Q早|)

e)译码

前向接收只有viterbi译码,采用成熟的IPcore实现。

f)软件动态加载

为了保持模块的通用性,尽可能的兼容多种编码方式和调制方式,设计时FPGA软件采用ICAP动态加载方式,软件固件存储在大容量FLASH中,支持4个版本的动态加载,每个版本可以作为一种工作模式,都可以控制接收速率、发射速率及电平等;初始加电时,默认加载一个版本,其它几个版本可分别通过外部指令控制加载到FPGA中,各版本分时使用。因此,该模块可以灵活的作为通用模块使用。

3.3接口软件设计

接口软件主要包括LVDS接口高速数据的接收、数据发送,以及RS422串口监控软件。这些都是成熟的技术,不在此展开叙述。

4达到的性能指标

a)调制性能

1)矢量调制误差(EVM):≤5%;

2)杂波:≤-60 dBc;

3)谐波:≤-40 dBc;

4)输出电平:0 dBm~-30 dBm。

b)解调性能

5)解调门限:Eb/N0=7 dB时,BER<1×10-6;

6)多普勒动态:±110 kHz,2 kHz/s;

7)电平动态:0 dBm~-30 dBm。

由以上性能指标可以看出,在较大的多普勒动态以及信息速率跨度很大的情况下,该通用模块调制解调的性能都达到了比较高的水平。

5结语

本文基于FPGA+外围电路的通用硬件电路架构,采用全数字调制解调实现基带处理算法,采用I、Q双路D/A正交调制,并且利用FPGA 的ICAP动态加载技术,设计了一种通用的卫星通信调制解调模块。利用动态加载技术,实现多种扩频速率、调制方式和编译码方式的任意组合,软件可灵活重构。

经过工程实践验证表明,该模块参数配置灵活,可扩展性强,通过更新FPGA程序即可实现不同需求信号的调制解调,是一个开放的通用平台。目前该产品已开始小批量生产,可广泛应用于卫星通信及其他宽带通信设备。

参考文献:

[1]吴学智,武兵,何如龙.外军新一代卫星通信系统及关键技术研究[J].通信技术,2012 ,45(09):7-8.

WU Xue-zhi,WU Bing,HE Ru-long.Research of New Satellite Communication System and Key Technology inForeign Army[J].Communications Technology,2012,45(09):7-8.

[2]张欣.扩频通信数字基带信号处理算法及其VLSI实现[M].北京:科学出版社,2004:110-135.

ZHANG Xin.Digital Baseband Signal Algorithm and Its VLSI Realization[M].Beijing: Science Press,2004:110-135.

[3]郑生华,韩华,王冰.雷达数字接收机中的中频带通采样和数字I/Q解调及其实现[J].现代电子,2002(02):29-30.

ZHENG Sheng-hua,HAN Hua,WANG Bing.Study and Realization of Intermediate Frequency Bandpass Sampling and Digital I/Q Demodulation in Digital Radar Receiver[J].Modern Electronic,2002(02):29-30.

[4]刘艳华.Costas环法BPSK信号解调的研究与实现[J].通信技术,2012,45(01):16-17.

LIU Yan-hua.Study and Realization of BPSK Signal Demodulation with Costas Loop[J].Communications Technology,2012,45(01):16-17.

A Universal Modulation and Demodulation Module Board Design of Satellite Communication

XU Yuan-chao

(No.10 Institute of CETC,Chengdu Sichuan 610036,China)

Abstract:For developing a baseband disposal module used by multiple satellite communication device,an universal and wideband digital modulation and demodulation module is designed with modularization and digital method.Based on an universal hardware,the developed product supports spread spectrum signal demodulation with spread spectrum clock of 3~4 Mc/s and message rate of 2.4~9.6 kb/s,and wideband BPSK/QPSK modulation with message rate of 0.5~110 Mb/s.In addition,4 working mode can be configured in accordance with rate,coding and modulation,which switched by control command.Project application indicates this module is an universal product completely suitable for baseband disposal need of multiple satellite communication devices.

Key words:satellite communication,digital modulation and demodulation,wideband universal

doi:10.3969/j.issn.1002-0802.2016.02.022

* 收稿日期:2015-09-01;修回日期:2015-12-10Received date:2015-09-01;Revised date:2015-12-10

中图分类号:TN914

文献标志码:A

文章编号:1002-0802(2016)02-0238-05

作者简介:

徐远超(1982—),男,硕士,工程师,主要研究方向为卫星通信。