一种基于多处理器的星载计算机抗辐射加固设计方案*

2016-06-28彭小燕彭飞刘凯俊杨鹿蔡曦

彭小燕 彭飞 刘凯俊 杨鹿 蔡曦

(上海航天电子技术研究所,上海,200109)

星载计算机作为卫星上的核心部件,主要用于卫星控制、数据处理和星务管理等。空间环境不同于地面,其中存在着许多电磁波与高能粒子,它们会对星载计算机系统中的电子器件产生各种辐射效应。如果星载计算机没有任何防辐射措施,将很容易受到电磁波的辐射和高能粒子的冲击,从而影响到计算机内部微电子器件的性能和参数,导致卫星工作的异常或故障[1]。由于卫星的工作具有长期性和不可维护性的特点,一旦卫星出现故障几乎无法进行修复,整个卫星可能就会报废,甚至成为太空垃圾,这些都将带来巨大的损失。所以,对星载计算机进行抗辐射加固设计是星载计算机分系统设计的重要组成部分。本设计方案中所提出的“多处理器高性能星载计算机”抓住了星载计算机多个高性能处理器协同工作这一重要趋势,利用系统由多个高性能处理器组成这一先天条件,使得本系统的性能得到大幅提升,可以将出错的处理器进行替换,大大提高了星载计算机系统的可靠性,实现了星载计算机的抗辐射加固设计与高性能设计的平衡。本设计

一种基于多处理器的星载计算机抗辐射加固设计方案*

彭小燕彭飞刘凯俊杨鹿蔡曦

(上海航天电子技术研究所,上海,200109)

文摘:采用4DSP+FPGA结构方案,在满足系统高可靠性的前提下,运行一种“3+1”的工作模式,针对备份DSP提出一种可选的“轮转切换”方案,利用预读节省DSP进行数据读取的时间,实现星载计算机的抗辐射加固设计与高性能设计的平衡。

关键词:卫星设备;星载计算机;多处理器;抗辐射加固。

星载计算机作为卫星上的核心部件,主要用于卫星控制、数据处理和星务管理等。空间环境不同于地面,其中存在着许多电磁波与高能粒子,它们会对星载计算机系统中的电子器件产生各种辐射效应。如果星载计算机没有任何防辐射措施,将很容易受到电磁波的辐射和高能粒子的冲击,从而影响到计算机内部微电子器件的性能和参数,导致卫星工作的异常或故障[1]。由于卫星的工作具有长期性和不可维护性的特点,一旦卫星出现故障几乎无法进行修复,整个卫星可能就会报废,甚至成为太空垃圾,这些都将带来巨大的损失。所以,对星载计算机进行抗辐射加固设计是星载计算机分系统设计的重要组成部分。

本设计方案中所提出的“多处理器高性能星载计算机”抓住了星载计算机多个高性能处理器协同工作这一重要趋势,利用系统由多个高性能处理器组成这一先天条件,使得本系统的性能得到大幅提升,可以将出错的处理器进行替换,大大提高了星载计算机系统的可靠性,实现了星载计算机的抗辐射加固设计与高性能设计的平衡。本设计

1 系统平台方案

本设计方案希望通过对星载计算机软件容错技术进行研究,来解决传统星载计算机系统高性能与高可靠性难以协调兼顾的问题。

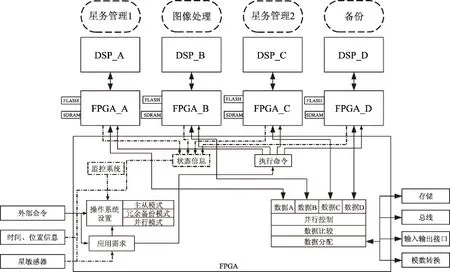

本设计方案采用FPGA和4个DSP构建多处理器高性能星载计算机系统,其硬件结构如图1所示。每个子系统由DSP(数字信号处理器)、FLASH(闪存)、SDRAM(同步动态随机存储器)、FPGA(现场可编程门阵列,也称为子系统FPGA)和JTAG(联合测试工作组)接口等器件组成。每个子系统都连接到一个管理FPGA上(称为全系统FPGA),并连接共享双端口SRAM、FLASH、1553B总线控制器、RS-422/LVDS收发器等外设。系统的关键接口包括子系统和全系统。

a)子系统。每个子系统内部利用子系统FPGA实现数据处理器SMJ320C6701的32位 EMIF接口与FLASH/SDRAM直接连接,同时将EMIF接口引出至全系统FPGA,并实现基于“检二纠一”的EDAC(错误检测与纠正)校验编码。其中,对子系统存储接口的模式配置为:DSP与FLASH——异步EMIF接口总线模式复用(典型配置);DSP与SDRAM——同步EMIF接口总线模式复用(SDRAM模式配置);子系统对外接口(通过子系统FPGA)——EMIF数据/地址线、异步/同步EMIF控制信号(含Full -rate SBSRAM模式)、McBSP接口、中断信号(DSP到主机、主机到DSP)、定时器/GPIO信号、DMA控制信号等。

b)全系统。全系统FPGA中实现定制EMIF总线扩展逻辑,将高速同步SRAM接口映射连接至两片双端口SRAM,最大程度保证全系统共享存储的访存效率[2];将异步EMIF地址映射至全系统FLASH和1553B控制器,实现全系统DMA功能;将串行通讯McBSP接口映射至RS-422/LVDS接口,并实现McBSP到通用串口的协议转换。其中,对全系统存储和接口控制的模式配置如下。

·双端口SRAM:同步EMIF接口总线模式复用,支持Full -rate SSCLK下4 -beat burst SBSRAM模式读写。

·FLASH:异步EMIF接口总线模式复用(DMA支持)。

·1553B总线控制器:异步EMIF接口总线模式复用(DMA支持)》

·RS-422/LVDS收发器:McBSP接口交叉开关(CrossBar)模式复用及串口协议转换(DMA支持)。

此外,全系统FPGA中还集成了系统模式配置和备份切换等全局控制逻辑,通过预先设定的控制寄存器和状态寄存器与各个子系统交互。

2 系统运行方案

2.1系统启动及运行

该系统在正常工作的情况下,3个处理器单元进行并行计算(称为并行子系统)。一个处理器单元处于待机或预处理状态(温备份),作为并行系统的冗余备份(称为备份子系统);各并行子系统运行时通过自检或过程比较等方式进行检错,发现自身故障时,该并行子系统进行重启操作,同时通过管理控制单元将其上任务切换到备份子系统再次执行。未出现故障的并行子系统可以继续运行,利用系统的高效处理能力弥补处理器切换的时间消耗,实现整体任务不中断。

系统启动和运行包括待机、初始化、配置、执行、故障诊断与备份切换等状态,状态间的切换均由全系统FPGA发出命令进行控制,如图2所示。

软件初始化中,系统构成为1个主控DSP、3个从属DSP与全系统FPGA中的控制逻辑。每个DSP独立地将程序存在私有的Flash中,在上电启动后,利用boot代码将程序搬运至SDRAM,执行主程序。在初始化状态,DSP将进行芯片配置、初始化外设,完成状态检查,等待全系统FPGA发出下一步的命令。

全系统FPGA将根据DSP健康状态和系统运行日志,选择最可靠的DSP作为主DSP。基于系统处理能力和扩展性的考虑,全系统FPGA负责由外部信息获得需要执行任务的标号,而相应任务本身需要的冗余度、并行度和外设需求等信息均保存在每个DSP中。主DSP将根据全系统FPGA提供的任务标号再将任务的需求信息反馈给全系统FPGA。

全系统FPGA综合任务需求信息与环境因素、外部命令综合考虑,激活相应的从DSP,并对它们进行配置(并行或备份)。而每个DSP相对独立地在被激活后,读取其配置信息,如果为并行模式,DSP将根据任务标号、子程序标号执行对应的代码;如果为备份模式,DSP将原地等待之后的调度和分配。

每个DSP子系统在运行过程中进行自身的故障检测,检测到故障发生时,子系统将进入故障诊断状态。如果为可恢复故障,该系统将继续执行;如果为不可恢复故障,子系统将通知全系统FPGA启动备份切换和中断任务分配,故障DSP子系统被全系统FPGA重启进入初始状态,等待下一轮模式配置和任务分配。

2.2多DSP并行方案

并行处理的目的是采用多个处理单元同时对任务进行处理而减少任务的执行时间,达到实时性的要求[3]。本设计方案的范围主要是在高性能DSP硬件平台上的多DSP并行结构和DSP算法的并行实现。DSP并行实现要求分配并行任务,调整数据结构,平均分配功能单元,利用汇编语言的灵活性合理编排指令,设计性能良好的并行算法[4]。

本多处理器高性能星载计算机采用DSP作为运算处理单元,在并行工作模式下,采用3×DSP并行结构,同时在每个DSP内具有多个数据处理通路、多个寄存器组等多功能单元。多处理器和多功能单元的可并行操作是并行处理的基础,在应用实现上可将任务划分为多份,交予多处理器进行实现;在算法设计中可以在一个周期内尽量安排多个占用不同功能单元的指令,提高程序的执行速度。

在并行处理中,系统的DSP并行方式包括三种处理方式:多类任务同时执行、一类任务多次执行和一个任务分割执行。

a)多类任务同时执行。在“多类任务同时执行”这种并行处理方法中,进行并行运算的3 个DSP各自处理不同的程序任务。如图3所示,DSP_A中执行星务管理程序1,DSP_B执行图像处理,DSP_C执行星务管理程序2。程序的分配由FPGA中的“operation configure”(操作系统设置)模块进行操作,该模块在程序开始运行之前,根据外部指令、卫星的时间位置信息、航天器的传感器信息和程序需求来决定并行处理的方法和最终的程序分配。在这种并行处理方法下,DSP各司其职,相互之间没有数据关联,当星上需要同时进行多个程序的执行时,此种并行方法是比较合适的。

b)一类任务多次执行。在这种并行处理方法中,同一个任务要执行多次的重复操作,只是每次进行操作的数据不相同,而且数据相互之间完全没有关联。如图4所示,系统进行视频图像处理,由于一个视频图像处理分为很多帧,而每个帧的操作除了被操作数据不同外,其它都是一样的,视频图像帧与帧之间没有任何的数据关联,所以FPGA将视频图像中的不同帧分给不同的子系统处理,图中DSP_A、DSP_B和DSP_C分别处理第n、n+1和n+2帧图像。同样,DSP执行内容的分配也由FPGA中的“操作系统设置”模块进行操作,当星上需要快速而且重复的执行某个程序时,此种并行方法是比较合适的。

图3 多类任务同时执行

图4 一类任务多次执行

c)一个任务分割执行。对于“一个任务分割执行”这种方法,进行并行运算的3个DSP各自处理程序中的一部分,各DSP之间处理的内容可能存在数据关联。我们以某一待处理图像为例(如图5所示双线大方框区设为图像部分),系统在对其进行处理之前,为了高效而快速地执行程序,首先将图像分为12个小图,每个DSP执行其中的4幅小图像。不同于一类任务多次执行,首先,一个任务分割执行说明这个任务只执行了一次,而不是重复执行,另外任务的分割会带来分割之后任务间的一些数据交互,如图像在分割和拼接的时候存在少量数据交互。FPGA中的“操作系统设置”模块进行程序的分割和分配操作,如图6所示(图像与图5对应)。当星上需要快速执行某个大型程序时,此种并行方法是比较合适的。

图5 “一个任务分割执行”情况下的任务分配示例

图6 一个任务分割执行

3 故障诊断与恢复

3.1故障诊断

在并行情况下,每个DSP子系统可以依靠自检进行简单故障诊断,主要依赖于程序监视技术[4],即“看门狗”,记录处理器程序“跑飞”或“死机”造成的无响应状态。如果在设定时间内发生故障的次数超过设定值,即认为子系统发生不可恢复故障,通知管理调度单元执行备份切换。

由于“看门狗”技术无法检出DSP运算结果出错的情况,因此参照该方案的硬件结构和特定应用,结合已有的控制领域故障诊断技术,对不同的并行方案制定各自的故障诊断方案,作为对自检技术的补充。

对于“多类任务同时执行”的情况,由于每个DSP执行的任务完全独立,在任务明确的情况下,对较为复杂的图像处理类任务采用基于知识的故障诊断方法,如机器学习等,有利于提高故障检出率;对较为简单的星务处理类任务可采用基于信号处理的故障诊断方法[5],降低诊断开销。

对于“一类任务多次执行”和“一个任务分割执行”的情况,多个DSP系统构成SIMD架构,非常利于使用基于解析模型的故障诊断方法,如状态估计法、等价空间法和过程参数估计法等,利用DSP任务过程比较发现输出结果异常。

由于SMJ320C6701支持德州仪器(TI)官方提供的轻量级实时操作系统DSP/BIOS,具有简单的多进程管理功能。利用DSP/BIOS提供的基于优先级设置的进程切换和调度机制,可以方便的实现软件多模冗余和定时器超时处理等容错设计。此外,DSP/BIOS还可以大大简化星务管理中的任务优先级设置操作,有效保证“多类任务同时执行”应用场景下的全局实时性。

3.2备份切换方案

3.2.1备份执行流程

从程序的运行方式可以看出,不论系统运行在何种并行处理方式下,都有一个处于温备份状态的DSP在等待切换,系统中每个DSP的运行流程都如图7所示。系统启动之后,各子系统进行初始化操作,在全系统FPGA的配置下,3个DSP子系统进行并行操作(如图7中①所示),而且在执行程序的过程中进行自检。如果并行系统中某个DSP发生了故障,则该DSP将通过中断告知全系统FPGA中的调度系统,DSP子系统自身复位。进行温备份操作的DSP则进行等待(如图7中②所示),当收到调度系统的启动命令后,则启动程序并加入到并行系统中执行任务。

图7 DSP运行流程图

在被配置为备份的DSP中,可以选择基本模式(如图7中③所示)或冗余模式(如图7中④所示)。基本模式下,备份DSP将处于低功耗状态,不执行运算任务,等待调度系统唤起。冗余模式下,备份DSP将按照预先设定的选择机制(如参考历史状态等)在当前3个并行DSP中选取一个并行任务同时执行。如本轮处理中(两个同步点之间)并行DSP未发生故障,则备份DSP在下一轮继续选择新的任务进行冗余计算;如本轮发生故障,若发生故障的并行任务与备份DSP运行的冗余任务相同,则可以直接采用冗余运算的结果,预测失败情况下备份DSP停止当前操作,重新执行故障DSP任务。这种模式具有最短的系统恢复时间。

3.2.2备份替换策略

本设计方案提供可配置的备份替换策略,支持不同环境下性能与恢复时间之间的权衡。每种备份替换策略下,执行备份的DSP均可选择基本模式或冗余模式。

a)固定备份机制。固定备份机制选取某个特定DSP作为系统温备份。以图5的图像处理为例,一张高清图像被划分为12个任务,其中每3个任务为一轮,由3个并行DSP(例如DSP_A、DSP_B、DSP_C)同时处理。在冗余模式下,每轮由固定备份DSP(例如DSP_D)执行选定的任务(如与DSP_A相同)。由于这种备份替换方式具有确定性,在硬件上可以预先根据并行DSP和备份DSP运行特点,采用特定的加固优化设计,达到最好的运行效果。

b)轮转备份机制。与固定备份切换机制不同,在轮转备份机制中,没有某个固定的DSP一直运行在备份状态下。此时,备份操作由DSP_A、DSP_B、DSP_C、DSP_D轮流执行。以图5的图像为例,在执行第一轮任务(即任务1~3)时,DSP_D作为本轮备份;在执行第二轮任务(即任务4~6)时,FPGA调度系统将DSP_A设置为本轮备份,以此类推。轮转备份机制比固定备份具有更好的公平性,在基本模式下有利于缓解系统TID(辐射总剂量)积累,增强抗辐性能。

c)预读机制。在当前系统定义中,处于温备份状态的DSP,无论是基本模式还是冗余模式,对于提升系统运算性能来说是没有帮助的。考虑到在实际系统运行中,故障发生属于小概率事件,为了在保证系统可靠性的前提下提高系统的性能,本方案在轮转备份的基础上,提出了预读轮转切换方法。

在预读轮转切换方法中,所有DSP轮流做备份,本轮首先完成并行处理任务的DSP为下一轮备份;备份DSP亦处于运行状态,执行后续处理任务。如本轮某DSP(如DSP_A)发生故障,则备份DSP终止当前操作,重新执行DSP_A的处理任务。这种方式下,无故障时系统中DSP为并行运行;故障时能够快速重新执行处理任务,具有最高的处理性能。

以图5的图像处理为例,FPGA在进行任务分割时,不仅仅对DSP_A、DSP_B和DSP_C分配待执行任务(如任务1~3)。同时也会对DSP_D分配任务(如任务4),在DSP_A、DSP_B和DSP_C进行并行计算的时候,DSP_D会将DSP_A下一阶段所要处理的数据预读到本地存储空间中,然后,在DSP_A执行当前阶段的程序之后,如果系统未出现错误,则DSP_D加入下轮并行,DSP_A则进入下轮备份预读。同理,在DSP_A进行温备份预读处理时,如果系统未出现错误,则DSP_A重新加入并行,由DSP_B进行备份数据预读。加入了预读的轮转备份机制下,系统实质上运行在4×DSP并行状态,这种方法在保证系统可靠性的前提下,缩短省略掉DSP读取数据的时间,从而最大程度提高系统处理性能。

可以看出,相同任务在各种备份配置下执行情况各不相同,在实际设计中可以根据系统对运算性能、可靠性、切换开销等方面的需求进行灵活配置。

本文以高性能、高可靠的并行星载计算机任务需求为背景,构建了“4DSP+FPGA”的多处

理器并行星载计算机体系结构,运行一种“3+ 1”的工作模式,利用DSP快速、丰富的对外接口实现多处理器的数据信息交互,以保证计算机的高性能需求。此外,利用多处理器的硬件资源提出处理器备份运行方案,即针对备份DSP提出一种可选的“轮转切换”方案,利用预读节省DSP进行数据读取的时间,实现计算机高可靠的抗辐射性能需求。

参考文献

[1]Bolchini C.,Miele A.,Santambrogio M.D.TMR and Partial Dynamic Reconfiguration to mitigate SEU faults in FPGAs”,the Proc. Of IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems.IEEE,2007:87-95.

[2]陈书明,汪东,陈小文.一种面向多核DSP的小容量紧耦合快速共享数据池[J].计算机学报,2008,31(10):1737-1744.

[3]郭保东.异构多核DSP互连通信机制QLINK的研究与实现[D].长沙:国防科技大学,2007:23-34.

[4]夏康.高可靠并行星载计算机硬件容错技术研究.上海交通大学硕士论文,2012-12-01.

[5]雷涛.多DSP并行多模跟踪软件系统的研究与优化实现.北京:中国科学院研究生院,2006:23-36.

作者简介:

彭小燕(1983年—),女,电子工程专业工程硕士,工程师,现主要从事星载计算机技术研究。

*本文源于国防预研抗辐射加固技术项目(513110401××)。方案使用FPGA和四片高性能DSP数字信号处理芯片组建多处理器高性能星载计算机平台,包括4DSP+FPGA系统架构和软件运行方案的设计。