低噪声低功耗斩波运放的分析与设计

2016-06-13张兆浩吴次南

李 威,张兆浩,吴次南

(贵州大学 大数据与信息工程学院,贵州 贵阳 550025)

低噪声低功耗斩波运放的分析与设计

李威,张兆浩,吴次南

(贵州大学 大数据与信息工程学院,贵州 贵阳550025)

摘要CMOS运放的噪声尤其是低频1/f噪声会随着整体功耗的降低而急剧增加,针对传感器读出电路应用,文中在传统斩波运放的基础上设计了一个低噪声、低功耗的嵌套式斩波运算放大器。基于SMIC0.18 μm工艺,通过Spectre仿真工具进行仿真与验证。高频斩波(fchop,high)频率为500 kHz,低频斩波频率(fchop,low)为2 kHz时的仿真结果表明,运放在100 Hz处的噪声功率谱密度(Power Spectral Density,PSD)降为23 ,总消耗电流14 μA,放大器的增益带宽积(GBW)为16.7 MHz,运放的电流效率(GBW/Itot)达到了1 193,该设计的整体性能与以往的设计相比具有一定优势。

关键词嵌套式斩波;低噪声;低功耗;残余失调;放大器

20世纪90年代以来互联网改变了世界,进入新世纪,学术界开始思考互联网的未来,于是便出现了“物联网”(Internet of Things,IOT)概念[1]。在物联网中,传感器是物质世界和互联网的接口,是物联网的重要组成部分,所以物联网在最初也称为“传感网”。随着传感器技术的发展,尤其是微机电系统(Microelectromechanical Systems,MEMS)的发展,物联网同时也获得了更广阔的发展空间。

传感器接口电路是物联网概念中一项重要的研究内容。一方面,若要长时间大规模地使用传感器网络,传感器接口电路必须有较低的功耗或有稳定的能量来源。例如在医疗电子应用中,植入生物体的芯片必须具有极低功耗,以确保生物芯片能在很长一段时间内使用;另一方面,传感器信号非常微小,且基本处于低频段,这就需要传感器信号读出电路具有极低的噪声[2]。以CMOS电路为例,对于传感器读出电路中最重要的低噪声放大器来说,其主要噪声来源包括了全频段下的热噪声以及低频处的闪烁噪声。正如所知,放大器的功耗与噪声存在折衷关系:随着功耗的降低,其噪声性能尤其是低频1/f噪声性能将严重恶化。现代CMOS集成电路工艺正朝着深亚微米方向发展,这就使模拟信号处理电路需要面对电源电压的降低以及1/f噪声、失调电压带来的更大挑战。由此可见传感器读出电路(Readout Circuit)正成为制约物联网进一步发展的一个重要因素。也因此,面向传感器应用的低噪声、低功耗运算放大器电路受到越来越多的关注[3]。

目前广泛采用的噪声消除技术有斩波技术和自调零技术。而自调零技术会造成白噪声的折叠,且自调零频率越高,折叠的白噪声越多,因而增大了基带噪声[4],为了抑制噪声,需要使用大电流,这使得自调零运放的功耗较大。所以由于低功耗的限制,本文采用斩波技术来消除失调和1/f噪声。

1斩波稳定原理与非理想因素分析

斩波稳定(CHS:Chopper Stabilization)技术是1948 年由E. A. Goldberg 发现的[5]。随着集成电路技术的不断发展,可快速应用于芯片集成技术。斩波技术最早被用来消除直流失调,由于在传感器接口电路应用中关注的噪声即噪声主要集中在低频段,所以可类似地将这些噪声看作是低频失调。

1.1基本原理

如图1是一个斩波放大器的基本构架[6]。这个放大器由一个斩波器CH1、一个放大器、另一个斩波器CH2以及一个低通滤波器组成。

图1 斩波稳定技术原理图

图1中下半部分(a)~(d)是正弦波输入时各个相应位置的理想波形图。信号(如图1(a))在进入放大器之前,会被CH1调制到高频(如图1(b)),被调制到高频的信号被放大器放大,如图1(c)所示;图中vos表示放大器中等效到输入端的直流失调(Offset)和1/f噪声,放大器将被调制到高频的信号和仍处于低频的vos同时放大;经过第二个斩波开关CH2之后,处在高频的信号被还原,而处于低频的Offset和1/f噪声则被调制到了高频,如图1(d)所示。图1(d)中有相对较大摆幅的锯齿波被称为纹波(Ripple)。在斩波完成后,处于信号通路上的低通滤波器将这些纹波滤除,这就消除了Offset和噪声的影响。

1.2嵌套斩波技术

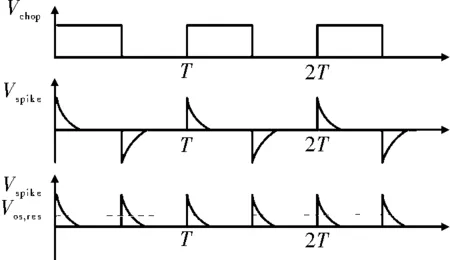

在斩波稳定放大器中,斩波开关一般由CMOS管组成。CMOS开关在时钟切换过程中产生的电荷注入效应,会造成残余失调,这是斩波运放一项重要的非理想因素。CMOS管栅极电压会在vSS和vDD之间快速切换,每次切换会通过交叠电容耦合一部分电荷进入信号通路,即产生毛刺,如图2所示。由开关产生的毛刺经过放大器放大然后被解调,相当于残留了一部分直流电压,这叫做残余失调。开关的面积越大,斩波频率越高,电荷注入越大,残余失调越多。

图2 斩波稳定中的电荷注入影响

在斩波技术中,斩波频率是一个关键的参数因其关系到整个斩波放大器的性能。要将如图1(c)这样的高频信号放大,明显需要斩波频率小于放大器的带宽,因只有这样放大器才不会有较大的增益损失,由于负载电容不会影响斩波速度,所以此处的放大器带宽指的是放大器空载时的-3 dB频率[2]。除了放大器带宽的限制,文中还要尽可能地消除1/f噪声,并使信号解调后不至于发生混叠,综合起来这就需要斩波频率满足[10]

(1)

2电路设计

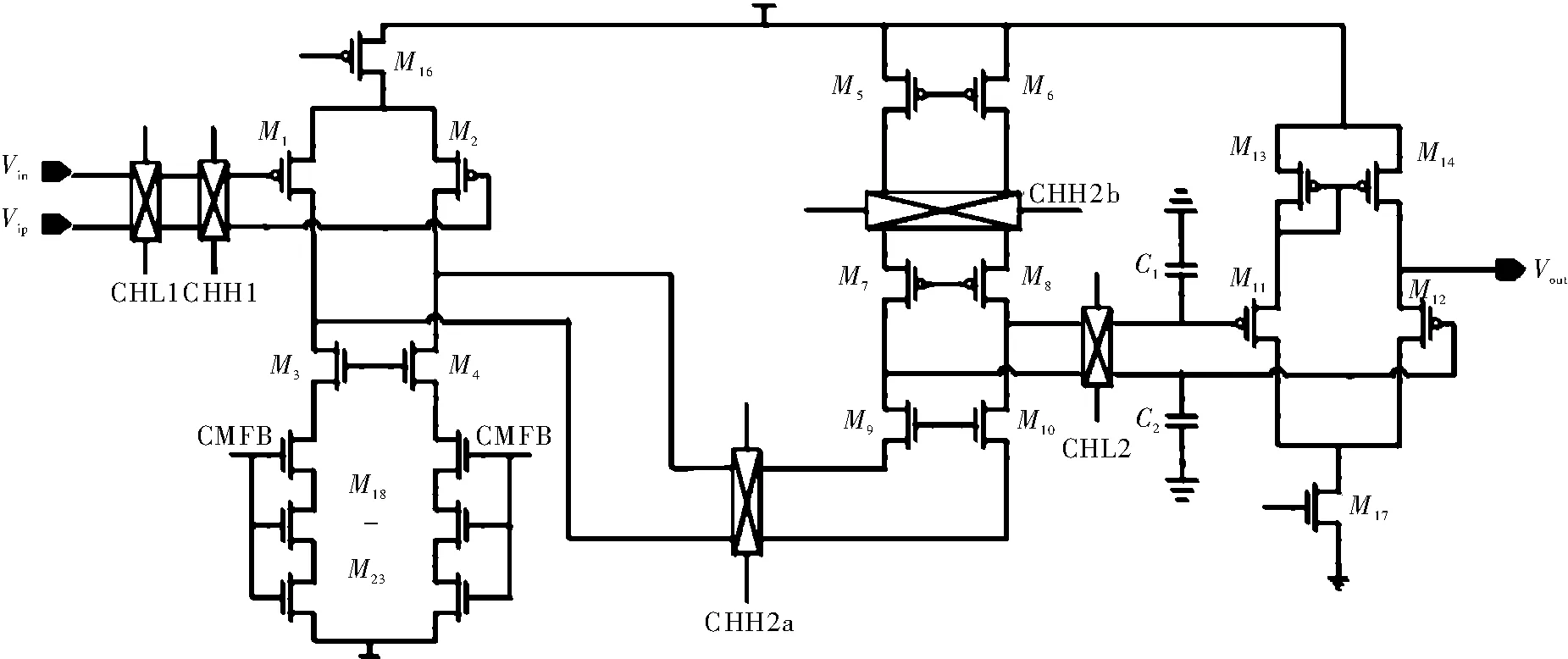

设计的两级斩波运算放大器主要由第一级的全差分折叠共源共栅电路和第二级有源电流镜负载的差分输入单端输出放大器组成,其中CHL1、CHH1、CHH2a、CHH2b、CHL2是斩波开关单元。本文采用高低阻点嵌套斩波方案。其中CHL1和CHL2是低速斩波开关,CHL2被设置在第一级放大器的输出点也就是第一级放大器唯一的高阻点;CHH1,CHH2a和CHH2b被设置在放大器内部的低阻点,实现快速斩波。

本设计电路如图3所示,输入管M1、M2采用大面积的PMOS管以减小1/f噪声的影响,M18~M23是6个处于线性区的NMOS管,构成第一级全差分放大器的共模反馈[11],稳定输出直流电平。M5、M6管和M3、M4管分别作为电流漏和电流源,由于整体电路的1/f噪声很大一部分取决于这4个管子,所以要取较大的面积,又由于带宽限制管子的L不能过大,且要减小其1/f噪声就要尽量减小其跨导,这就使得这4个管子必须处于饱和区,即需要较大的过驱动电压,低功耗意味着较低的宽长比,同时在此处也意味着较小的面积,这又与低噪声的要求相矛盾,这就使得这4个管子的沟道长度要合理的折中。由于1/f噪声的要求,M7~M10要有较大的面积,但又由于整体功耗的限制,管子要有较小的宽长比,这使得M7~M10必须处于亚阈值区才能满足低噪声、低功耗的要求。第二级电路是简单的差分输入、单端输出电路,由于电路中的第一个极点在第一级的输出处,第二个极点位于第二级的输出处,这使得第二级电路对带宽的要求较高,所以M11~M14要取较小的沟道长度。

图3 本设计整体电路图

设计斩波调制器,需要考虑电荷注入与时钟馈通效应的影响以及导通电阻是否能够满足信号的建立件。采用带虚拟管的CMOS开关斩波器有助于抵消部分电荷注入与时钟馈通效应,虚拟管置于开关管两侧,源漏相接,宽长比为开关管的1/2,具体电路如图4所示[12]。

图4 开关和斩波器

由于小的开关尺寸能减小时钟溃通效应。所以,输入端斩波开关CHL1采用较小尺寸的NMOS管(1 μm/0.18 μm)。为减小导通电阻引起的压降,在低阻点的斩波开关CHH1a、CHH1b分别取2 μm/0.18 μm、2 μm/0.18 μm的较大尺寸。此外,斩波调制器在进行版图设计时,应尽量使开关管环境处于对称状态,增加正反相寄生电容的匹配度,从而整体上减小电荷注入和时钟馈通效应产生的影响。

3仿真结果分析

含有斩波操作的放大器实际上属于开关电路,需使用Cadence公司的Spectre仿真工具中的PSS、PAC、Pnoise对其周期性稳态、幅频特性以及噪声性能进行仿真。本设计中的仿真基于SMIC0.18 μm工艺进行,斩波频率为fchop,high=500 kHz、fchop,low=2 kHz。

采用PAC仿真表明,其开环直流增益为101 dB,增益带宽积为16.7 MHz,带宽为150 Hz。系统消耗的总功耗为14 μA。此二级电路的主极点在第一级折叠共源共栅运放的输出端,其次极点在输出端,所以此运放带负载的能力较低。

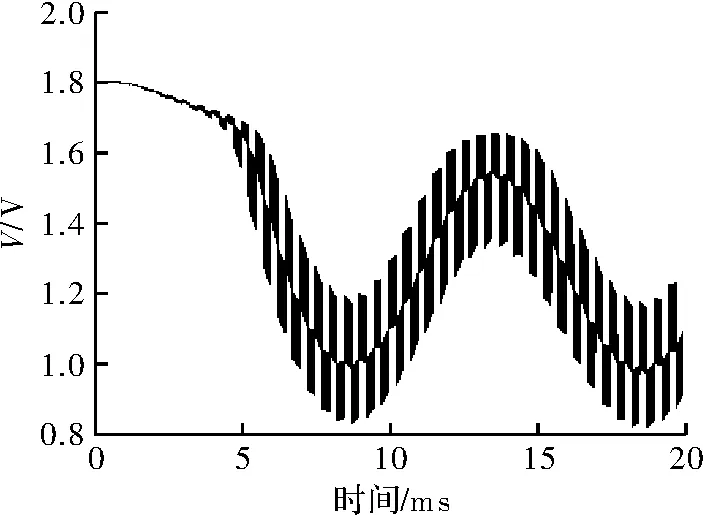

图5 Pnoise仿真结果

为仿真嵌套式斩波的残余失调消除效果,在斩波器CHH1和输入管M1之间加入1 mV的直流电压进行瞬态仿真,仿真结果如图6中所示,从图中可见残余失调基本被完全消除,但纹波还较大,这是因斩波频率只有500 kHz,本设计中的主极点位于第一级运放的输出处,第一级运放输出端的两个电容与第一级的输出电阻构成的低通滤波器对纹波起到滤除作用,而第一级运放的增益带宽积(GBW)较大,这使得第一级运放对500 kHz处信号的衰减较小。纹波可根据具体应用在后级电路中进行消除,此设计更关心其残余失调的消除情况。从仿真结果看,本设计对于残余失调的消除达到了预期的效果。

图6 加入1 mV失调后瞬态仿真结果

表1给出了本设计与其他论文的性能比较。文献[13]侧重于极低功耗的设计,其噪声性能较差;文献[14]有较好的低频噪声性能,但消耗了较大的电流;文献[15~16]与本设计消耗了相当的电流,但其电流效率较低。从整体性能上来说,本设计有相当的优势。

表1 斩波放大器的主要性能指标与比较

4结束语

参考文献

[1]Gubbi J,Buyya R.Internet of things:a vision,architectural elements,and future directions[J].Future Generation Computer Systems-the International Journal of Grid Computing and Escience,2013,29(7):1645-1660.

[2]刘爱荣,孔耀辉,杨华中.低电压Σ-Δ调制器关键技术及设计实例[J].微电子学,2008,38(5):727-730.

[3]陈铖颖,黑勇,胡晓宇.一种用于传感器信号检测的斩波运算放大器[J].微电子学,2012,42(1):17-20.

[4]Enz C C,Temes G C.Circuit techniques for reducing the effects of op-amp imperfections:auto-zeroing,correlated double sampling,and chopper stabilization[J].Proceedings of the IEEE,1996,84(11):1584-1614.

[5]杨银堂,贺斌,朱樟明.CMOS 斩波稳定放大器的分析与研究[J].电子器件,2005,28(1):167-171.

[6]Bakker A,Huijsing J H.High-accuracy CMOS smart temperature sensors[M].Boston,MA:Kluwer Academic,2000.

[7]Yoshinori Kusuda.Auto correction feedback for ripple suppression in a chopper amplifier[J].IEEE Journal of Solid-State Circuits,2010,45(8):1436-1445.

[8]Rong Wu,Kofi A A Makinwa,Johan H Huijsing.A chopper current-feedback instrumentation amplifier with a 1mHz 1/f noise corner and an AC-coupled ripple-reduction loop[J].IEEE Journal of Solid-State Circuits,2009,44(12):3232-3244.

[9]Bakker A,Thiele K,Huijsing J.A CMOS nested-chopper instrumentation amplifier with 100nV offset[J].IEEE Journal of Solid-State Circuits,2000,35(12):1877-1883.

[10]Menolfi C,Huang Q.A low-noise CMOS instrumentation amplifier for thermoelectric infrared detectors[J].IEEE Journal of Solid-State Circuits,1997,32(7):968-976.

[11]Behzad Razavi.模拟CMOS集成电路设计[M].陈贵灿,程军,张瑞智,译.西安:西安交通大学出版社,2013.

[12]孙鹏.用于植入式生物医疗系统的高性能仪表放大器的研究与设计[D].杭州:浙江大学,2013.

[13]Guocheng Huang,Tao Yin.A 1.3μW 0.7μVRMS chopper current-reuse instrumentation amplifier for EEG applications[C].Lisbon:IEEE International Symposium on Circuits and Systems (ISCAS),2015.

[15]Sun Peng,Zhao Menglian,Wu Xiaobo.A 36nV chopper-stabilized CMOS amplifier with a new ripple-spur-filter scheme[C].Xi’an:IEEE International Conference on Solid-State and Integrated Circuits and Systems,2012.

[16]Belloni M,Bonizzoni E.A micropower chopper-CDS operational amplifier[J].IEEE Journal of Solid-State Circuits,2010,45(12):2521-2529.

Analysis and Design of Low noise Low power Chopper OTA

LI Wei,ZHANG Zhaohao,WU Cinan

(College of Big Data and Information Engineering,Guizhou University,Guiyang 550025,China)

AbstractThe noise especially 1/f noise of a CMOS operational amplifier will sharply increase as the decrease of total power.This paper presents a low noise low power nested chopper operational amplifier aiming at the application of sensor readout circuit.We simulate and verify using the Spectre tools based on SMIC 0.18 μm CMOS process.The results show that the power spectral density(PSD)dropped to 23 at 100 Hz.The OTA consumes 14 μA of the total current,achieves 16.7 MHz of GBW and 1 193 of current efficiency at the 500 kHz of the High-chop frequency (fchop,high) and 2 kHz of Low-chop frequency (fchop,low).The overall performance of the OTA has advantages comparing to the papers published in recent years.

Keywordsnested-chopper;low noise;low power;residual offset;amplifier

doi:10.16180/j.cnki.issn1007-7820.2016.05.008

收稿日期:2016-03-09

作者简介:李威(1989—),男,硕士研究生。研究方向:模拟混合信号集成电路与低功耗模拟集成电路。张兆浩(1962—),男,博士,教授。研究方向:光学等。

中图分类号TN722

文献标识码A

文章编号1007-7820(2016)05-026-04