VPX平台的多板卡FPGA动态配置方法

2016-06-13陈昌明邵高平刘小蒙党力明

陈昌明,邵高平,刘小蒙,党力明,高 飞

(信息工程大学 信息系统工程学院,河南 郑州 450001)

VPX平台的多板卡FPGA动态配置方法

陈昌明,邵高平,刘小蒙,党力明,高飞

(信息工程大学 信息系统工程学院,河南 郑州450001)

摘要针对VPX平台板卡的FPGA通常采用上电时从非易失性存储器主动加载配置数据的方式,存在灵活性较差的缺点。文中提出了一种基于CPU+SPI总线+CPLD的多板卡FPGA动态配置方法,可在不开箱的情况下对平台内各板卡FPGA进行动态配置。经测试,该方法配置10.9 MB大小的数据用时约为7 s,具有较好的灵活性和可靠性。

关键词VPX;FPGA;动态配置

近年来,VPX平台[1]以其良好的机械结构和导冷抗震能力在航天、军用等可靠性要求较高的应用场合得到了广泛地应用[2]。FPGA作为当前主流的高速数字信号处理器,具有并行处理能力强、可重配置性等特点[3],在VPX平台板卡上得到大量采用。

目前,VPX板卡FPGA的配置数据通常固化于板上的PROM、Flash等非易失性存储器,每次上电时由FPGA主动从存储器加载配置数据。这种配置方式虽然具有稳定、快速等优点,但缺乏操作灵活性,如升级配置数据时需进行现场开箱调试,无法根据应用需求动态改变FPGA配置逻辑[4]。本文提出一种VPX平台多板卡FPGA的动态配置方法,可在不开机箱的情况下对平台各板卡FPGA进行动态配置,具有较好的灵活性和可靠性。

1总体设计方案

FPGA的配置模式主要有主串行模式、主SPI模式、主BPI模式、主SelectMAP模式、从串行模式、从SelectMAP模式和JTAG模式。主模式由FPGA控制配置过程,主动从片外非易失存储器加载配置数据;从模式需要外部的处理器或微控制器控制将数据加载到FPGA;JTAG模式为调试模式,断电即丢失数据[5]。考虑到从模式较主模式具有更好的灵活性,且从串行模式相较于从SelectMAP模式具有电路结构简单、节省PCB面积等优点,本方案采用从串行配置模式。

图1所示为VPX平台动态配置原理框图。VPX主控板作为平台的管理控制中心,采用CPU作为核心处理器,负责对各功能板的FPGA进行动态配置。主控板采用Flash存储各板卡临时的配置数据,并可通过串口和以太网口与平台外部的PC机相连。如需升级配置数据,可从外部PC机通过以太网进行下载。主控板与各功能板通过VPX总线形成星型互连,数据传输协议采用较易实现的SPI总线协议。由于CPLD具有接口实现容易、断电不丢失配置数据等特点,因此各功能板采用CPLD实现SPI接口电路以及对FPGA进行动态配置的控制逻辑。

图1 平台配置原理框图

2软件设计

2.1FPGA配置原理

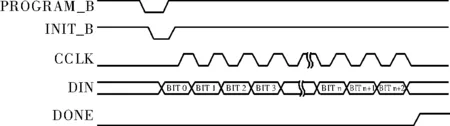

FPGA从串行配置模式的时序如图2所示。通电后,将PROGRAM_B引脚置为低电平,便可以对FPGA进行配置。PROGRAM_B引脚置低后,FPGA会将INIT_B引脚置低,并开始清空配置寄存器。在清空完配置寄存器后,INIT_B信号将重新被置为高电平。同时,FPGA将对配置模式引脚进行采样,并启动配置过程。配置过程开始后,处理器或微控制器在CCLK引脚产生配置时钟,在DIN引脚逐位产生配置数据,配置数据在CCLK上升沿有效。配置过程中如果发生错误,INIT_B引脚将被置为低电平,配置过程中断。此时,若要重新配置,只需将PROGRAM_B引脚置低即可。配置数据下载完成后,DONE引脚将被置为高电平,此时FPGA成功完成配置过程[6]。

图2 从串行配置模式时序图

2.2FPGA动态配置流程

VPX平台的多板卡FPGA动态配置流程如图3所示。上电后,VPX平台将对各板卡进行硬件初始化。CPU上电后执行引导加载程序,并对串口、以太网口进行初始化。初始化完成后,CPU将加载操作系统映像并启动嵌入式操作系统。操作系统启动后,可以从外部PC机通过串口发起动态配置任务。发起动态配置任务后,程序将初始化CPU的SPI模式控制寄存器,并通过SPI协议发送待配置功能板的地址。待配置功能板的CPLD收到地址命令后将与本板地址进行匹配,如匹配成功则准备开始接收数据并启动配置时序,其他功能板由于地址未匹配将不启动配置时序。同时,CPU从PC机或Flash读取配置数据并通过SPI总线传送给CPLD,CPLD接收数据并对FPGA进行配置。配置数据传送完成后,CPLD将对DONE信号进行检测并将配置结果通知CPU。

图3 FPGA动态配置流程

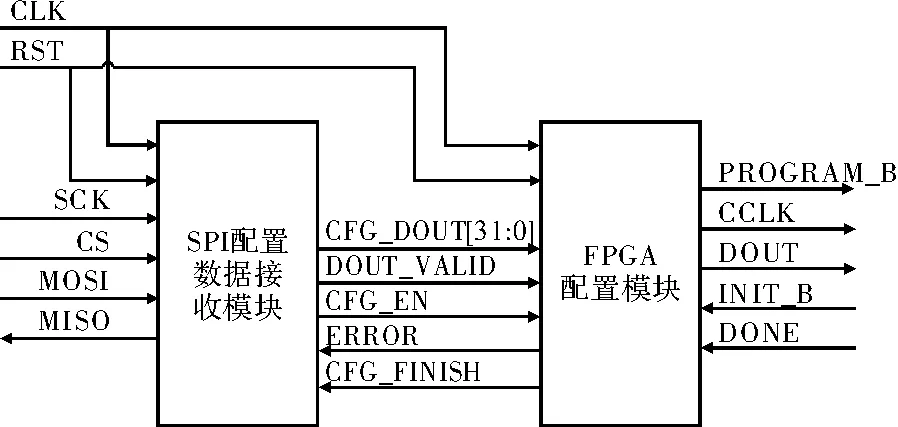

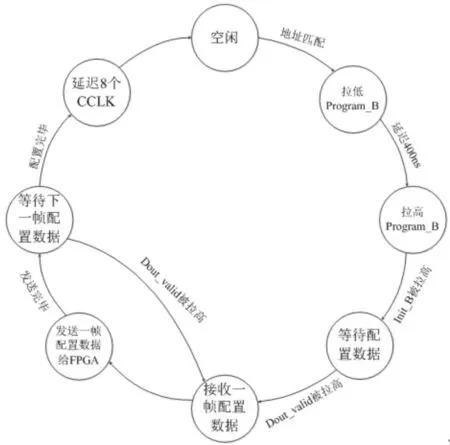

2.3CPLD配置逻辑设计

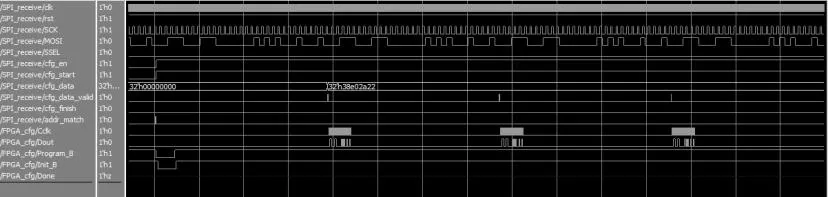

本方案中,CPLD的配置逻辑主要分为SPI配置数据接收模块和FPGA配置模块,其逻辑框图如图4所示。SPI配置数据接收模块主要负责接收VPX主控板通过SPI协议发送的数据,并将串行数据转换为并行数据发送给FPGA配置模块。FPGA配置模块主要实现对FPGA进行从串行配置的时序,其主要功能的状态转移图如图5所示。SPI配置数据接收模块检测到地址匹配后随即将CFG_EN拉高,FPGA配置模块检测到CFG_EN拉高后即将Program_B拉低,在保持400 ns后将Program_B拉高并检测Init_B。当检测到Init_B由低变高后,进入等待配置数据状态,并拉低Init_B延迟配置启动以等待配置数据。当检测到数据有效信号Dout_valid变高后,FPGA配置模块开始接收配置数据,一帧配置数据为32位。接收到一帧配置数据后,FPGA配置模块将并行数据转换为串行数据,并通过配置时序发送给FPGA。发送完毕后,FPGA配置模块开始接收下一帧数据,直至配置数据全部接收完成。配置数据接收完后,FPGA配置模块将检测DONE和INIT_B。若检测到DONE为高,在CCLK保持8个周期后配置过程结束。同时,CFG_FINISH将被拉高,通知CPU配置成功。若检测到INIT_B为低,则ERROR将被拉高,通知CPU配置失败。如图6所示为配置逻辑的功能仿真波形图。

图4 CPLD逻辑框图

图5 FPGA配置模块状态转移图

图6 功能仿真波形图

3实验仿真验证

为验证本方案的性能,在3U的VPX平台上进行测试。VPX主控板CPU型号为Freescale公司的MPC8536E,VPX功能板CPLD型号为Xilinx公司的XC2C256,FPGA型号为Xilinx公司Kintex7系列的XC7K325T,配置文件格式为.bin,大小为10.9 MB。经测试,FPGA配置一次的时间约为7 s,且该方法稳定性较好。由于FPGA从PROM存储器主动读取配置数据的方式配置时间一般为ms级[7],可以看出,本方案虽然配置时间较慢,但具有较好的灵活性。

4结束语

本方案实现了在不开箱的情况下对VPX平台多板卡FPGA进行动态在线配置,具有较好的灵活性,在需要动态改变FPGA配置的软件无线电平台等应用场合具有较好的应用前景,同时为其他类型的嵌入式信息处理平台也提供了借鉴。

参考文献

[1]洪艳,沈利华.基于VPX高速综合信息处理平台设计[J].导弹与航天运载技术,2011(3):58-61.

[2]吉玉洁,张小林.VPX 总线标准研究及其在无人机中的应用展望[J].计算机测量与控制,2012,20(4):1112-1115.

[3]杨海钢,孙嘉斌,王慰.FPGA器件设计技术发展综述[J].电子与信息学报,2010,32(3):714-727.

[4]陈曦,沈佐峰.一种可靠的FPGA动态配置方法及实现[J].通信技术,2012,3(45):105-107,110.

[5]Xilinx Company.UG470[M].San Jose:Xilinx Company,2013.

[6]田耘,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2008.

[7]黄勇.一种新型的FPGA快速动态配置和远程加载技术[J].通信技术,2013,46(12):93-96.

Multiple Boards FPGA Dynamic Configuration on VPX Platform

CHEN Changming,SHAO Gaoping,LIU Xiaomeng,DANG Liming,GAO Fei

(College of Information System Engineering,Information Engineering University,Zhengzhou 450001,China)

AbstractCurrently,FPGA on VPX platform board usually loads configuration data from nonvolatile memory initiatively when power-on occurs,which has the disadvantage of inflexibility.This paper presents a multiple boards FPGA dynamic configuration method based on CPU+SPI bus+CPLD which offers FPGA configuration on boards without opening the box on VPX platform.It takes about 7 seconds to configuring data of 10.9 MB by this method with good flexibility and reliability.

KeywordsVPX;FPGA;dynamic configuration

doi:10.16180/j.cnki.issn1007-7820.2016.05.007

收稿日期:2015-09-29

作者简介:陈昌明(1988—),男,硕士研究生。研究方向:电子系统设计。邵高平(1964—),男,教授,硕士生导师。研究方向:电子系统设计。

中图分类号TN709

文献标识码A

文章编号1007-7820(2016)05-023-03