基于FPGA的简易数字信号发生器设计

2016-05-30杨巍

杨巍

摘 要:数字信号发生器作为科研和从事电子设计工作的一项重要设备,相比传统的模拟信号发生器,它具有测量信号的准确度高、精度高、变换速度快等优点。文献介绍的一种数字信号发生器,是由FPGA芯片通过设计并制作完成的。文中重点讨论了如何用FPGA实现码率、滤波器设计、恢复时钟的电路设计等,可为参与数字信号发生器设计的工作人员提供一定的参考价值。

关键词:数字信号发生器;FPGA;滤波器;恢复时钟

中图分类号:TP2735 文献标识码:A 文章编号:1006-8937(2016)05-0081-02

1 设计的基本要求

本数字信号发生器要求输出5V-TTL电平,其中高电平为2.4 ~5 V,低电平为0 ~0.4 V,码率为10~100 kpbs,步进率为10 kpbs,误差小于1%。

2 芯片的选取与论证

2.1 方案1

采用高性能单片机,如ARM公司的Cortex-M3,它是32位的CPU,具有完全基于硬件的中断处理,并可用定时器做10 us、11.1 us、12.5 us、14.3 us……的定时中断,在中断服务函数里做移位、异或运算,可以实现设计要求要求,但性能稍显勉强。

2.2 方案2

采用CPLD/FPGA芯片,如xilinx的artix-7系列的FPGA芯片。在设计的技术参数中有伪随机噪声10Mbps的码率要求,故均采用CPLD/FPGA比较合适。由于设计允许的码元周期的最大误差为:1/100 k,1/101 k = 99 ns,1/99 ns = 10.1 MHz,因此CPLD/FPGA的工作时钟大于10.1MHz即可保证1%的码率误差。

目前大部分主流的单片机、CPLD、FPGA的IO电平为3.3 V-LVCMOS,或3.3 V-LVTTL,其输出特性是可以满足TTL电平输出要求的。

综上所述,应选用FPGA的核来完成本次数字信号发生器的设计。

3 滤波器的设计

数字信号发生器中对滤波器的要求是:截止频率100 kHz、200 kHz、500 kHz,误差不大于10%,在100 kbps的码率下,数百kHz的截止频率已比较接近传输带宽要求,用于模拟非理想信道的传输特性。10%的误差要求并不算高,但如果采用运放做有源滤波器,应考虑运放的非理想特性,设计电路后,可采用具体的仿真模型仿真整个电路,修调R、C值,以达到要求。且设计成通带增益0.2~4.0可调,滤波与4倍增益可同时完成,然后通过电位器分压,也可电位器分压后在经过4倍同相放大。

此外,带外衰减不小于40 dB/Dec,因此要考虑至少采用2阶及以上的滤波器,因实际滤波器可能不够精准,为求稳妥,最好采用3阶滤波器(60 dB/Dec)。当然,也可采用3阶无源滤波器,电路简单,但需匹配输入、输出阻抗,误差也不易做小;如果采用运放做有源滤波器,只需1~2个运放完成;或者采用通用滤波器芯片,如美信公司的MAX297(低通滤波器)和MAX263(高通滤波器)来直接完成。

3.1 采用运放实现

我们设计中采用Filter Solution,TI-TINA等软件设计滤波器,运放可采用TL081(082, 084)等常见运放芯片,其带宽增益积为3 MHz,满足这里的滤波器要求。

最大增益时输出信号电压 0 ~20 V,因一般运放最大供电电压约30 V,可采用同相滤波放大配合不对称电源供电(25 V, -5 V),如果要在滤波同时做放大,不宜做反相放大,否则电源供电难于处理。由运放实现的滤波电路,如图1所示。

3.2 采用专用芯片实现

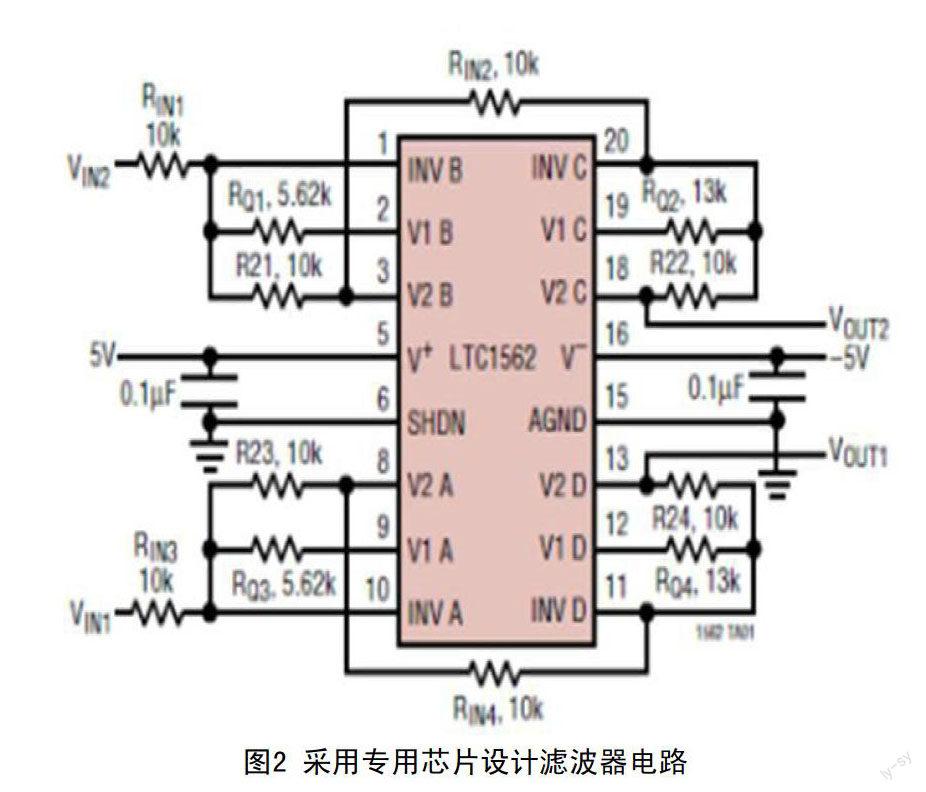

我们可以采用通用高通或低通滤波器,例如LT1562-2和LT1568,使用时在外部仅需使用电阻配置截止频率,若用LT1562-2,则需四个可组成一个2阶单元,可配置为两个4阶滤波器,通带带宽为20~300 kHz;若用LT 1568,则需两个芯片,组成一个2阶单元,也可配置为一个4阶滤波器,通带带宽为 200 kHz~5 MHz。

在具体应用时要注意的是,它们的供电电压最大为双5V,不能提供增益,若用于此设计,必须另外在后级做4倍增益。由专用芯片设计的滤波器电路,如图2所示。

4 伪随机信号发生器的设计

此部分设计与数字信号发生器相似。设本原多项式:

f2(x)=1+x+x4+x5+x12

码率10 Mbps,因此此部分设计必须采用CPLD或FPGA来完成,10 Mbps的码率下,该伪噪声的功率谱密度在数百kHz处已非常平坦,完全可当做白噪声处理。输出峰峰值100 mV,误差不大于10%,CPLD/FPGA输出后通过电位器分压并调整准确,但最好后面用运算放大器做电压跟随电路。

5 恢复时钟电路的设计

本设计的编码信号(数字基带)的码率是不确定的(11种可能值),为恢复时钟增加难度。通常而言,恢复时钟电路的设计方法有滤波法、锁相环法、直接测周/测频法。

5.1 滤波法

将基带信号进行波形变换后使用窄带滤波器提取其中的时钟频率成分,但本题基带码率不确定,不宜采用;如果穷举11种码率需要11个窄带滤波器,太复杂。

5.2 锁相环法

采用异或门鉴相器的锁相环,锁定范围有限(±90 °相差,两倍频以内),对于本题不太实用,采用11种不同的初始频率去穷举或许可以,但没有仿真或实验验证。

5.3 双触发器鉴频法

当编码输入相位超前时,环路滤波计数器加计数,数控振荡器计数步进(相角步进)增加,输出频率增加。实际上,NCO初始化频率取决于环路滤波计数器的初始值。本设计采用上述方法完成恢复时钟的设计,除此之外,我们还可以采用方法4和方法5来完成设计。

5.4 直接测周并同步

我们可以检测一小段时间内曼码的最大/最小跳沿间隔(码元周期/周期的一半),让计数器以此为模循环计数,并在合适地跳沿出现时清零。

5.5 直接测频并同步

这种方法是在一小段时间内计曼码的跳沿个数,根据4/3的关系确定码率,确定码元周期,让计数器以此循环周期计数,并由曼码的跳沿清零。

6 TTL电平和幅度的控制

根据前面所述,希望TTL输出高电平接近上限5 V,可采用 5 V供电的74HCT244作缓冲输出,其输入高电平仅要求2 V以上,可接受FPGA的输出,而输出可以很接近电源轨。

在这里,我们将74HCT244输出后经过电位器控制衰减后在经过运放进行电压跟随,以保证电平输出的低输出内阻。电路如图3所示。

7 结 语

数字信号发生器的设计是一项很复杂的工作,限于篇幅,在此文中只能介绍有限的设计方法和经验,望同行的科技工作人员和学者多提宝贵意见,让我们把数字信号发生器做得更好。

参考文献:

[1] 秦龙.MSP430单片机常用模块与综合系统实例精讲[M].北京:电子工 业出版社,2007.

[2] 黄根春,周立青,张望先.全国大学生电子设计竞赛教程-基于TI器件 设计方法[M].北京:电子工业出版社,2011.

[3] 罗杰.Verilog HDL与FPGA数字系统设计[M].北京:机械工业出版社,

2015.