基于DSP Builder三相锁相环的设计

2016-05-14罗文清劳雪婷吕玉波刘畅

罗文清 劳雪婷 吕玉波 刘畅

摘 要:传统三相锁相环的设计方法占用资源多,开发效率低下,针对这一特点,该文在DSP Builder环境下实现了三相锁相环的设计。在Simulink环境下进行建模仿真后,利用Signal Compiler模块将MDL文件直接转化为可综合的硬件描述语言,整个过程无须人工编程。最后,将HDL代码下载到FPGA芯片上进行实物验证。结果表明,此三相锁相环可以快速实现精确锁相,验证了该设计方法的可行性和有效性。

关键词:DSP Builder 三相锁相环 现场可编程门阵列 硬件描述语言

中图分类号:TM76 文献标识码:A 文章编号:1672-3791(2016)03(a)-0019-02

在直流输电、无功补偿等场合中,均要求准确获取电网电压相位信息。目前,工程上多以数字信号处理器为核心,实现离散域的三相锁相环(PLL)算法,虽然具有编程灵活的优点[1],但是算法中的三角运算、乘法运算占用了大量CPU资源[2]。而现场可编程门阵列(FPGA)以硬件电路形式并行运行,不存在占用CPU资源的问题,更适合于工程现场。文献[3]以FPGA器件为核心实现了快速锁相,但是其基于底层Verilog HDL硬件描述语言的开发手段,存在开发效率低、优化困难等缺点。

针对上述问题,该文采用一种全新的设计方案,实现三相锁相环的快速建模与功能实现。在分析锁相环基本工作原理之后,对所建立的PLL模型进行了传输门级仿真。仿真结果验证了该方案的可行性和有效性。

1 三相锁相环的工作原理

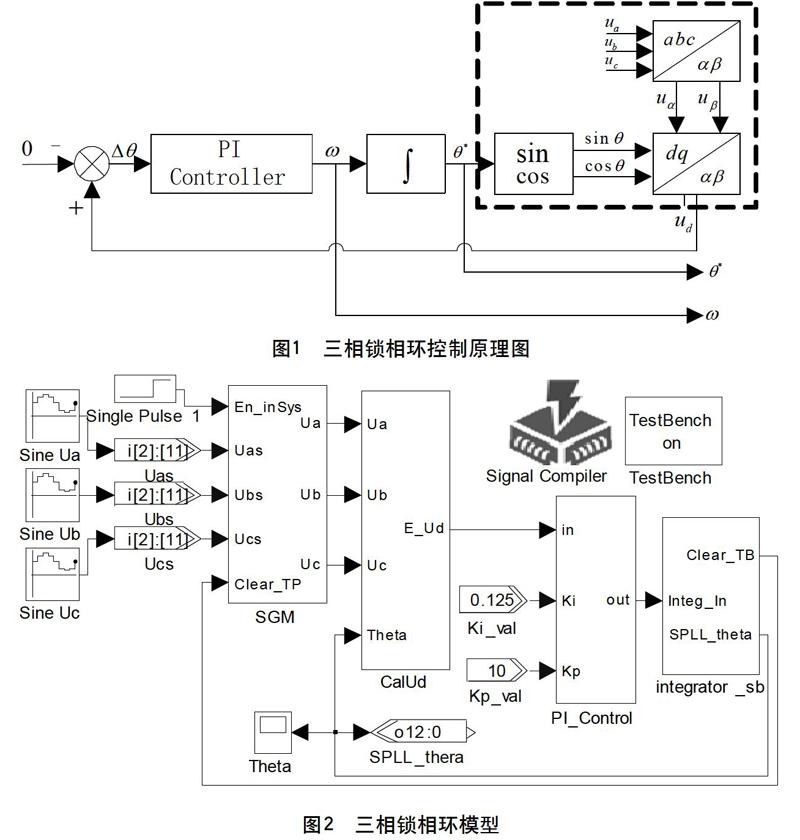

基于同步旋转坐标变换的三相锁相环主要由dq变换矩阵(鉴相器)、PI反馈控制系统以及积分器组成,如图1所示。归一化后的鉴相器输出为:,其中为PLL相位,为电网实际相位。假设锁相环锁定电网相位时,锁相环输出相位与实际电网相位几乎相等,鉴相器输出经过反相器后得到误差信号,经过PI控制器得到电网角频率,经过积分环节得到电网相位。系统经过PI环节、积分环节、同步旋转坐标变换构成一个反馈,当时,实现精确锁相。

2 DSP Builder下的PLL建模

DSP Builder是Altera公司推出的内嵌于MATLAB/Simulink之中的系统级设计工具,采用图形界面进行建模、设计和仿真。通过调用Blockset库下的Signal Compiler模块,可以将Simulink的设计文件(.mdl)直接转换成硬件描述语言,避免了人工大量编写、优化代码的工作。

DSP Builder建模时需要采用Altera提供的Blockset库,该库中的模块不能与标准的Simulink直接相连。因此需要定义DSP Builder的边界,由input模块与output模块确定,分别代表边界的开始与结束。根据三相锁相环的工作原理,该文在DSP Builder环境下建立了如图2所示的PLL模型。该模型主要由CalUd模块、PI模块、积分模块组成。此外,在顶层模型中需要加入Signal Compiler模块,可选加入TestBench模块用于功能仿真。模型中PI控制器的积分环节由Integrator模块实现,PI控制器的比例环节由Multiplier模块实现。

3 HDL代码生成与验证

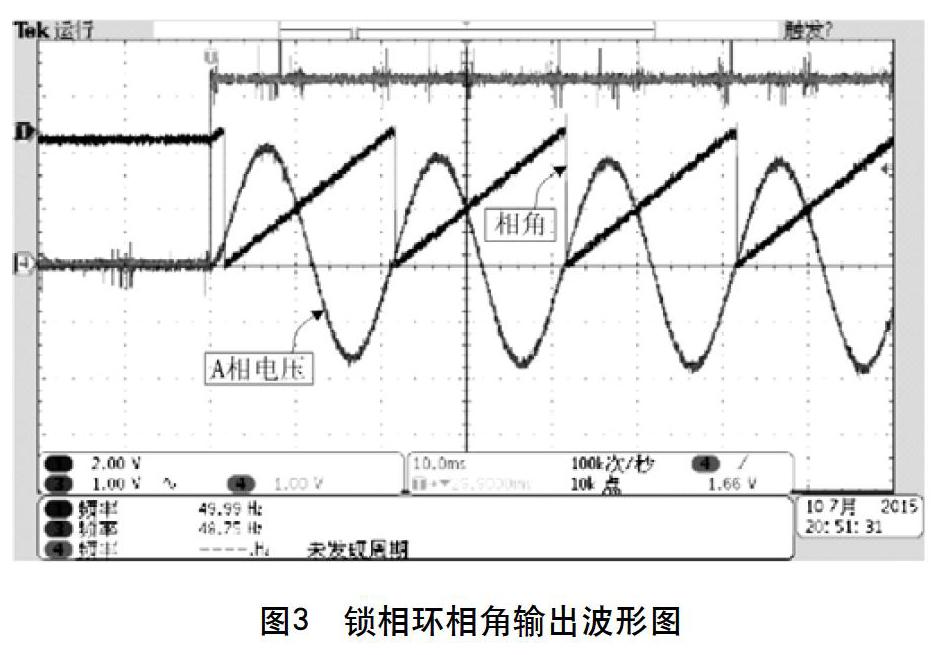

在DSP Builder环境中完成系统级验证后,需要将PLL模型转换成可以综合的HDL代码。转换步骤如下:打开模型中的Signal Compiler模块,设置Family参数为Cyclone I,Device参数为AUTO,点击Compile按钮,DSP Builder自动调用QuartusII软件进行综合并生成网表文件。QuartusII综合无误后,选择Export标签,选择保存目录即可自动生成VHDL代码。此外,mdl仿真模型的仿真属于系统级仿真不同于HDL代码的功能仿真,因此需要对HDL代码进行功能仿真。调用模型中的TestBench模块,打钩ModelSim GUI复选框,运行后会自动生成HDL输入激励文件,并调用ModelSim仿真软件对HDL代码进行功能仿真,整个过程无须人工干预,也无须编写复杂的激励文件,从而实现HDL代码的快速验证。图3为三相锁相环的实际跟踪效果图。可以看出,锁相环在2~3个周波内实现了精确锁相,性能优良。

4 结语

该文分析了三相锁相环的工作原理,在DSP Builder环境下搭建了三相锁相环的系统模型。并且利用TestBench工具对生成的HDL代码进行了快速验证与仿真。最后将HDL代码下载到FPGA芯片上进行验证。结果表明,基于DSP Builder的三相锁相环设计方法可以快速实现模型搭建与算法设计,缩短了设计周期,提高了设计的灵活性,为FPGA快速开发提供了一种新方法。

参考文献

[1] 杨华.基于DSP28335的软件锁相环及其在PWM整流器中的应用[J].船电技术,2013(11):19-23.

[2] Se-Kyo Chung.A phase tracking system for three phase utility interface inverters [J].IEEE Transactions on Power Electronics,2000,15(3):431-438.

[3] 刘超,庄圣贤,刘思佳,等.基于FPGA的三相电网故障环境下锁相技术分析[J].电子科技,2014(9):148-152.