基于FPGA的数字脉冲压缩算法的设计与实现

2016-04-28高星

高 星

(中国船舶重工集团公司第723研究所,扬州 225001)

基于FPGA的数字脉冲压缩算法的设计与实现

高星

(中国船舶重工集团公司第723研究所,扬州 225001)

摘要:介绍了雷达信号处理系统中脉冲压缩技术的现场可编程门阵列(FPGA)实现方法,研究和分析了线性调频信号的脉冲压缩算法,结合研究目标和设计要求,设计了一种基于数据分段的脉冲压缩处理方法,通过SignalTap仿真证明了其有效性。

关键词:现场可编程门阵列;脉冲压缩;数据分段处理

0引言

当要求雷达探测目标的作用距离增大时,需要加大信号能量E,同时增加信号能量可以提高接收信号的信噪比,因此增大信号能量就变得很重要。增大发射机的脉冲功率是增加信号能量的一个途径,但它受到发射管峰值功率及传输线功率容量等因素的限制,只能在一定范围内起到作用[1]。在发射机平均功率允许的条件下,也可以用增大脉冲宽度τ的办法来增加信号的能量,但增大τ又会降低距离分辨力。非常短的脉冲信号可以极大地提高雷达的距离分辨力,然而使用短脉冲信号降低了平均发射功率,由于平均发射功率与接收机信噪比直接相关,平均发射功率越高,接收机的信噪比越高。故此,增加脉冲宽度(即提高平均发射功率)和提高雷达的距离分辨力之间存在着不可调和的矛盾。为了解决这一矛盾,研究人员陆续开始研究利用“复杂波形”来代替传统的矩形脉冲信号。最早获得实际应用的就是线性调频信号,线性调频信号是通过线性频率调制(LFM)来获得大时宽带宽积的,采用这种信号的雷达可以同时获得远作用距离和高距离分辨力。它具有以下优点:所用匹配滤波器对回波信号的多普勒频移不敏感,因而可以用一个匹配滤波器来处理具有不同多普勒频移的信号。其主要缺点是存在距离与多普勒频移的耦合及匹配滤波器输出旁瓣较高,为压低旁瓣常采用加窗处理。近年来,由于高速模/数(A/D)转换器、高速高密度现场可编程门阵列(FPGA)等数字技术迅速发展[2],以数字技术实现的脉冲压缩被广泛采用。

1频域数字压缩原理

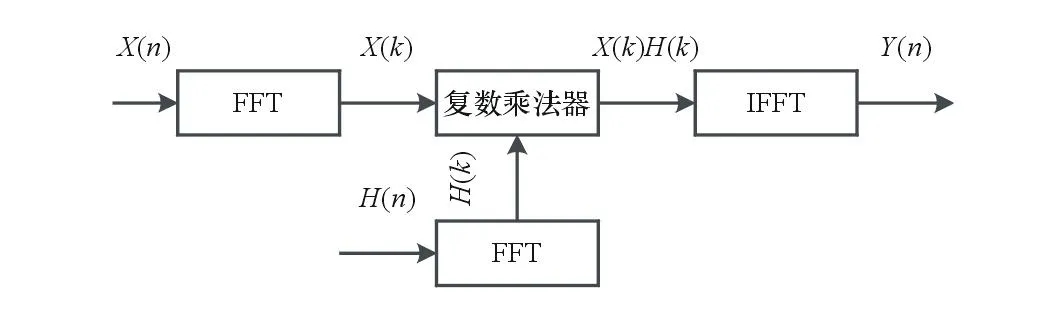

脉冲压缩包括发射宽脉冲和处理接收回波以获得窄脉冲[3]。这样脉冲压缩雷达既保持了窄脉冲的高距离分辨力,又能获得宽脉冲雷达系统的强检测能力。在脉冲压缩系统中,发射波形往往在相位上或频率上进行调制,接收时将回波信号数字下变频后进行匹配滤波。当脉冲压缩匹配滤波在频域通过复数相乘实现时,称为频域数字脉冲压缩。根据数字信号处理和脉冲压缩相关理论知识可知,频域脉冲压缩处理的过程可由下式表示:

Y(n)=PIFFT[X(k)×H(k)]=

PIFFT{PFFT[X(n)]×PFFT[H(n)]}

(1)

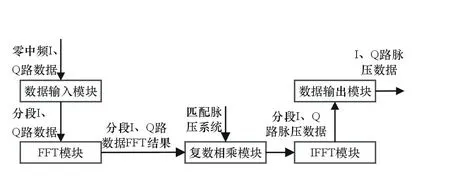

上式的实现原理框图如图1所示。

图1 频域脉冲压缩结构

频域脉冲压缩处理的优点是利用快速傅里叶变换(FFT) 实现了信号的时域到频域转换,对于大时宽带宽积信号,在计算量和硬件资源消耗的规模上均大大小于时域卷积运算。而其主要缺点则是频域脉冲压缩属于批处理算法,即必须对整个脉冲重复周期内的回波数据同时进行处理,如果脉冲压缩重复周期内的回波数据量太大,一般的硬件处理速度比较难满足实时性要求,故其较适用于部分距离范围内的脉压处理,若要实现全距离范围内的脉压,则需要采用距离分段处理或并行处理方式来实现[1]。距离分段处理原理如下:设雷达回波数据序列长度为P,脉压系数序列长度为M,将P平均分为m段,每段长度为N=P/m,每段输入子序列为:

si(nT)=si(nt),iN≤n≤(i+1)N-1,

(2)

则输出子序列为:

(3)

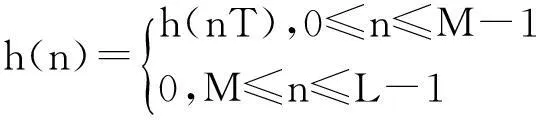

为了在频域上实现上式的线性卷积,需对每个子序列 si(nT)及 h(nT)分别补零扩展成长度为L=M+N-1的序列:

si(n)=

(4)

(5)

对每一个补零后的子序列完成子序列频域脉冲压缩:

(6)

对soi(k)进行L点离散傅里叶逆变换(IFFT)即得到各子序列的脉冲压缩输出 soi(n):

(7)

最后将各个子脉冲压缩序列以 M-1的重叠长度进行重叠相加,即得到原整个雷达回波序列的脉冲压缩结果:

(8)

2脉冲压缩电路设计

本文设计了一种距离分段复用的脉冲压缩方法,该方法基于单片FPGA的硬件平台,采用频域数字脉冲压缩技术,巧妙运用重叠相加法原理,以一套脉冲压缩模块在一个脉冲周期内实现了大时宽调频信号的脉冲压缩处理。本雷达在不同工作模式下所发射波形的参数有所不同。为了满足本雷达在不同模式下的工作要求,要求所设计的脉冲压缩电路参数具有可重配置的特点(如脉压系数可实时配置,处理窗可任意选择等)。同时,雷达信号处理的一个很重要的要求就是实时性,由于雷达信号的数据量大小与波形相关参数有关,且往往很大,所以并不是很容易实现数据的实时处理。下面结合雷达波形的有关指标参数,对脉压电路性能要求进行分析:

本雷达最大处理量程为24 km,处理距离单元数为 1 600个,由于待处理的距离单元数较大,故采用距离分段脉压处理。

本雷达最大时宽带宽积为320,此时线性调频信号带宽为 20 MHz,信号脉宽为 16 μs。所以设计的FFT(IFFT)最小为512。本雷达最大重复频率为10 000 Hz,即最小脉冲重复时间(PRT)为100 μs,本设计中取FFT(IFFT)点数为 1 024,时钟为80 MHz。此时,完成一次距离分段脉冲压缩的时间约为50 μs左右,符合最小PRT要求。

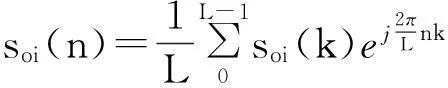

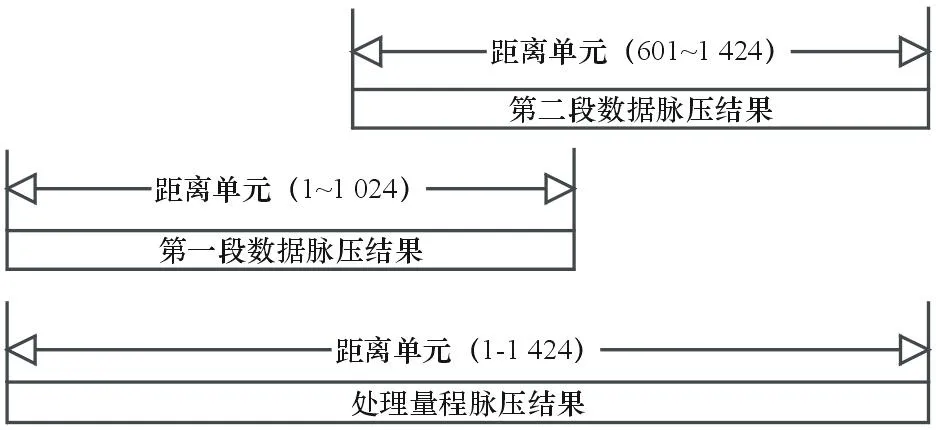

由以上分析,以10 km处理量程示例给出距离分段结果。该处理量程共有1 424个距离单元。第1段为1~1 024个距离单元,第2段为601~1 624个距离单元,超过处理范围的距离单元数补零。距离分段结果如图2所示。

图2 距离分段示意图

先对每段数据进行脉压处理,然后再将2个数据段的脉冲压缩结果进行距离单元拼接,由于第601~1 024个距离单元为2段数据所重叠的部分,选取其中一段中的即可。第1段数据保留第1~600个距离单元,第2段数据保留第601~1 424个距离单元,将第2段保留的数据接在第1段保留的数据后,总长度为1 424的数据脉冲压缩处理完成。距离拼接结果如图3所示。

图3 距离拼接示意图

3基于FPGA的实现方法

整个脉冲压缩系统由5个子模块组成,如图4所示。

图4 脉冲压缩电路系统架构图

(1) 数据输入模块。数据输入模块是整个脉冲压缩系统的重要组成部分,对雷达处理量程内的零中频回波信号数据,按照上节的距离分段脉压要求分割成若干距离单元数据片段,并对最后一个距离单元数据片段进行补零操作。

(2) FFT 运算模块。FFT 运算模块是整个脉冲压缩系统的重要组成部分,是脉冲压缩电路中的2个主要运算单元之一,用于实现数据由时域到频域的转换。根据脉冲压缩电路设计的 FFT 运算模块中的 FFT 点数为 1 024,通过Quartus中的具有FFT功能的IP核,分别对每个数据片段进行FFT运算。

(3) 复数相乘模块。复数相乘模块通过只读存储器(ROM)完成线性调频波形匹配系数的配置,同时对FFT运算模块输出的数据片段进行实时复数相乘处理。

(4) IFFT 运算模块。IFFT 运算模块用于实现数据由频域到时域的转换,通过Quartus中的具有FFT功能的IP核,对复数相乘模块输出的数据片段进行IFFT处理。

(5) 数据输出处理模块。数据输出处理模块先根据输出数据幅度要求对 IFFT 运算模块的输出数据幅度进行调整,然后对已经完成脉冲压缩处理的数据片段进行拼接操作并舍去无效数据,保证输出的脉冲压缩数据的正确性。

4仿真与结果分析

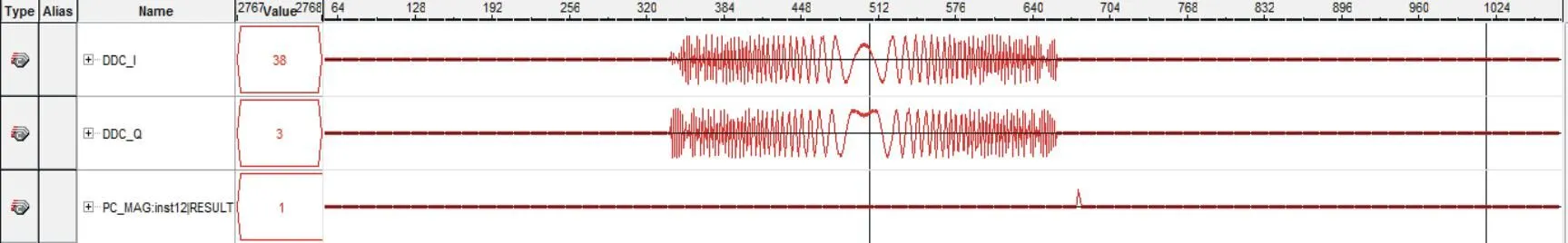

本设计采用Altera公司的StratixⅡ系列的EP2S180F1020I4型FPGA来实现距离分段脉冲压缩模块的设计。对10 km量程,使用Quartus调试工具逻辑分析仪SignalTapⅡ来观测FPGA硬件实现结果,其中脉压前后运用SignalTapⅡ观测到的信号波形如图5所示。

SignalTap观测时钟为20 MHz,其中DDC_I为零中频I路信号,DDC_Q为零中频Q路信号,PC_MAGinst12∣RESULT为脉压输出结果。可以看出,脉压主副比满足要求。

图5 线性调频波形脉冲压缩结果图

5结束语

本文对数字脉冲压缩处理算法进行了研究,针对研究对象和设计目标进行了较深入的分析比较,确定了脉压处理方案。

利用Altera公司的StratixⅡ系列FPGA器件实现了距离分段数字脉冲压缩算法,在做实时信号处理时,该设计能够使资源优化,并且满足运算速度的要求,实现起来也不复杂,在实际工程中有很强的运用价值。

参考文献

[1]丁鹭飞,耿富录,陈建春.雷达原理[M].4版.北京:电子工业出版社,2011.

[2]EDA 先锋工作室.Verilog HDL实用精解——轻松成为设计高手[M].北京:北京航天航空大学出版社,2012.

[3]马晓岩,向家彬.雷达信号处理[M].长沙:湖南科学技术出版社,1999.

Design and Implementation of The Digital Pulse Compression Algorithm Based on FPGA

GAO Xing

(The 723 Institute of CSIC,Yangzhou 225001,China)

Abstract:This paper introduces the implementation method of field-programmable gate array (FPGA) for pulse compression technology in the radar signal processing system,studies and analyzes the pulse compression algorithm of linear frequency modulation (LFM) signal;designs a pulse compression processing method based on segmented data combining with the study objectives and design requirements,proves its validity through SignalTap simulation.

Key words:field-programmable gate array;pulse compression;segmented data processing

DOI:10.16426/j.cnki.jcdzdk.2016.01.018

中图分类号:TN957.51

文献标识码:A

文章编号:CN32-1413(2016)01-0085-04

收稿日期:2015-10-16