叠层芯片引线键合技术在陶瓷封装中的应用

2016-03-23廖小平

廖小平,高 亮

(无锡中微高科电子有限公司,江苏 无锡 214035)

叠层芯片引线键合技术在陶瓷封装中的应用

廖小平,高 亮

(无锡中微高科电子有限公司,江苏 无锡214035)

摘 要:随着集成电路封装技术朝着高密度封装方向发展,同时基于系统产品不断多功能化的需求,出现了叠层封装技术。介绍了芯片叠层封装的传统引线封装结构,详细阐述了一种新型的芯片十字交叉型叠层封装结构,并结合这种封装结构在陶瓷封装工艺中的应用进行了具体实施与探讨,并进行了引线键合可靠性考核试验。通过试验研究表明叠层芯片引线键合技术也可广泛应用于陶瓷封装产品中。

关键词:叠层芯片;悬空键合;低弧键合;3D封装

1 引言

陶瓷封装是以陶瓷材料为基体、以柯伐合金为盖板进行封接的气密性封装,由于气密性好,封装体具有很高的可靠性,同时还可实现多信号、地和电源层结构,并具有对复杂的器件进行一体化封装的能力。陶瓷基板技术也已经达到一百多层布线的能力,可以将无源器件如电阻、电容、电感等都集成在陶瓷基板上,实现高密度封装。它的散热性也很好。陶瓷封装由于其卓越性能,在航空航天及大型计算机等众多领域都有广泛的应用。

近年来,国产化航空航天电子产品对更高性能、更低功耗的不断增长需求推动国产化微电子陶瓷封装向密度更高的三维封装方式发展,三维封装不但提高了封装密度,而且也减小了芯片之间互连导线的长度,从而提高了器件的运行速度,而且通过多层封装还可以实现器件的多功能化。芯片叠层封装就是一种得到广泛应用的三维封装技术。初级的3D芯片叠层封装就是把多个芯片在垂直方向上累叠起来,利用传统的引线封装结构,然后再进行封装。其传统的引线封装结构主要有2种:一种是金字塔型的叠层封装,使用大小不同的芯片,上层芯片的面积要小于下层,这样下层芯片表面就有足够的面积和空间可以用来进行引线键合;另一种是使用大小相同的芯片,通过在上下层芯片之间加入一层垫片以便于下层芯片的引线键合,垫片是一块面积比上下层芯片小的普通硅片[1~5]。

但是在进行多芯片叠层时, 也并非所有的芯片叠层方案都可以用以上两种封装结构实施,在此基础上发展了一种十字交叉型的叠层封装。本文就十字交叉型叠层封装技术在陶瓷封装工艺中的应用进行了试验验证和讨论。

2 叠层芯片的引线键合

2.1键合材料的准备

为验证十字交叉型叠层封装技术是否可应用于陶瓷封装工艺中,采用镀金硅片代替裸芯片,通过设计5种不同尺寸(4 mm×3 mm,4 mm×2 mm,3 mm× 2 mm,3 mm×1.5 mm,2 mm×1 mm)的镀金硅片,选择CQFP240陶瓷外壳,芯片叠层5层,键合丝采用贺力氏(常熟)有限公司生产的Φ30 μm HD2的金丝。

2.2试验方法

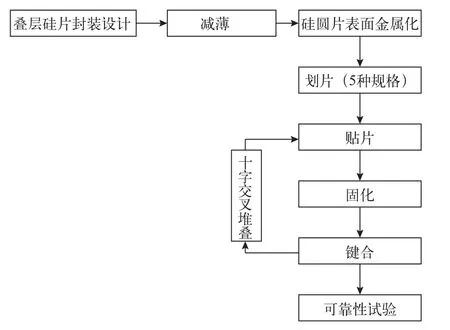

本项目采用磨削设备把硅片减薄到150 μm,采用表面蒸镀设备对硅片表面进行金属化,然后采用切割设备把硅片划成5种不同的规格,尺寸分别为4 mm× 3 mm,4 mm×2 mm,3 mm×2 mm,3 mm×1.5 mm,2 mm×1 mm,用绝缘胶进行贴片,然后经过150℃、1 h固化,采用超声金丝球焊机进行键合,键合过程中采用高纯氧化铝制作的陶瓷劈刀(美国SPT公司生产),将直径为30 μm的金丝(常熟贺力氏有限公司生产,拉断力大于11 g)键合到镀金硅片上。通过重复贴片工艺和键合工艺进行硅片的十字交叉型叠层键合。

其详细的工艺流程如图1。

键合可靠性试验采用Dage4000微测试仪,测量经过300℃、1 h烘烤前和经过300℃、1 h烘烤后的金丝抗拉强度和金球抗剪强度来表征其键合可靠性,测试拉钩位置位于每根线的最高点下方即弧线最高点的下方。

2.3键合工艺参数

十字交叉型叠层芯片的成功有引线键合,其键合工艺参数的正确应用起到至关重要的作用,如线弧高度、控制线弧形状参数、键合压力、控制外悬芯片引线键合参数等。

图1 十字交叉型叠层封装工艺流程图

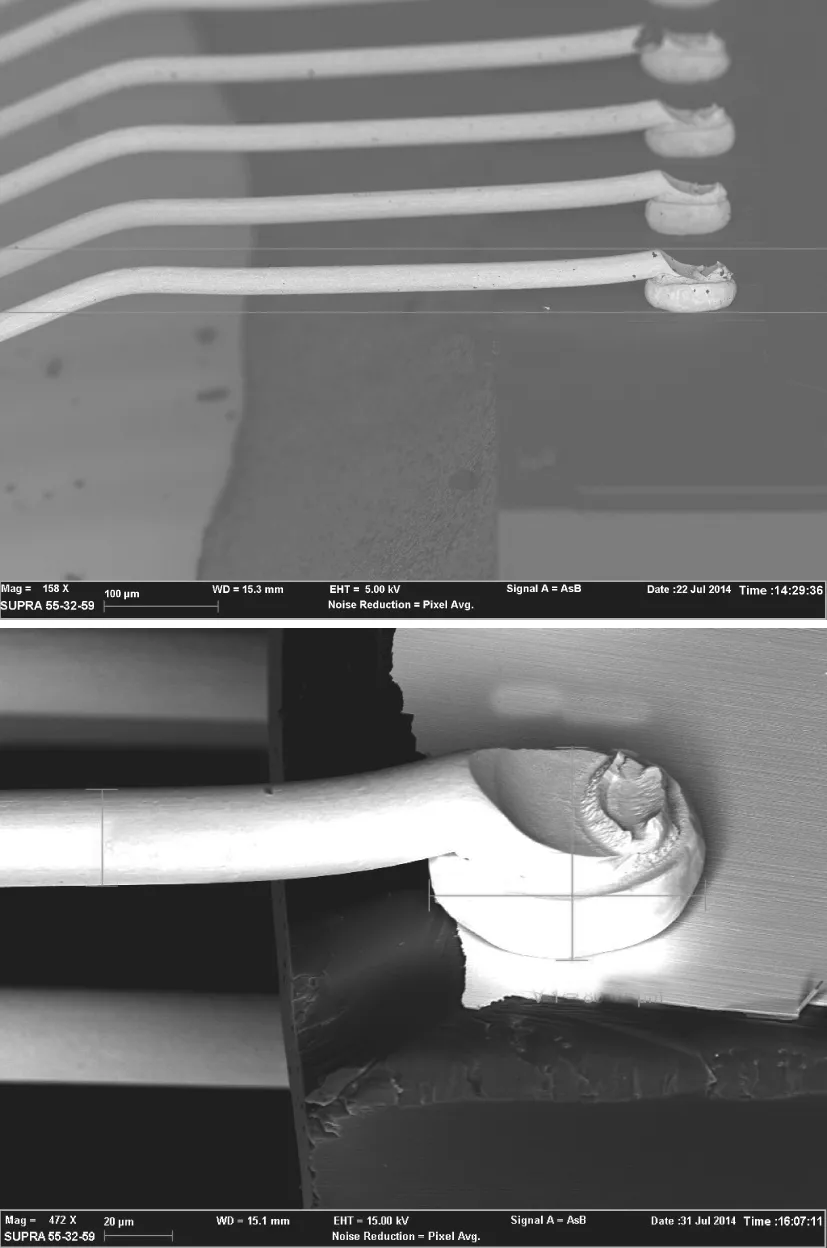

由于芯片厚度的降低和叠层芯片层数的增加,十字交叉型叠层芯片引线键合技术涉及到低线弧键合技术,而传统的引线键合技术形成的线弧高度一般在200 μm左右,难以满足叠层芯片的低线弧键合需求。目前,采用反向拱丝键合技术可以成功实现线弧高度为50 μm的引线键合,如图2。为了使传统的拱丝能满足低线弧的要求,通过调整线弧形状可以起到一定的作用。

图2 低线弧引线键合SEM照片

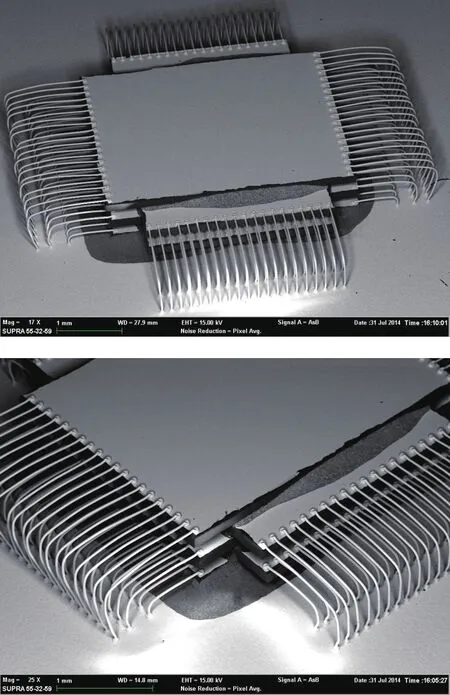

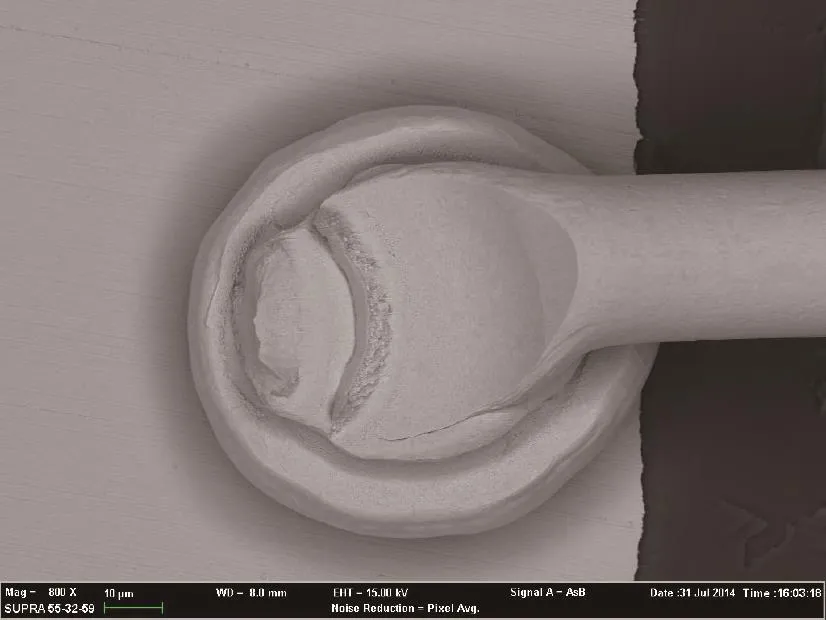

十字交叉型叠层芯片引线键合技术还涉及到外悬芯片键合技术, 而传统的引线键合技术根本无法解决外悬芯片的键合,其在键合过程中芯片边缘的弹性作用易导致外悬芯片碎裂、线弧不稳定、球形不一致和键合不上的问题。目前,采用控制并优化外悬芯片引线键合参数的方法可以解决这一问题,芯片堆叠5层的引线键合SEM照片如图3所示。

图3 芯片叠层5层的引线键合SEM照片

2.4键合质量检验

(1)键合点形变检查,对键合完毕的电路在显微镜下进行形变检查,叠层芯片和单芯片键合的电路其形变满足GJB548B-2005方法内部目检的要求,如图4所示。

图4 外悬引线键合的焊点形变SEM照片

(2)键合弧线外观质量检测,对键合完毕的电路在显微镜下进行弧线外观质量检查,检测结果正常,如图3所示。

(3)键合完毕后进行键合引线拉力强度测试,叠层芯片键合的引线拉力测试结果均满足GJB548B-2005方法2011.1的要求。

(4)键合完毕后进行金球抗剪强度测试(金球直径约80 μm),根据EIA/JESD22-B116球压焊的破坏性剪切试验方法,引线的金球抗剪强度最小测试值为35 g,均合格。

3 叠层芯片的引线键合可靠性试验

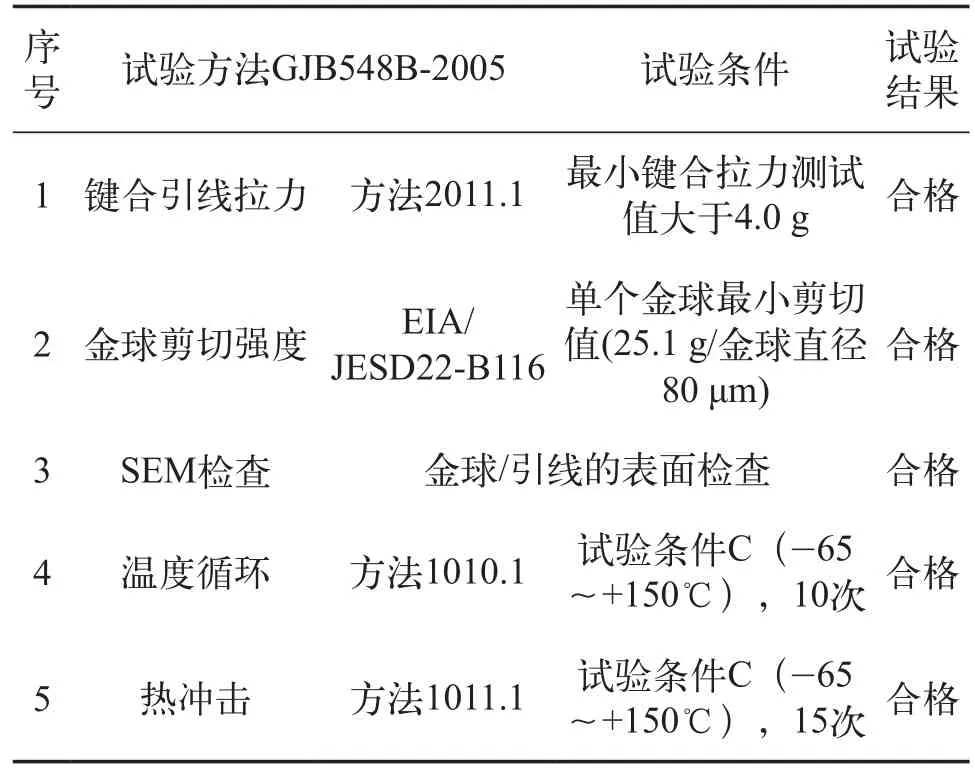

可靠性考核的试验条件如表1所示。

表1 绝缘引线键合电路可靠性试验条件

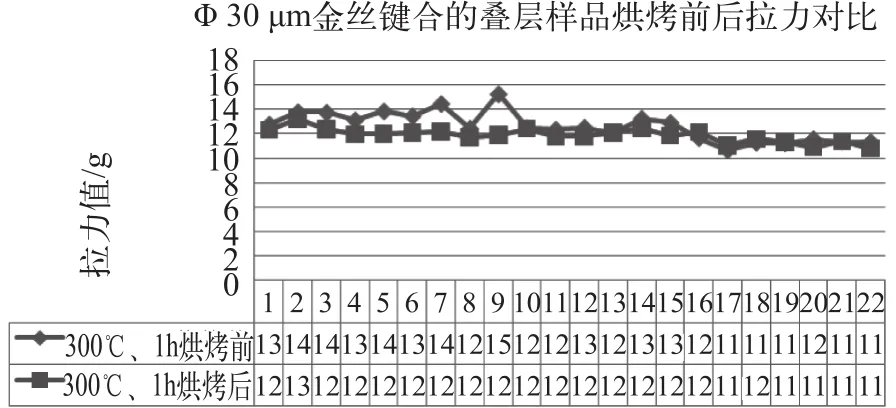

图5 300℃、1 h烘烤前后的叠层样品引线拉力值对比图

为了进一步验证键合的可靠性情况,进行300℃、1 h烘烤试验,试验后进行了引线键合拉力测试,测试结果如图5。从图中看出,烘烤后引线拉力值并没有出现明显的下降,拉力值均在10 g以上。从以上试验结果分析,通过叠层芯片有引线键合的电路能够通过相关可靠性考核试验,能够解决低线弧键合的技术难题,并防止键合引线产生“塌线”现象,还能够解决外悬芯片键合过程中芯片易碎、线弧不稳定、球形不一致和键合不上等问题。

4 总结

传统的引线键合技术在系统产品不断多功能化的需求及三维封装发展趋势的推动下,出现了叠层芯片引线键合技术。由于叠层封装的产品具有功能更多、性能更好、速度更快、功耗更低等优势,相信随着技术的进步及成本的降低,叠层封装产品的应用将涉及到各个领域,不仅仅局限于应用广泛的消费类产品,同时还将覆盖尖端科技产品,并在陶瓷封装领域得到广泛应用。

参考文献:

[1] 孙宏伟.叠层芯片封装技术与工艺探讨[J]. 电子工业专用设备,2006,136: 65-74.

[2] Li X, Wang J, Zhao L Y. The investigation of board-level vibration for the stacked memory device[C]. ICEPT Conference, 2014.

[3] GJB-548B. Test methods and procedures for microelectronic device[S]. 2005.

[4] Pang J W, Wang J, Zhao L Y. Study on the board-level drop test of the stacked memory device by FEA[C]. ICEPT Conference, 2014.

[5] Liu D S, Chao Y C, Wang C H. Study of wire bonding looping formation in the electronic packaging process using the three-dimensional finite element method[J]. Finite Elements in Analysis and Design, 2004, 40(3) : 263-286.

廖小平(1986—),男,江西宜春人,硕士,现主要从事集成电路封装技术研究与应用工作。

Application of Wire Bonding of Multi-Stack Die in the Ceramic Package

LIAO Xiaoping, GAO Liang

(Wuxi Zhongwei High-Tech Electronics Co., Ltd. Wuxi 214035, China)

Abstract:With the development of the integrated circuit packaging technology towards the direction of high density packaging, and based on the requirement of more functional system products, which have been promoting the development of multi-stack package. In this paper, the traditional typical stacked chip packages are introduced. A cross type which is a new type of stacked chip package is described in detail. The cross type application in the ceramic packaging technology is discussed, and the reliability test of wire bonding is also researched. According to the study conclusion, the technology of wire bonding of multi-stack die also can be widely used in the ceramic packaging products.

Keywords:multi-stack die; wire bonding on overhang; low profile wire bonding; 3D package

作者简介:

收稿日期:2015-11-26

中图分类号:TN305.94

文献标识码:A

文章编号:1681-1070(2016)02-0005-04