一种基于SOC低压低功耗带隙电压源

2016-03-10四川大学

四川大学 陈 峰 王 志 林 鑫 苏 平

一种基于SOC低压低功耗带隙电压源

四川大学 陈 峰 王 志 林 鑫 苏 平

在模拟电路中,基准电压源为电路里其他模块提供精确、稳定的电压基准偏置或者由其转化而来的电流基准偏置,基准电压源的性能往往直接影响到整个系统的精度和性能,随着集成电路特征尺寸的不断缩小以及SOC在便携产品中应用的迅猛发展,SOC设计不可避免地朝着低压和低功耗的目标前进。本作品采用了自偏置结构,使用华润上华0.18um工艺,在-45℃-120℃温度范围内进行仿真,本作品温度系数为6.6ppm/℃,在1kHz带宽内电源抑制比为46dB,功耗极低,版图面积仅有0.0003。

带隙电压源;低压低功耗;温度系数;面积小;自偏置

一、实验原理

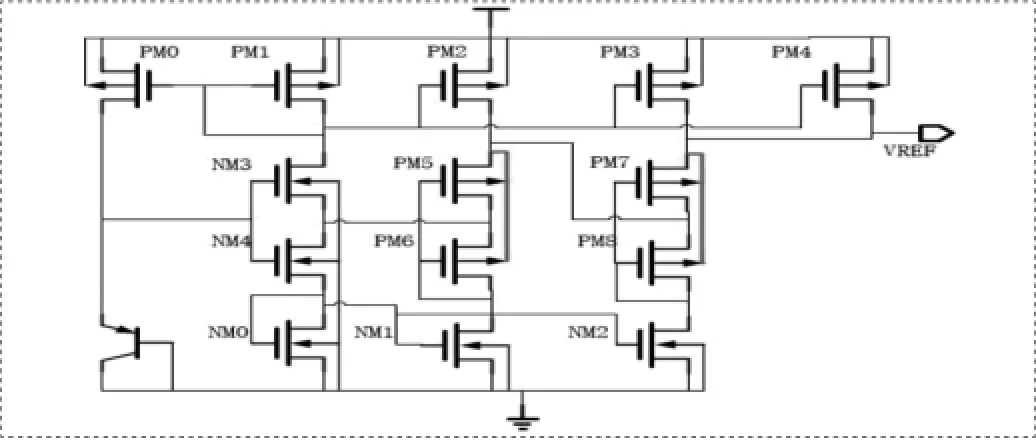

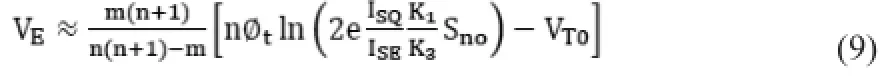

图1 带隙基准源电路图

电路原理图如图1所示,电路由一个三极管和三个self-cascode(SC)结构和电流镜构成。电流镜结构为三极管和SC提供电流,三极管的具有负温度系数,SC结构输出的电压是正温度系数。由三个SC结构的输出电压和M2栅源电压叠加而成,三极管的VBE以一定比例体现在M2栅源电压上,故M2栅源电压与温度负相关,而SC结构输出电压与温度正相关,通过调整三极管的参数和SC中MOSFET的参数完成温度补偿,获得基准电压VREF。

本电路主要改进的地方在于使用了两个pmos 组成的SC结构,同时,如图1所示,将两个“上”pmos的源级与其衬底(即n阱)连接,以抑制衬底调制效应,提高了精度和电源抑制比。

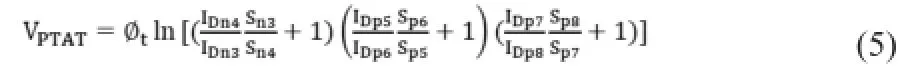

(一)PTAT电压的产生

本电路主要利用self-cascode 结构来产生具有正温度特性的电压分量。

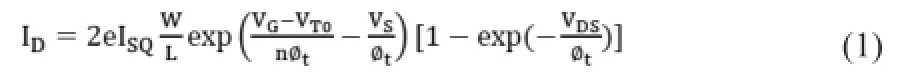

MOS管在亚阈值区的漏电流公式:

PTAT电压由三组自偏置(self-cascode /SC)结构产生,分别为NM3-NM4,PM5-PM6,PM7-PM8三组。

选取PM7-PM8结构,可以得到:

利用公式(1)和(2)可以得到:

其中:

从公式中可以看出,电压为对数函数关系,相对变化比较小,为了得到比较大的温度系数,因此串联多个SC结构,PTAT电压是由NM4、PM5和PM7的漏源电压总和提供:

(二)CTAT电压的产生

由推导可知,发射集电压取决于定义电路平衡点的过程参数,即:MOSFET的阈值电压VTO、特定的电流密度ISQ和结反向饱和电流ISE。

基准电压源:

二、仿真结果

采用华润上华0.18um工艺,利用华大九天公司Aether仿真工具对电路的温度系数、电源抑制比、线性度以及电路的启动时间进行仿真。

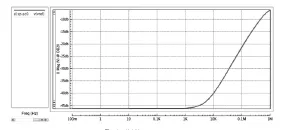

1.温度系数仿真

当电源电压为1.2V时,输出基准电压471mV,在-40℃-125℃范围内温度系数为6.65ppm/℃

图2 温度系数

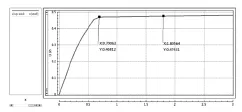

2.电压抑制比仿真

对电路进行交流仿真,电源电压为1.2V,在0.01Hz-1MHz范围内进行仿真,得出波形如下图所示,可以看出在低频范围内(0.01Hz-1kHz)电源抑制比稳定在-46Db。

图3 电压抑制比

3.线性度仿真

将电源电压从0V变化到3V,对电路进行仿真,基准电压和电源电压的关系如图4所示,可以看出,在电源电压为0.7V左右,基准电压源的基准电压输出开始稳定,在0.7-3V范围内,基准电压将比较稳定在0.47V左右,总体来说,该电路的线性度很好。

图4 线性度

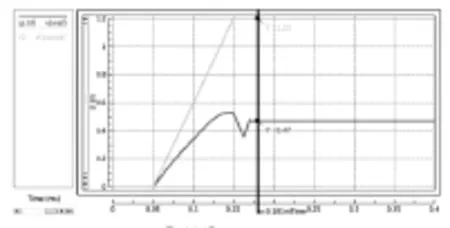

4.启动时间仿真

上电后对电路进行瞬态仿真,得到下图5。观察基准电压输出与时间的关系,可以看出,该电路在上电0.18ms之后输出电压才趋于稳定,即启动时间为 0.18ms,该启动时间可以满足大部分电路,为了适应于对启动时间更小的电路,可以牺牲版图面积,给该电路单独加一个启动电路,就可以将启动时间大大的降低。

图5 启动时间

5.功耗仿真

对电路进行仿真,可以测出,在-40℃-125℃范围内电路中电流大小从而可以得出电路的总体功耗。在室温下,电路电流非常小,仅有10.9104nA。

图6 电路功耗

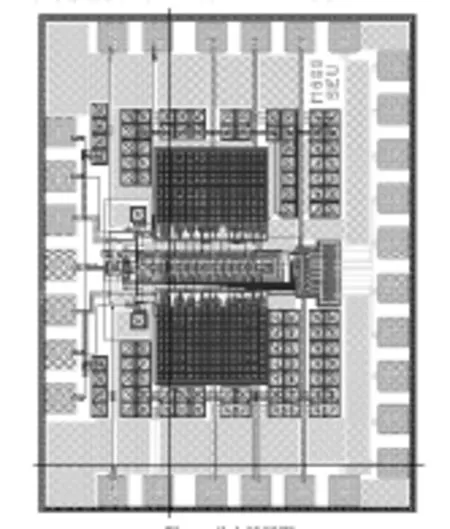

三、版图

版图设计如图7所示,总面积仅有17um*18.2um=309.4=0.0003。左下角为三极管部分,左上部和上面部分为电流镜部分,有显著特点是右边两个pmos对的SC结构,由于n阱电位的不同,需要与其它n阱保持一定距离。

图7 电路版图

四、结论

我们设计了一种基于SOC的低压低功耗的带隙基准源,采用华润上华0.18um工艺,并用Aether软件对我们的设计进行了验证。我们的电路采用自偏置结构,所以在没有启动电路的额情况下仍能自启动,这大大减小了电路的面积,可以降低成本,我们对自偏置结构进行了改进,使自偏置结构的衬底结统一的某一电位,以抑制衬偏效应,实验仿真证明,该改进的确提高了电路温度系数、电源抑制比等方面的性能。在电源电压为1.2V下,基准输出稳定在0.47V左右,且温度系数为6.6ppm/℃,该电路总体功耗为10nA,版图面积很小,仅有0.0003。由于低压低功耗,该基准电压源可应用的范围很广,如可穿戴智能设备等。

[1]Oscar E Mattia, Hamilton Klimach. 0.7 V Supply, 8 nW, 8 ppm/ oC Resistorless Sub-Bandgap Voltage Reference 05 June 2016.

[2]李燕霞,龚敏,高博.基于0.18 μm 的无电阻无运放低功耗带隙基准源设计[J].电子与封装,2015(1).

[3]吕阳,王春雷,朱杰,邱成军 一种极低功耗自偏置CMOS带隙基准源[j]电子世界.

陈峰(1995-),江西抚州人,大学本科,现就读于四川大学。

王志(1994-),四川成都人,大学本科,现就读于四川大学。

林鑫(1994-),福建人,大学本科,现就读于四川大学。

指导老师:苏平。

图2.3 总电路版图

3 总结

本文基于CSMC 0.18um CMOS工艺,设计了一款12位、200kS/s高精度低功耗SAR ADC。本文优化了电容型SAR ADC结构,采用改进型分段电容全差分结构,大大减小电路总电容值,节省电路面积,并提出非单调开关切换方案,降低功耗;选用栅压自举开关实现采样开关电路,提高了ADC的采样精度;采用动态比较器,降低电路功耗;提出改进型异步时序,减小关键路径延时。仿真结果表明:采样频率为200kS/s时,有效位数为11.1bit,信号噪声失真比为68.5dB,平均电流为11.7uA。

参考文献

[1]张理振.10Bit 30MSs低功耗SAR ADC设计[D].[硕士学位论文].南京:东南大学,2013.

[2]Michiel van Elzakker,Ed van Tuijl, Paul Geraedts, et al. A 10-bit Charge-Redistribution ADC Consuming 1.9uW at 1 MS/s[J].IEEE Journal of Solid-State Circuits,2010,45(5):1007-1015.

[3]He-Gong Wei, U-Fat Chio,Sai-Weng Sin, et al. A 0.024mm2 4.9fJ 10-bit 2MS/s SAR ADC in 65nm CMOS[C]. IEEE European Solid-State Circuits Conference,2012:377-380.

[4]Guo Wei,Mirabbasi S.A Low-Power 10-bit 50MS/s SAR ADC Using a Parasitic-Compensated Split Capacitor DAC[C].IEEE International Symposium on Circuits and Systems,2012:1275-1278.

[5]W Y Pang,C S Wang,Y K Chang,et al.A 10b 500KS/s low power SAR ADC with splitting capacitor[C],IEEE ASSCC Dig Tech Papers,2009:149-15.

[6]Guan-Ying Huang, Soon-Jyh Chang, Chun-Cheng Liu, et al. 10-bit 30MS/s SAR ADC Using a Switchback Switching Method[J]. IEEE Transactions on VLSI Systems, 2012, 21(3):584-588.

[7]Sang-Hyun Cho, Chang-Kyo Lee, Jong-Kee Kwon, et al. A 550uW 10b 40MS/s SAR ADC with Multistep Addition-Only Digital Error Correction [J]. IEEE Journal of Solid-State Circuits, 2011, 46(8):1-11.

[8]Jen-Huan Tsai,Yen-Ju Chen,Meng-Huang Shen et al.A. 1-V 8b 40MS/s 113uW charge-recycling SAR ADC with a 14uW asynchronous controller[C].IEEE Symposium on VLSI Circuits,2011:264-265.

[9]Jeon, Heung Jun, “Low-power high-speed low-offset fully dynamic CMOS latched comparator”, Master’s Thesis, Northeastern University,2010.

作者简介:

李晓兴(1993-),女,江苏扬州人,硕士,东南大学。

杨丽娟(1992-),女,江苏南通人,硕士,东南大学。

杨靖文(1992-),男,河南平顶山人,硕士,东南大学。