12位高精度低功耗SAR ADC设计

2016-03-10东南大学信息科学与工程学院李晓兴杨丽娟杨靖文

东南大学信息科学与工程学院 李晓兴 杨丽娟 杨靖文

12位高精度低功耗SAR ADC设计

东南大学信息科学与工程学院 李晓兴 杨丽娟 杨靖文

本文基于华润上华0.18um CMOS工艺,设计了一款200kS/s、12bit高精度低功耗逐次逼近型模数转换器(Successive Approximation Register ADC,SAR ADC)。本文采用线性度高的栅压自举开关提高精度;采用改进型分段电容结构,并提出非单调开关切换方案,减小了面积和功耗;采用动态比较器减小功耗;采用改进异步时序,减小关键路径延时。前仿结果表明:在200kS/s采样速率下有效位数为11.1bit,信号噪声失真比为68.5dB,平均电流11.7uA。

逐次逼近型模数转换器;改进分段电容结构;非单调开关切换;改进异步时序

0 引言

逐次逼近型模数转换器(SAR ADC)以其低功耗、小面积、结构简单等优点被广泛应用于现代超大规模集成电路与片上系统中,此外,SAR ADC功耗随采样速率而改变,这对于低功耗应用或者不需要连续采集数据的应用非常有利[1],因而,开展高精度低功耗SAR ADC的研究与设计,对低功耗的系统设计和应用具有重要意义。

近年来许多工作致力于降低SAR ADC的动态功耗,在传统二进制电容阵列DAC的基础上进行改造,提出了许多新颖的DAC结构和开关切换方式[2],大大降低了ADC的整体功耗。近年来提出的降低DAC开关能量的方案有步进式电荷重分配结构[3]、分段电容结构[4]、能量节省型开关切换方式[5]、单向开关切换方式[6]、基于共模电压的电荷重分配结构[7]以及无源电荷分享结构[8]等等。

本文的主要目标是设计一款高精度低功耗ADC,文章从功耗和面积的角度出发,通过对传统SAR ADC的结构进行改进和完善,提出更加适合低功耗应用领域的新型结构和开关切换方案,同时采用异步时序控制技术代替传统的同步时序控制,减小关键路径延时,进一步降低功耗。

1 电路设计

1.1 ADC架构

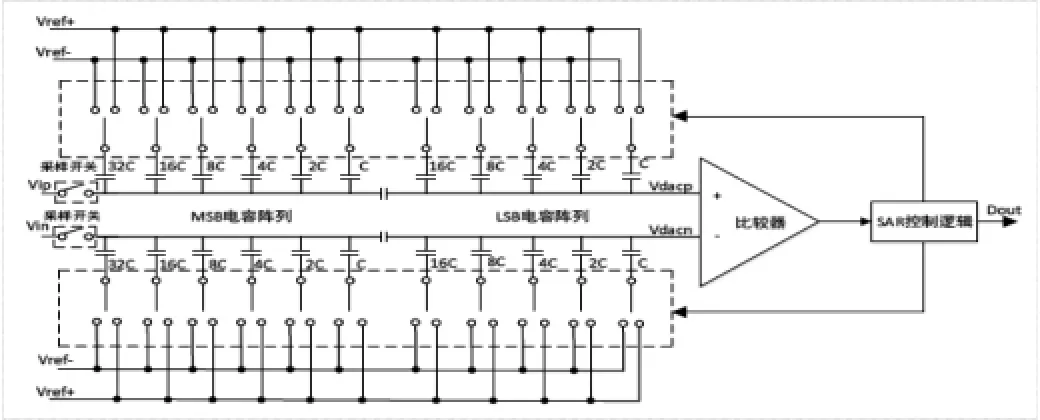

本文采用的ADC架构如图1.1.1所示,主要包括数模转换器(Digital to Analog Converter, DAC)、栅压自举开关、比较器以及SAR 控制逻辑单元。

图1.1.1 12位SAR ADC整体电路框图

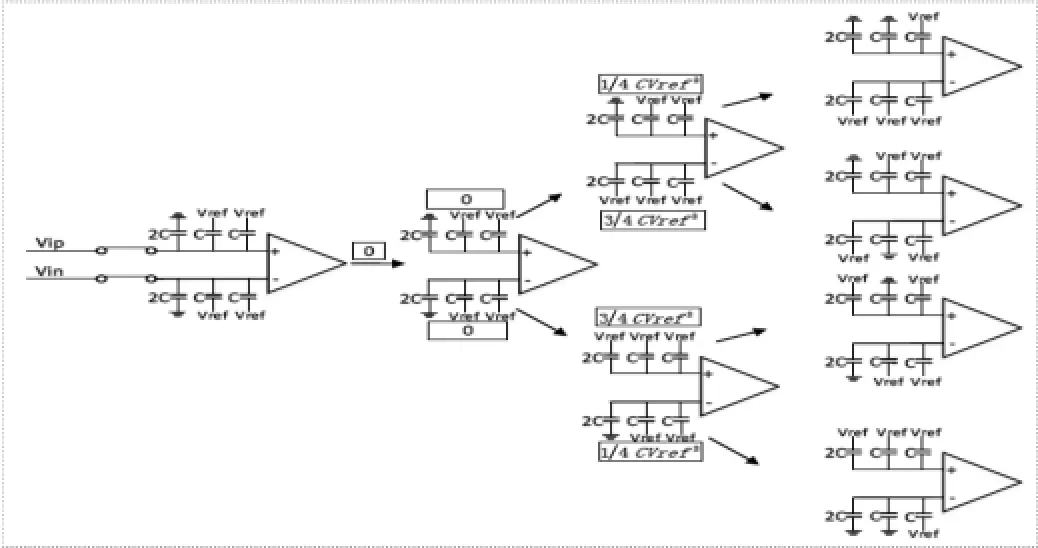

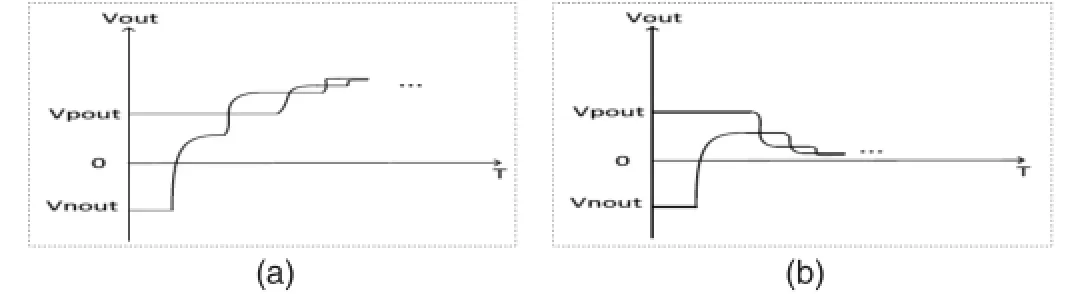

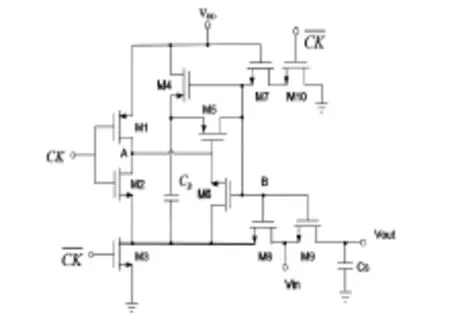

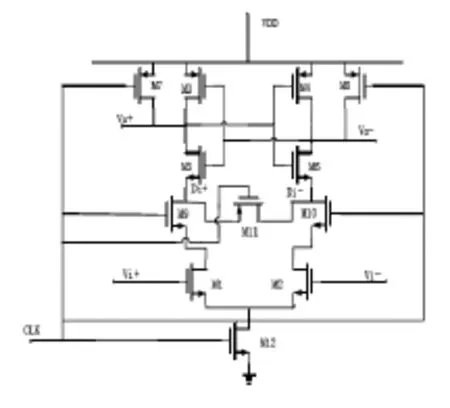

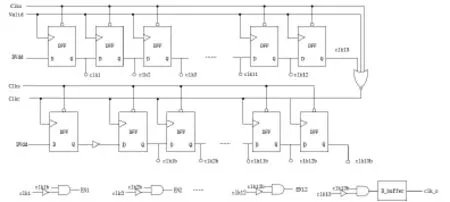

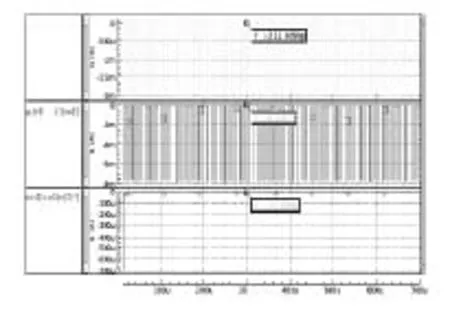

整个电路工作过程如下:(1)当两个采样开关导通,电容阵列最高位电容下极板连接低电平Vref-,本设计中Vref-取1.15V,其它位电容下极板均连接高电平Vref+,本设计中Vref+取2.15V,电路进入采样阶段。这种开关时序可以减小功耗,,具体原因将在下一小节中提及。(2)采样结束后,采样开关断开,DAC输出至比较器的信号为采样的差分信号,即Vdacp=Vip和Vdacn=Vin。比较器随即开始对Vdacp和Vdacn进行第一次比较,得到最高位MSB的结果。(3)SAR控制逻辑根据MSB的结果,改变电容阵列开关切换,使得DAC进行电荷重分配。当Vdacp>Vdacn时,N端最高位电容开关由Vref-切换到Vref+,待充放电结束后,Vdacn增大。反之,Vdacp 至此,系统完成了一次完整的模数转换。 图1.2.1 采用非单调时序3位SAR ADC的开关功耗示意图 1.2 DAC 1.2.1 DAC结构设计 DAC模块电路在SAR ADC中是一个很重要的部分,本设计采用改进型分段电容式结构,电路不需要设计独立的采样保持电路,与传统分段电容式结构相比,有以下几点改进:(1)采用了全差分结构;(2)减少了一位电容,采用“先比较,再变化”的结构,有效控制了面积的增大,同时减小了整个电容阵列的功耗。 1.2.2 开关切换方案 电容阵列的功耗是决定SAR ADC整体功耗的最主要因素,为了显著减小电容阵列的功耗,本设计提出了一种非单调的开关切换方案:采样阶段,最高位电容的下极板接负基准电压Vref-,其它位电容下极板接正基准电压Vref+,同时上极板对输入信号进行采样,采样结束后,采样开关断开。这种开关时序相比于传统单调电容开关时序主要有两点优势:减小功耗和共模电平变化,下面将对这两点优势作详细说明。 (1)减小功耗 以3位SAR ADC为例,图1.2.1给出了使用本文提出的非单调时序的开关功耗示意图。 采样结束后,采样开关断开,比较器直接进行第一次比较,这一步不消耗开关能量。如果Vip大于Vin,则MSB=1,同时与比较器负输入端相连电容阵列的最大的电容接Vref;否则MSB=0,同时与比较器正输入端相连电容阵列的最大电容接Vref,其余电容接法保持不变,这一步消耗的能量为: 与传统的单调电容开关时序不同,这一步仍然不消耗开关能量,此时最高位需要的开关能量由后面的低位电容提供,其余各位消耗的量相同。由于功耗与电容成正比,所以最高位开关切换时消耗的能量最大,因此本文采用的非单调开关时序大大降低了功耗。 (2)减小共模电平变化 图1.2.2是转换过程中DAC差分输出的变化图,其中:(a)是单调开关切换;(b)是本设计采用的非单调开关切换,可以看出单调开关切换DAC的输出始终是单调增加的,每次只有一个输出端变化,共模电平变化范围大。而本设计采用的非单调开关切换方法,只有第一个比较周期结束后,DAC一端的输出增加,另一端不变,其余周期均是一端减小,另一端不变,这样共模电平的变化范围小,并且确保DAC的输出在比较器的输入范围内。 图1.2.2 两种开关切换方法的DAC差分输出变化图 1.3 栅压自举开关 图1.3.1 栅压自举开关原理图 如图1.3.1所示,本文采用了一种栅压自举开关电路。与传统的CMOS开关相比,栅压自举开关在输入信号电压变化时,电路可保证开关MOS管栅源电压不变。从而保证等效导通电阻不变。提高整个电路的线性度。 1.4 比较器 传统的动态比较器如图1.4.1所示,图中M1、M2是差分输入管,M3~M6构成交叉耦合对,加速比较,比较器的工作状态通过时钟信号CLK控制,当CLK为低电平时,比较器进入复位状态输出端被复位到高电平。CLK为高电平时,比较器开始比较。 图1.4.1 传统的动态比较器原理图 图1.4.2 改进型的动态比较器原理图 本文采用的动态比较器在传统动态比较器的基础上进行修改,改进后的动态比较器电路原理图如图1.4.2所示,改进型的结构相较于传统结构使用了更多的NMOS开关,减少了PMOS开关,使用M11替代了图1.4.1中的PMOS复位开关M9,M10。 在比较器的噪声方面,改进型的动态比较器可以显著地减小踢回噪声对比较器的影响,在比较器中,输入差分对漏端电压的变化将会产生很大的,并且还可能会使差分对的工作区域发生变化从而使其栅端电压发生变化产生踢回噪声。在本文所使用的结构中,M9,M10显著减小了首尾相连的反相器对输入差分对产生的踢回噪声。 在功耗方面,改进型的动态比较器结构相较于传统结构,不仅节省了复位期间的比较器功耗,并且从理论分析[9]可知,比较器的比较时间提高了大约45%,由于本文的ADC使用的是异步时序结构,所以快速的比较周期有利于在相同的采样周期下可以减少工作时间,从而进一步地降低功耗。 1.5 数字逻辑电路 SAR ADC控制电路从总体上来说包括同步和异步两种。同步控制电路需要一个频率大约为(N+1)*fs的内部时钟,并且转换时每步转换消耗的时间是一样的。异步控制电路系统时钟频率和系统转换速率相等,采样完后SAR ADC自动产生转换所需的时钟。为减小功耗,本设计采用了异步控制方法。同时相比于传统的异步逻辑电路,本设计减少了关键路径上的中间控制信号,以此来减小关键路径延时,使电路工作速度更快。 图1.5.1给出了从比较器到DAC直接控制的信号转移路径,通过这种方式可以有效地减小控制信号对整个比较周期的影响,从而缩短比较时间。只要给出锁存器的En信号和Rst信号就可以使整个电路工作起来。 Rst信号可直接接采样信号,使其在采样阶段复位。En信号则必须由控制逻辑来实现。 图1.5.2给出了本次设计所采用的异步逻辑的电路框图。比较器时钟信号clkc由采样时钟信号Clks,比较器输出有效信号Valid以及12次比较完成信号Clk13共同决定,而EN信号由每次比较开始和结束的信号共同决定。 图1.5.1 从比较器到DAC直接控制的信号转移路径 图1.5.2 异步逻辑时序控制电路示意图 完成各个模块的设计后,按照图1.1.1系统框图所示,组合完成SAR ADC电路,对该电路进行系统仿真,采样点数128个点,最终的电路前仿真结果如图2.1所示。ADC功耗及平均电流如图2.2所示。总电路版图如图2.3所示。 图2.1 ADC输出matlab仿真结果 图2.2 ADC功耗及平均电流 仿真结果表明,采样频率为200kS/s时,有效位数ENOB为11.1bit,信号噪声失真比SNDR为68.5dB,无杂散动态范围SFDR为78.5dB,平均电流11.7uA。 Design of 12-bit High Precision Low Power SAR ADC Li Xiaoxing,Yang Lijuan,Yang Jingwen A 200kS/s, 12bit high precision low power SAR ADC is designed in this paper using CSMC 0.18um process. Bootstrapped switch with high linearity is adopted to improve the accuracy; Improved segmented capacitive structures and non-monotonic switching scheme are proposed in order to reduce the area and power consumption; Dynamic comparator is used to lower the static power consumption; Improved asynchronous timing can reduce the delay of the critical path. The simulation results show that: when sampling speed is 200kS/s, the effective number of bits is 11.1bit, signal to noise and distortion is 68.5dB and the average current is 11.7uA. SAR ADC; Improved segmented capacitive structures; Non-monotonic switching scheme; Improved asynchronous timing

2 仿真结果

(School of Information Science and Engineering, Southeast University, Nanjing 211189, China)