片上FLASH存储器接口的设计

2016-03-09解放军92785部队刘宗福

解放军92785部队 刘宗福

片上FLASH存储器接口的设计

解放军92785部队 刘宗福

【摘要】DSP片内有限的存储容量限制了其信息处理能力,针对这一特点,本文设计了外部存储器接口,使DSP具有了和FLASH等异步存储器的无缝接口,用户可以方便的外接存储器芯片来扩展存储空间。文章中给出了设计思路与实现,并进行了RTL级验证,设计的外部存储器接口在功能和时序上符合各种存储器技术规范,达到了预定目标。

【关键词】数字信号处理器;FLASH存储器;外部存储器接口;有限状态机

0 引言

基于DSP的末制导雷达信息处理对存储空间的要求较高,以满足雷达数据实时回传与存储的要求。尤其在做导引头飞行试验或防空反导训练时,需要外接存储器来扩展DSP的存储空间,用于记录试验训练数据。目前用于DSP的存储器芯片有ROM、Flash、SBSRAM、SDRAM等。然而,该类存储器件的对外接口复杂,无法与DSP芯片进行无缝对接,给基于DSP的雷达信号处理分机设计带来很多不便之处。因而本文设计的DSP中,片上集成了外部存储器接口(EMIF),支持Flash等多种存储器,可以使DSP芯片实现和FLASH存储器芯片的无缝连接。

1 功能介绍

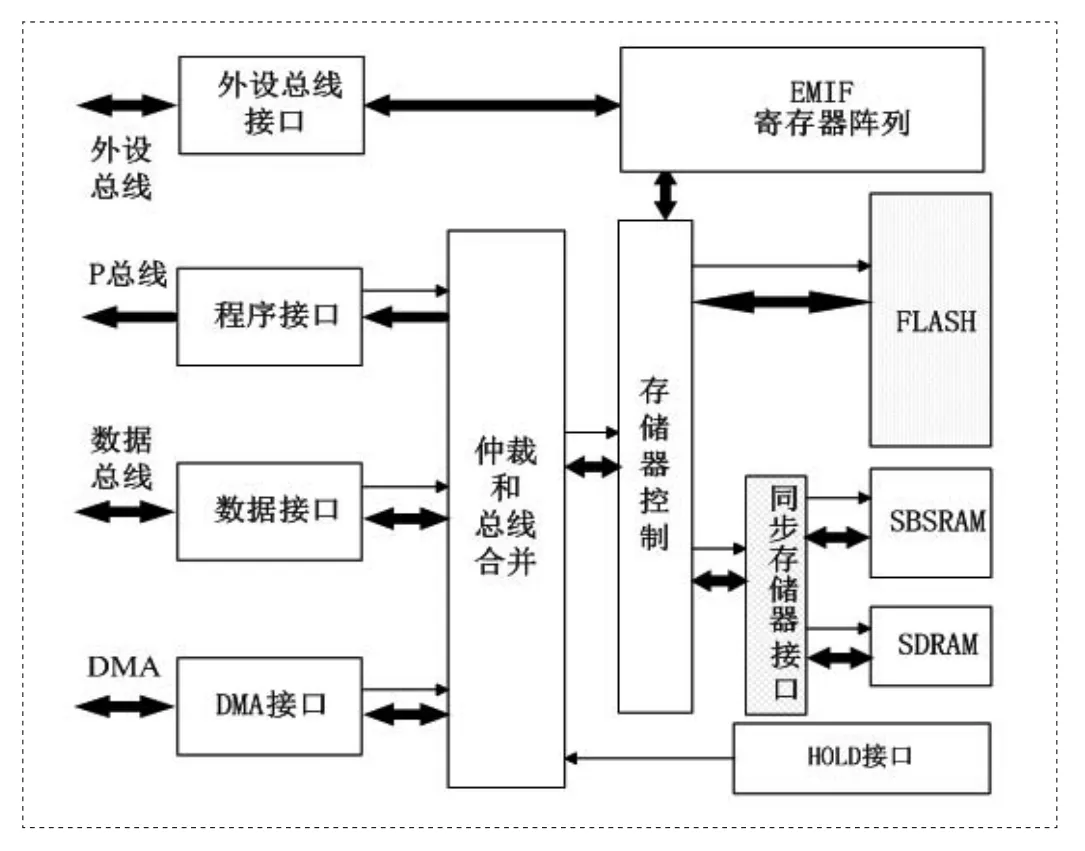

在系统的设计中,在DSP片上集成了外部存储器接口EMIF。图1是EMIF部件的框图。CPU经由程序总线(P总线)读取片外存储器中的程序,经由数据总线读写外存中的数据, DMA总线用来进行片内和片外之间的大量数据传输。所有的读写外存的请求按优先级进行仲裁,每次选择一个送到存储器控制模块,译码后送给相应的控制器:FLASH存储控制器、SBSRAM控制器、SDRAM控制器,本文主要介绍FLASH存储控制器的设计。

图1 EMIF的框图

Flash存储器接口也支持ROM、异步SRAM存储器等,这类存储器读写不需要时钟。设计该类接口主要有两个作用,一是为了加载程序,在DSP加电后,引导加载器可通过FLASH控制器接口将片外程序加载到DSP片上存储器,另外,FLASH存储器可以永久保存末制导雷达的部分数据,供飞行试验或训练结束后进行事后数据分析。

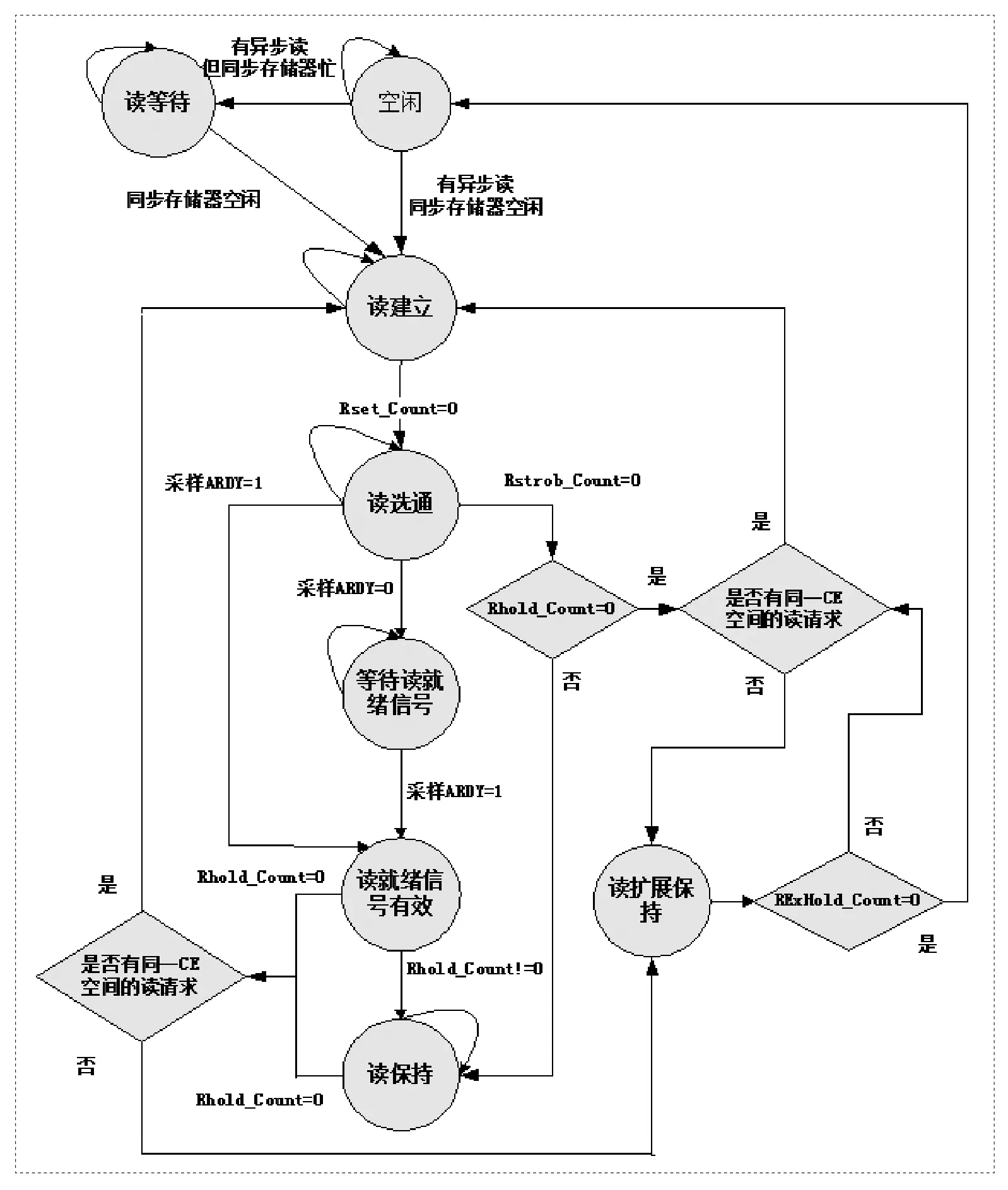

图2 FLASH存储控制器的读状态机

2 FLASH存储器读写操作流程

读时序的过程如下所示(写操作流程类似):

(1)建立时间期间

首先,给出片选信号,选中指定的FLASH存储器开始工作;其次,输出使能信号有效,允许指定的FLASH存储芯片根据要求对外输出数据;第三,给出字节使能信号,标明要访问的字节的数量与位置;建立时间的最后,给出地址信号,发送要访问的地址信号到FLASH存储芯片。

(2)选通时间期间

首先,给出读选通信号,开始进入读选通时间;其次,在CPU的时钟上升沿采样数据,该操作恰好领先于读选通信号的上升;最后,进入读选通信号上升沿,读选通时间终止。

(3)保持时间的停止

字节使能线变为无效;地址线变为无效;输出使能信号上升,释放芯片的输出使能信号。

(4)扩展保持时间期间

在保持时间结束后,需要插入扩展保持周期,使FLASH存储控制器发出的输出使能信号和片选信号无效。加入扩展保持时间,主要是考虑到在下一次访问外部存储空间时,FLASH存储控制器可能会在不同的片选(CE)空间之间进行切换,或者改变数据的传输方向。

3 FLASH读写控制器设计

3.1 FLASH读写控制器的构成

FLASH存储控制器由计数器、有限状态机FSM与数据通路三个功能模块构成。其中,整体的结构设计思想为FSM-D组合,以有限状态机模块为核心。FSM模块控制状态机的翻转,同时输出FLASH存储控制器的状态信号,控制进行指令译码与数据装配。计数器模块保存FLASH存储器的读写时序参数,根据FSM模块的命令开始减1计数过程,计数结束后向FSM发出定时中断,数据通路模块根据FSM的当前状态,定时输出数据信号、地址,同时负责读写数据内容的装配。

3.2 计数器模块

该模块实现若干个计数器,记录FLASH存储器所有的读写时序参数,与读操作有关的计数器变量如表1所示。FSM模块给出读写控制信号,在进入对应状态的同时,启动计数器从规定的初始数值开始递减,当计数结束后,告知状态机进行翻转。

表1 FLASH存储控制器中的读时序计数器

3.3 FSM模块

FSM模块接收来自EMIF控制模块的指令,若其他存储控制器与外部Hold请求(外部设备发出申请EMIF放弃控制存储器的请求)未占用总线,启动计数器模块开始计时,根据计数器模块的定时结果,发出中断信号改变FSM状态。FSM不仅要输出FLASH存储控制器的状态信号,而且要根据FSM的当前所在状态,给出读写操作使能信号以及外部总线的输出使能信号。本文以读操作为例,设计了FSM的流程,如图2所示。

(1)空闲状态,当接收到读FLASH存储器的请求后,在等待其他存储器(SDRAM等)空闲或外设HOLD请求结束后,立即进入读操作建立时间状态。

(2)读操作建立时间状态,开始计数,当该状态结束后进入读选通时间状态。

(3)读选通时间状态,若不采样FLASH存储器的ARDY信号,则当读选通时间状态结束后,对FLASH存储器数据采样,然后跳转到第6步判断读保持时间计数器,若采样ARDY信号则进入下一步完成ARDY信号采样。

(4)在读操作选通时间结束前的第3个CPU时钟上升沿采样ARDY,若信号电平为低,进入读选通操作的扩展等待时间,等到ARDY为高时进入下一步(读数据采样);若在读操作选通时间结束前的第3个CPU时钟上升沿采样ARDY为高,直接进入下一步(读数据采样)。

(5)计数3个CPU时钟周期,在读操作选通时间的末尾(最后一个CPU时钟上升沿)对数据采样,进入下一步(读保持状态)。

(6)若读保持时间计数器Rhold_Count为零,如有同一CE空间的读请求,进入第1步(重新开始读操作),若没有进入第8步(读扩展保持时间);如果Rhold_Count不为零,进入下一步(读保持时间状态)。

(7)读保持时间状态,Rhold_Count计数结束后,若有同一CE空间的读请求,进入第1步(重新开始读操作),若无进入下一步(读扩展保持时间)。

(8)读扩展保持时间状态,若有同一CE空间的读请求到来,进入读建立时间状态,若无同一CE空间的读请求,继续进行扩展保持状态递减计时,若扩展保持时间计数器结束,进入IDLE(空闲)状态。

写操作的流程和读操作时类似的,将读写操作组合,构成FLASH存储控制器的整个状态机。

3.4 数据通路模块

该模块主要根据FLASH存储器的位宽度与读写时序计数器的当前数值,对地址信号、字节使能信好和写数据进行译码。在DSP读FLASH存储器的数据时,要根据存储器的位宽度和读写时序计数器的数值,将要读的数据组装后发送给DSP。

4 FLASH存储控制器的功能测试

本文采用Modelsim仿真工具(主要用于模块级与部件级模拟)与Ncverilog(后期用于系统级模拟)仿真工具,外接FLASH存储器的软核,对FLASH存储控制器进行功能验证,以DMA总线访存来测试,依次测试了8b、16b、32b的异步存储器,给出的示例为不采样ARDY,写32b的数据F00FFF0F的情况,如图3所示,其中EA为地址信号,BE为字节使能信号,CE位片选信号,AOE为FLASH存储器的输出使能信号,AWE为写选通信号,ED_OUT为FLASH存储控制器对外输出的数据。

图3 DMA向8位的FLASH存储器写32位的数据

5 结束语

本文设计的FLASH存储器接口,在一定程度上解决了DSP片内存储空间的不足,用户可以借助于FLASH存储器接口,构建高速度、大容量的片外存储空间。在具体的结构设计方面,FLASH存储器接口挂在总线上,尽量满足IP核的可重用设计,即不需要对结构做大的改动,就可以重构一个满足不同需求的片上外部存储器接口,只需要替换总线接口模块为其他类型的片上总线即可。

参考文献

[1]彭启琮等.TMS320VC55x系列DSP的CPU与外设[M].北京:清华大学出版社,2005.

[2]夏宇闻.Verilog 数字系统设计教程[M].北京:北京航空航天大学出版社,2008.

[3]刘宗福.FT-C55 LP外部存储器接口的设计与实现[D].国防科技大学硕士论文,2009.

[4]顾菘,等.TMS320C67系列EMIF与异步FIFO存储器的接口设计[J].电子工程师,2005,31(5):53-55.

[5]周顺燕,吴丹.TMS320C6713 DSP的高速EMIF数据接口设计与实现[J].计算机测量与控制,2010,18(7):1654-1656.

刘宗福(1984—),山东高密人,硕士研究生,工程师,主要从事雷达信号处理工作。

作者简介: