基于51核的AES算法高速硬件设计与实现

2016-02-29曾小波易志中

曾小波,易志中,焦 歆

(1.湖南理工职业技术学院 太阳能工程系,湖南 湘潭 411104;2.上海滕维信息科技有限公司,上海 200072)

基于51核的AES算法高速硬件设计与实现

曾小波1,易志中2,焦歆2

(1.湖南理工职业技术学院 太阳能工程系,湖南 湘潭411104;2.上海滕维信息科技有限公司,上海200072)

摘要为提高算法的效率,降低密钥运算的复杂度,提升密钥抵抗强力攻击和时间攻击能力,提出一种AES的算法方案。阐述了AES算法原理及片上系统执行AES的工作流程,基于8051软核AES算法IP原理、设计流程以及硬件模块的实现方案,并给出了效率分析及在硬件平台上的验证结果。仿真结果显示,用查表法实现AES,其IP核具有高效性,并可为密码SoC产品的开发体统算法引擎支持。相比较于以往的算法模型,该方案用少量面积换取速度,大幅提高了算法的效率,因此具备良好的应用价值。

关键词对称加密;AES算法;IP核;片上系统;解密

High-Speed Hardware Design and Implementation of AES Algorithm Based on 51 Core

ZENG Xiaobo1,YI Zhizhong2,JIAO Xin2

(1.Department of Solar Engineering,Hunan Vocational College of Science and Technology,Xiangtan 411104,China;

2.Shanghai Tengwei Information Technology Co.,Ltd.,Shanghai 200072,China)

AbstractAn AES algorithm scheme is proposed for higher algorithm efficiency,lower complexity of key operations and better resistance of the key against brute-force attack and time attack.The AES principles and its on-chip implementation based on 8051 soft-core are presented with workflow system and hardware modules design given.The efficiency analysis and verification results on the hardware platform are provided.Simulation results show that the AES IP core by look-up table method has high efficiency,and offers support for algorithm engine in the SoC decency password product development.A substantial increase in the efficiency of the algorithm is achieved at the mere cost of a small area of the exchange rate compared with conventional algorithms.

Keywordssymmetric encryption;AES algorithm;IP core;system on chip;decryption

AES(Advanced Encryption Standard)是由美国联邦政府采用的一种区块对称加密标准,以此来取代之前的DES,截止至2006年,高级加密标准已成成为最流行的对称算法[1]。其在软硬件实现过程中均表现出良好的性能:建立密钥时间短、灵敏性高、能够抵抗强力攻击和时间攻击[2]。本文利用Ncverilog研究查表法AES算法[3]高速硬件的实现,并采用8051软核为控制器,将AES作为可移植的IP进行了顶层调试,并给出其相应Verilog模型的仿真结果。本文中所采用的Verilog行为模型为RTL级(Register Transfer Level),是用寄存器这一级别的描述方式来描述电路的数据流方式,即可综合的。模型接口为标准的Wishbone总线及51接口。相比较于以往的算法模型,该方案用少量面积换取速度,大幅提升了算法的效率。

1算法描述

1.1 算法综述

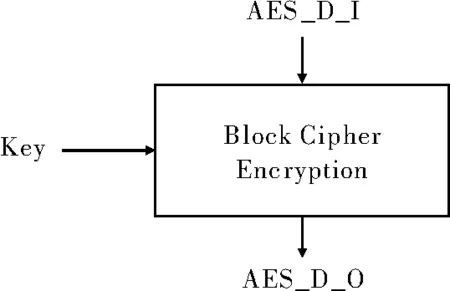

从算法应用的流程上来可将其分为两大步骤:(1)密钥扩展;(2)加密或解密的实现。AES IP的端口简略描述如图1所示。AES_D_I为AES算法数据输入端口,为明文或者密文。KEY为密钥输入端口长度可为128,192或256 bit。AES_D_O为数据输出端口,即完成加密的数据或解密完成的数据。本文选用128 bit作为密钥长度。

图1 AES IP端口简略图

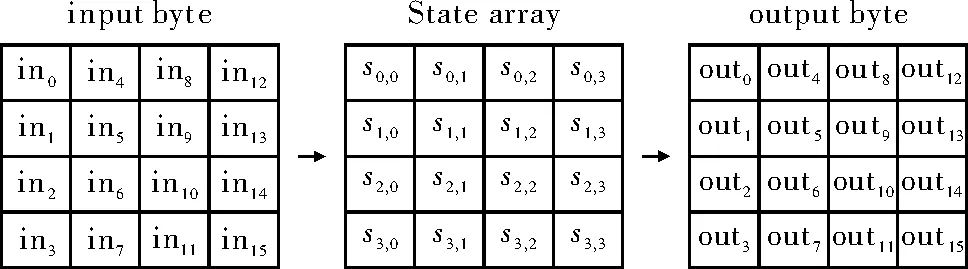

以128 bit数据按字节(Byte)输入为例,输入为in0,in1,…,in15,复制到图2所示状态矩阵中。加密或解密的运算均在该状态举证上进行,最终结果将被复制到输出字节数组out0,out1,…,out15。

图2 状态矩阵、输入和输出

对于AES算法,数据输入分组、数据输出分组、状态长度均为128 bit。Nb=4,该值反应了状态中32 bit的个数。在加密和解密的初始阶段,输入数组in按照下述规则复制到状态举证中

S[r,c]=in[r+4c] for 0≤r<4 and 0≤c<4

(1)

在加密和解密的结束阶段,状态举证将按照下述规则被复制到输出数组out中

out[r+4c]=S[r,c] for 0≤r<4 and 0≤c<4

(2)

状态矩阵中每一列的4Byte可看作一个32bit字,行号r可作为每一个字中4Byte的索引。因此,状态可看作32bit字(列),w0,…,w3的一维数组,列号c是该数组的索引。因此对于图2的例子,该状态可看作4个字组成的数组,为:W0=s0,0s1,0s2,0s3,0,W1=s0,1s1,1s2,1s3,1,W2=s0,2s1,2s2,2s3,2,W3=s0,3s1,3s2,3s3,3。

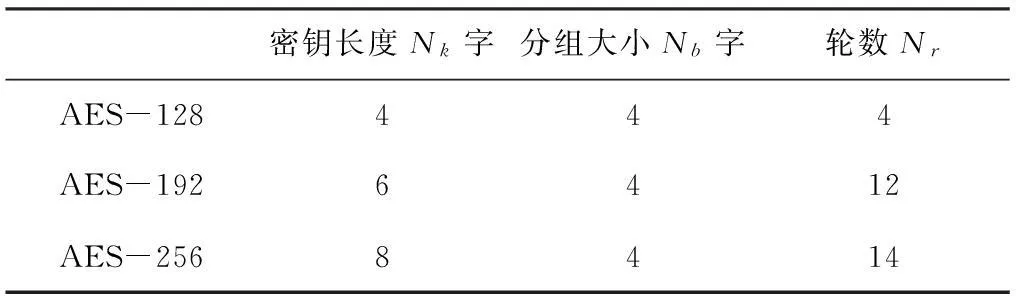

对于密钥K的长度可为128、192或256bit,也按密钥长度表示为Nk=4、6或8。AES加密的轮依赖于密钥的长度。将轮数表示为Nr,当Nk=4时Nr=10;当Nk=6时Nr=12;当Nk=8时Nr=14。该标准符合一切密钥长度-分组长度-轮数组合,如表1所示。

表1 密钥长度-分组长度-轮数组合

1.2 加密

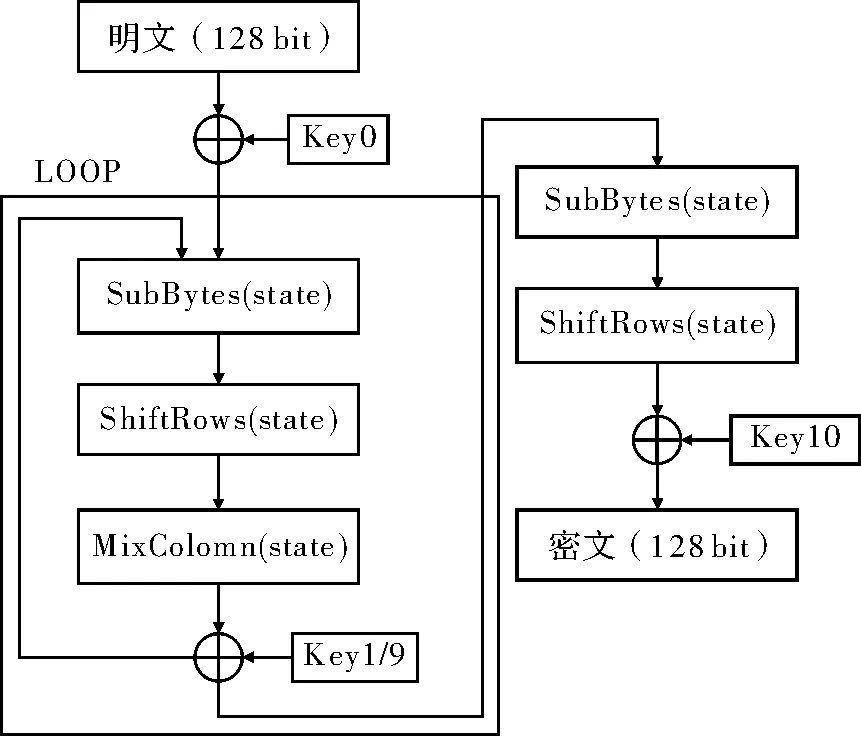

以128 bit密钥加密为例的流程图,如图3所示。首先将明文按式(1)所描述的管理将输入复制到状态矩阵中,与初始子密钥K0相加。然后经过Nr-1次轮函数来变换状态矩阵,最后一轮与前Nr-1轮略有不同。最后状态按式(2)所描述复制到输出。

图3 加密流程图(128 bit)

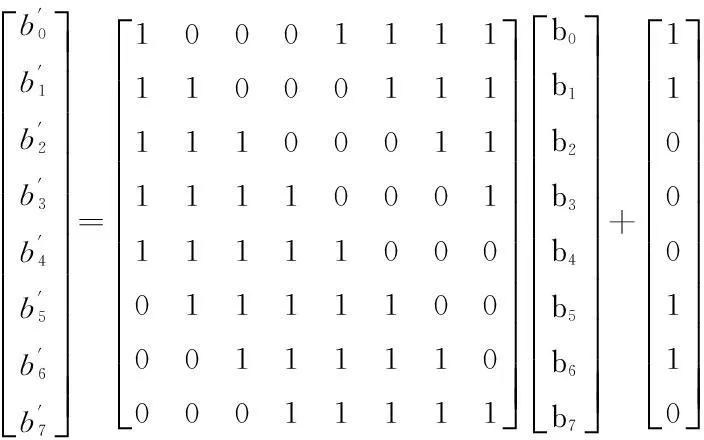

1.2.1Sub Bytes()

字节替代(Sub Bytes())是一个非线性的字节替代,将状态阵列中的字节看做GF(28)域上的元素,映射到自身的乘法逆,然后再通过图4所示的仿射变换。

图4SubBytes()变换在状态上的作用效果

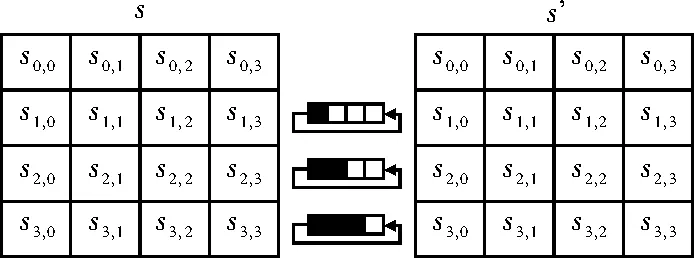

1.2.2ShiftRows()

在行移位(ShiftRows())变换中,状态的最后3行循环移位不同的位移r。具体方法按照式(3)进行

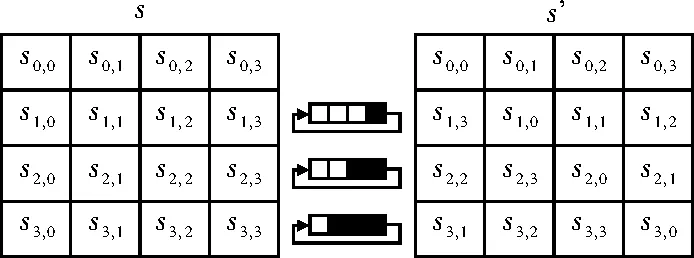

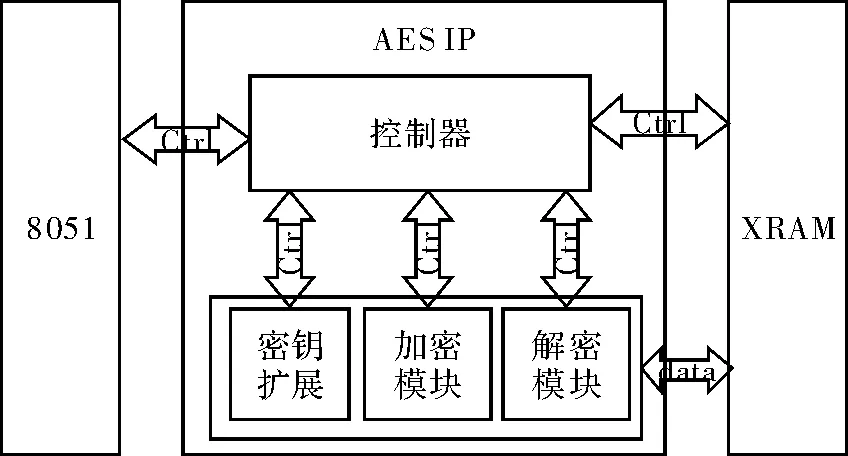

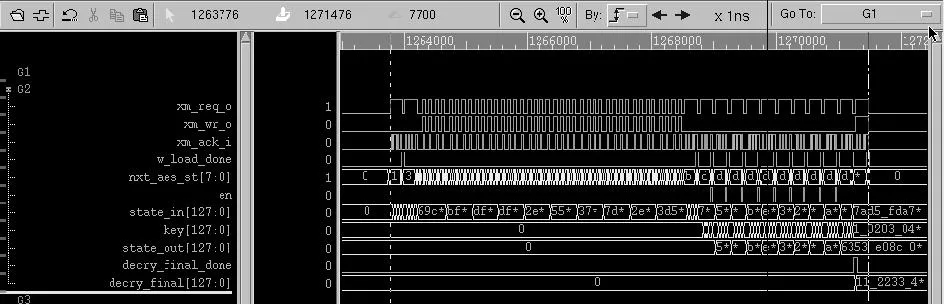

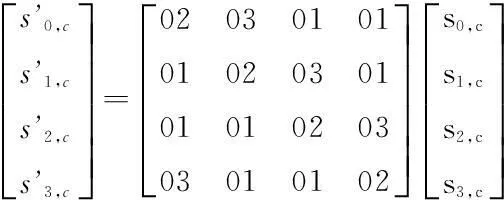

s’r,c=sr,(c+shift(r,Nb))mod Nbfor0 (3) 移位量shift(r,Nb)依赖于行号r,如下所示(Nb=4) shift(1,4)=1;shift(2,4)=2;shift(3,4)=3 (4) 作用效果如图5所示。 图5 ShiftRow()作用效果 1.2.3列混合(MixColumn()) MixColumn变换中,把状态的列看做GF(28)上的多项式,并与固定的多项式c(x)相乘后模X4+1,如图6所示,其中c(x)={03}x3+{01}x2+{01}x+{02},写成矩阵乘法,令s’(x)=a(x)×s(x)。 图6MixColumn变换 AES的密钥扩展[4]工作是将初始密钥扩展为Nb(Nr+1)个字,现以128bitAES为例,需要将原始4个字(128bit)的密钥扩展为44个字的新序列,每个字32bit3,记为w[0],w[1],w[2],…,w[43]。首先按式(1)将密钥输入到矩阵中,每一列的4个字节组成一个字。接着对初始4个列为w[0],w[1],w[2],w[3],进行扩充,构成40个新列。新列是以递归的方式产生的,具体原则是:如果i不是4的倍数,使用w[i]=w[i-4]⊕w[i-1]方程式,如果i是4的倍数,使用w[i]=w[i-4]⊕T(w[i-1])方程式[3]。T是一个复杂的函数,由3个部分组成:字循环,字节代换和轮常量异或。字循环是将1个字中的4个字节循环左移1个字节。字节代换将4Byte的数据分别使用SubByte()函数进行字节代换。轮常量异或是将前两步的结果同轮常量Rcon[j]进行异或,其中j表示轮数。经过以上步骤的运算,最终产生44个字组成的密钥,其中w[0],w[1],w[2],w[3]是原始密钥,用于在第一轮加密操作之前对明文进行加密,后40个字组成10组密钥,在每轮加密过程中作为轮密钥使用。 AES算法解密过程,即1.2加密变换逆转,然后以逆序执行即可直接得到解密算法。解密算法中使用的变换主要包括InvShiftRows(),InvSubBytes()和InvMixColumns()这3种变换。且各个变换的使用顺序也不同,首先对密文使用K10({w[40],w[41],w[42],w[43]})进行轮密钥加,然后进行第一轮的解密,分别为InvShiftRows(),InvSubBytes(),轮密钥加和InvMixColumns(),直到倒数第二轮解密,最后一轮操作只有3部InvShiftRows(),InvSubBytes()和使用K0(w[0],w[1],w[2],w[3])进行轮密钥加。以128bit为例的流程图如图7所示[5]。 图7 解密流程图(128 bit) 逆行运算(InvShiftRows())是行移位(ShiftRows())变换的逆变换。第一行中r=0,即不移位。下面的3行将循环移动Nb-shift(r,Nb) Byte,其中位移量shift(r,Nb)参照式(4)。作用效果图如图8所示。 图8 InvShiftRow()作用效果 InvMixColumn()变换是MixColumn()的逆变换。将状态的列看做GF(28)上的多项式且被一个固定的多项式a-1(x)模x4+1乘,a-1(x)={0b}x3+{0d}x2+{09}x+{0e}。写成矩阵乘法,即s’(x)=a-1(x)×s(x)。 2系统框架结构设计 由于AES IP由8051软核控制,及考虑到消息尺寸及填充后的密钥的尺寸较大,故在IP核上添加DMA bus,方便读写XRAM数据及节省硬件资源。IP的控制信号及信息地址数据由51软核控制[6,9-10]。整个系统框架如图9所示。 图9 AES框架图 如图9所示,IP核内由控制器来密钥扩展模块、加密模块还有解密模块。当这3个模块使能时可通过DMA总线从XRAM中抓取相对应的数据,进行扩展、加密或解密工作,完成后再通过DMA总线将数据写到XRAM中。 3IP的实现 首先,通过以上讨论可发现Sub Byte()和InvSubByte()函数就是一个8 bit输入/输出的S盒,由于这个S盒与密钥无关,在硬件实现时,为了提高速度。可计算出8 bit输入所包含256种组合的结果,将其制成表格,进行替换操作时通过查表实现。另外在一次密钥变换中,有32位数据要进行替换,故需要使用4次S盒。加密或解密算法若一次处理128 bit数据,就需要使用16次S盒。虽然S盒可重复使用,但其吞吐量太小。考虑到AES通常均是对大数据进行加密,本文在设计时以速度优先的为前提,同时使用16个Sbox,虽然占用相对较多的硬件资源但速度提升了16倍[6,9-10]。 通过以上对Mix Column和InvMixColumn的描述可发现一个特点,就是相乘的两个操作数中,有一个是常数。例如图6中的{02},{03},{01},{01}。此外,再通过GF(28)域中乘法规则和域中乘x规则可知,{03}x={02}x+x。因此可以再计算出x×Sbox的表。以解密为例,由以上两种表格,完全可以在一个时间内求得Sbox和x×Sbox的值。此外,ShiftRow(),InvShiftRows()和加法器也都由组合逻辑实现。因此,一个时钟便可完成一轮密钥的加密和解密运算。 4基于NC-Verilog的仿真 该IP算法用RTL实现后,在Red-Hat Linux仿真环境下进行了仿真,工具为NC-Verilog,测试向量从参考文献[3]的附录c选取。图10为AES-128 加密仿真结果。系统仿真时钟为40 MHz。从仿真结果显示,从8051使能IP到IP完成解密并将结果写入到XRAM一共用时7.7 ms。 图10 AES-128 解密仿真结果 5结束语 对称密码算法主要用于保证数据的机密性。通信双方在加密/解密过程中使用其共享的单一密钥。本文阐述并验证了AES算法通过查表法实现的可行性,定义了CPU接口和XRAM数据接口,使IP核在商用密码片上系统中占用资源更少,提高工作效率及其可移植性。密钥扩展及加密过程,每一轮扩展生成的密钥以及加密所需的密钥轮次相同,可在加密过程采取流水线(Pipeline)结构,在生成密钥的同时进行加密,省去将密钥写入XRAM过程,提高算法实现速度。 参考文献 [1]弟宇鸣,陈荣桦,左广霞.基于AES算法的加密模块设计[J].电子设计工程,2013,21(2):53-55. [2]王威,刘百华,孟凡清.计算机网络安全问题与防范方式[J].电子科技,2012,25(4):122-123,126. [3]曹晓丽,王爱强.AES算法研究[J].洛阳师范学院学报,2011,30(8):74-76. [4]王小伟.AES加密算法的研究与IP核设计实现[D].哈尔滨:哈尔滨工业大学,2012. [5]Joan Daemen,Vincent Rijmen.高级加密标准(AES)算法-Rijndael的设计[M].谷大武,徐胜波,译.北京:清华大学出版社,2003. [6]曾毅,鲁欣,付宇卓.一种优化可配置的AES密码算法硬件实现[J].微电子学与计算机,2004,21(12):34-37. [7]赵哲斐.AES算法IP核优化与设计[D].西安:西安电子科技大学,2013. [8]谢孝青,高琳.基于结构共享和多级流水线的AES算法硬件实现[J].电子科技,2009,22(3):48-51. [9]李浪.Verilog HDL语言的AES密码算法FPGA优化实现[J].重庆大学学报,2014,37(6):57-63. [10]叶剑,李立新.基于GPU的AES快速实现[J].计算机工程与设计,2010,31(2):256-259. 作者简介:曾小波(1979—),男,讲师。研究方向:嵌入式技术等。易志中(1980—),男,硕士,高级工程师。研究方向:视频编解码及图像处理。 基金项目:湖南省教育厅科研基金资助项目(13C380) 收稿日期:2015- 03- 31 中图分类号TN918.4;TP309.7 文献标识码A 文章编号1007-7820(2016)01-036-04 doi:10.16180/j.cnki.issn1007-7820.2016.01.010

1.3 密钥扩展

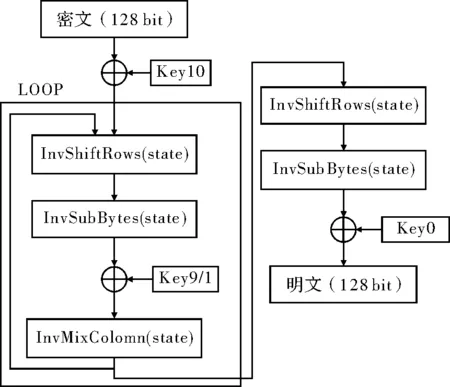

1.4 解密