基于TMS320C667x和VPX的雷达处理系统设计及应用

2016-02-07宋玉霞邵江雨

宋玉霞,李 贵,甘 峰,邵江雨

(中国西南电子技术研究所,四川 成都 610036)

基于TMS320C667x和VPX的雷达处理系统设计及应用

宋玉霞,李 贵,甘 峰,邵江雨

(中国西南电子技术研究所,四川 成都 610036)

针对基于CPCI或VME构建的雷达信号处理系统数传和处理能力的瓶颈,提出了一种以TI公司多核DSP TMS320C667x为核心处理器、基于VPX架构的高端高速雷达实时信号处理系统,介绍了系统的软硬件架构设计、电气结构设计、背板拓扑结构设计以及在雷达SAR成像处理模式、单脉冲处理模式的应用软件设计。工程应用中的测试结果表明,该系统具有比传统信号处理系统更高的处理性能和与高性能相匹配的高速数传网络,应用前景广阔。

处理系统;TMS320C667x;VPX;SAR成像处理;单脉冲处理

0 引言

过去10多年,雷达信号处理系统常采用TigerSHARC系列DSP或PowerPC系列CPU基于CPCI或VME总线进行构建。然而,在机载、弹载雷达SAR成像和单脉冲波束锐化等应用场合,采用TigerSHARC和PowerPC构建的处理平台因体积庞大、功耗高、控制复杂,给雷达系统的应用带来了很多局限性;面对现代武器装备系统海量数据传输需求,基于并行传输方式的CPCI或VME总线在带宽、功耗限制等方面的瓶颈日益突出[1]。

运用多核DSP技术实现雷达信号处理算法设计逐渐成为新的趋势[2],同时,高性能的处理器需要更高带宽的总线的支持[3]。本文采用TI公司多核DSP TMS320C667x和基于串行总线架构的VPX总线规范设计了一种新型高速实时通用信号处理系统,解决了传统信号处理系统芯片多、体积大和功耗高的问题。同时,VPX总线的采用解决了海量数据传输瓶颈问题,并与核心处理器的高性能相匹配,构成了处理和数传平衡的高性能系统,满足现代新体制雷达的应用需求。

1 处理器和总线架构

1.1 TMS320C667X

TI公司基于最新的KeyStone架构的TMS320C667x系列多核DSP,包括分别含1、2、4、8个C66x CorePacs 的TMS320C6671、TMS320C6672、TMS320C6674、TMS320C6678,其主要特点如下:

① 每个内核可工作在1 GHz、1.25 GHz或1.4 GHz;

② 具有定点/浮点双运算模块,当内核频率为1.25 GHz时,TMS320C6678处理论上可实现320GMACS或16GFLOPS处理能力[4];

③ 各核配置32 KB L1P(一级程序存储器)、32 KB L2D (一级数据存储器)和512 KB L2 (二级局部存储器)[5];片内集成4 096 KB多核共享存储器和运行速率达1 600 MHz的64 bit DDR3存储器接口。

④ 集成大量基于SerDes的适用于芯片级、板级互连的高速接口,包括Serial Rapid IO(SRIO)、PCI-Express、Hyperlink、EMAC等。

1.2 VPX

针对传统CPCI和VME并行总线面对海量数据传输的瓶颈,VITA组织制定了VPX系列标准。VPX是超级计算机型架构,具备声纳和雷达系统所需要的众多处理能力和各种带宽的要求[6],其主要优势如下: IO数量剧增,6U板卡共可提供160个高速差分对,每差分对传输速率高达6.25 GBauds;增强供电能力,支持115 W/ 5 V、384 W/ 12 V、768 W/ 48 V;集成ESD保护机制的连接器,提供强大的定位机制。

VPX标准是支持包括PCI Express、Serial RapidIO、Infiniband、散热和加固等在内的多种子标准的总称[7],它包含VITA46.0[8]:基本标准,规范板卡电气性能和板卡尺寸;VITA46.1:VMEbus 在VPX的映射规范;VITA46.3:Serial RapidI/O在VPX的映射规范;VITA46.4:PCI-E在VPX的映射规范;VITA46.7:千兆网在VPX的映射规范;VITA46.9:XMC/PMC/GbE on VPX;VITA46.10:VPX的后I/O规范;VITA46.11 VPX系统管理规范;VITA46.12:VPX光纤接口规范;VITA46.20 :VPX交换槽位规范;VITA48.0:加固散热基础规范;VITA48.1:风冷子规范;VITA48.2:传导制冷规范;VITA48.2:液冷规范。

2 系统硬件设计

2.1 系统总体架构

系统总体架构贯穿通用处理平台设计思想。由于TMS320C667x系列器件管脚相互兼容、定浮点处理能力兼容,且与所有现有的C6000系列兼容[9],采用TMS320C667x作为核心处理器,在不改变PCB设计的情况下根据应用要求选装不同数量内核的处理器,可使系统兼顾高低端处理、定浮点运算的需求,不仅可用于动态范围大的雷达声纳信号处理,还可应用到图像、通信信号处理和数据处理,为系统赋予真正通用性。同时,TMS320C667x集成了大量高速串行互连接口,而基于高速串行互联的VPX规范可以满足苛刻环境和超宽带的雷达等军工需求[10]。因此,本系统将TMS320C667x和VPX完美地结合,电路以TMS320C667x为核心处理器,板卡尺寸、电气接口、机箱结构完全遵循VITA46和VITA48系列标准进行设计,构建出一套高速、高性能、全开放的通用处理平台。

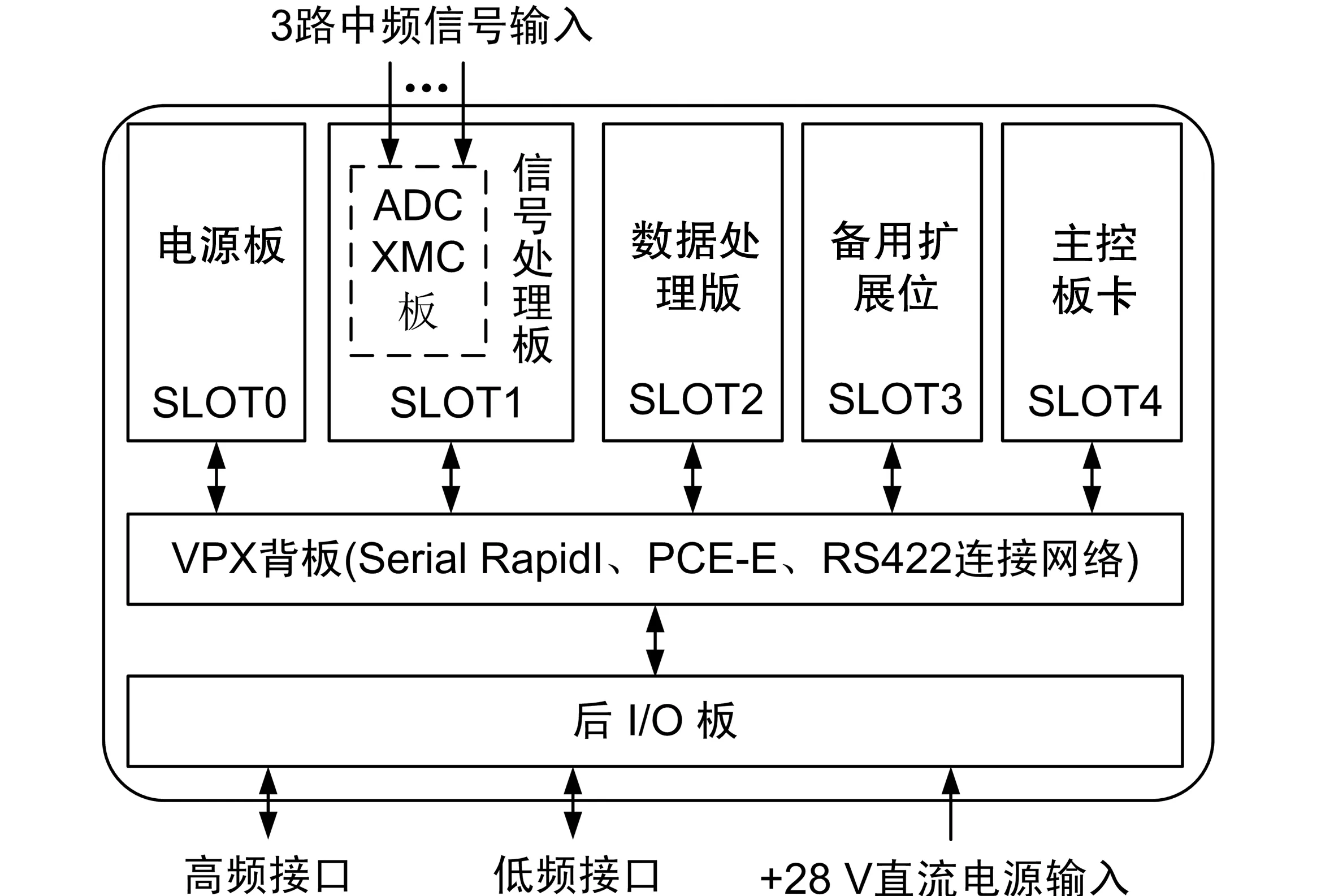

系统组成结构如图1所示。系统采用标准3U 5槽VPX机箱,含1块3U VPX背板、1块后I/O板、1块电源板、2块处理板(信号处理和数据处理)和1块主控板,其中信号处理板上安装ADC功能的XMC子卡,完成高速ADC和数字下变频功能,处理板实现雷达视频数字回波的信号处理和数据处理功能,主控板则通过解析外部命令实现系统启动、复位和时序控制等功能。系统通过VPX背板和后I/O板形成的通路实现对外信息交互,整个系统共对外提供4个千兆以太网口、32个用户自定义接口、4个全双工RS422接口和6个远程调试口。

图1 系统总体组成

系统槽位间采用0.8 inch中心间距标准,结构紧凑,可适应机载、弹载平台电子设备应用需求。同时,电路模块采用导冷散热,模块加固散热设计遵循VITA48.2,可满足机载等严酷的军用环境对冲击、振动、温度和海拔等的要求。

2.2 数据采集板

数据采集板设计成符合VITA42.0的XMC背板,主要完成输入中频模拟回波的A/D转换和数字正交解调。数据采集板含3路以ADS5474为主的数模转换通道,实现3通道14位、采样率400 MSPS的A/D转换,可分别对应雷达和、方位差和俯仰差支路回波的A/D变换;板载一片Xilinx公司的Virtex-6系列FPGA XC6VLX240T,含24×104个可编程逻辑单元和20个GTX高速低功耗链路口,可实现数字正交解调和高速数据通信功能;4片DDR3 SDRAM组成2组32位、容量4 Gbits的存储组,可以乒乓方式工作实现采集数据的缓存。

2.3 处理板

单个处理板组成框图如图2所示。处理板电气结构符合VITA46.0 3U板卡标准。板载2个TMS320C6678计算节点,每个计算节点配置独享的64位、工作频率667 MHz的 8 Gbits DDR3 SDRAM,共可提供358GFLOPS峰值处理能力;2个处理节点以点对点互连的高速Hyperlink口以分布式松耦合方式互联,避免了紧耦合互连方式中总线竞争、多管脚走线问题,具有传输速度快、低延迟的优点。

板载FPGA XC6VLX240T可组成5组4X SRIO,实现板内DSP和XMC或处理板对外接口。在FPGA中可实现5个4X SRIO 交换机功能和输入数据预处理功能。

对外接口包括2个2x PCI-E、1个4x SRIO和2个以太网MAC层接口,对外通信带宽宽。

2.4 背板高速互连拓扑

处理板提供了种类和数量丰富的高速串行链路接口,便于板卡间互连。板卡互连通过VPX背板实现。系统中每槽和其他各槽互连关系如下:通过板内FPGA 4x SRIO实现与相邻槽位的互连,通过2个DSP分别提供的2x PCI-E分别实现与其余两槽的互连,每Lane SRIO或PCI-E至少以3.125 Gbps速率运行,这种互连方式确保了任意2个槽位间均具有点对点高速互连接口,可用于槽位间大量数据传输。此外,系统内每个DSP的SGMII0接口均接入背板内千兆网交换器,外部设备通过交换器可访问系统内任意计算节点。

3 软件设计

3.1 系统软件架构

系统软件为嵌入式软件,主要由板级支持包BSP、操作系统内核、驱动、BOOT软件和应用软件等组件组成。BSP负责硬件初始化和操作系统内核载入等,为软件应用层提供大量的系统调用,主要包括DSP主频时钟设置、DDR初始化和中断初始化等;驱动主要包含DSP的SRIO、千兆以太网、Hyperlink、PCI-Express以及GPIO等驱动程序;BOOT包括基于EMIF16和SPI口等方式的BOOT软件。

系统支持源代码公开的嵌入Linux操作系统。系统中每个DSP的各核均可根据应用情况选择是否采用操作系统。在实时处理要求较高的应用中不推荐采用操作系统。

3.2 SAR成像处理模式应用软件

SAR成像处理模式对和支路回波进行SAR成像处理。采用3个子孔径成像拼接的SAR处理流程如图3所示。

图3 SAR成像处理模式应用软件流程

在这种模式中,信号处理板的2个DSP和数据处理板DSP1分别对雷达的1、2、3个孔径并行进行SAR成像处理,SAR成像处理过程中的距离脉压、幅度和计算、中心频率估计等处理过程经过细分由每个DSP的8核并行完成,有效区间估计、各核获得的中心频率和调频斜率的拟合由各DSP0#核完成,0#核在执行这些汇总信息处理前后,均需对其他核进行核间同步操作。各成像处理DSP获得的斜距图像传给数据处理板DSP2,由DSP2的8个核并行执行几何校正、子图拼接和图像处理后向主控板送出处理结果。

3.3 单脉冲处理模式应用软件

雷达单脉冲处理模式下通常需处理和支路、方位差支路、俯仰差支路回波。在本系统中,可由信号处理板DSP1的0#3#核完成和支路的脉冲压缩、相参积累,DSP2的0#3#核、4#7#核分别完成方位差、俯仰差支路的脉冲压缩、相参积累,DSP1的4#7#核完成目标检测,DSP1和DSP2根据检测结果往数据处理板送出3通道目标幅度、相位信息,数据处理板DSP1完成测角处理和跟踪算法处理,给主控送出处理结果。

4 测试结果分析

本系统主要硬件实物如图4所示。

图 4 硬件实物

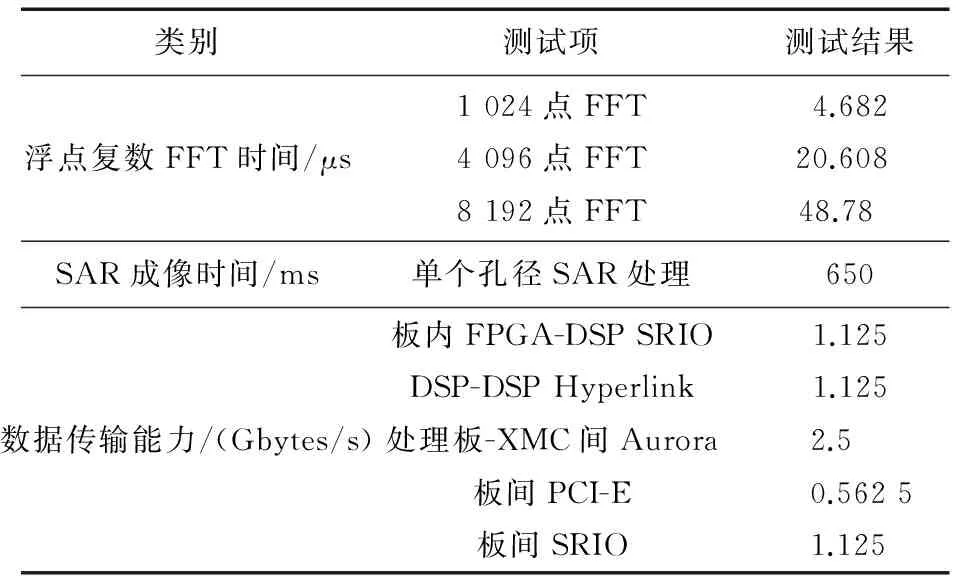

工程应用过程中,对系统处理能力和数据传输能力分别进行了测试,测试结果如表1所示。

表1 性能测试结果

表1中FFT为单精度浮点基2FFT运算,运行时旋转因子存在DSP的L2 Cache中;数据传输能力测试的是连续长时间误码为0时的有效数据传输率;SAR成像时间是单片TMS320C6678完成1个孔径SAR成像处理时间,孔径回波数据为距离向8 192点、方位向1 024点复数数据,距离压缩后有效距离长度1 024点。

从表1中可看出,TMS320C6678具有比ADSP-TS201更强的处理能力(单片ADSP-TS201完成8 192点FFT需耗时246.05 μs);系统采用高速串行链路获得了极高的数据通信率,即使是板间2x PCI-E链路接口,其有效数据传输率也大于并行PCI总线的理论峰值传输率(64位、66 MHz PCI运行速率528 Mbytes/s)。

5 结束语

在研究TMS320C6678和VPX系列标准的基础上,设计了一套基于TMS320C6678和VPX的雷达信号和数据处理系统,该系统结构、电气接口遵循VITA46和VITA48进行设计,结构紧凑,兼容高,低端信号处理,兼容定、浮点运算,是一套全开放式具有真正通用性的处理系统。测试结果表明,系统具有比ADSP-TS201类型的处理系统更强的处理能力和数传带宽。作为高效应用示例,介绍了基于多DSP多核并行处理的雷达或导引头SAR成像模式和单脉冲模式的应用软件流程。由于超强的处理能力和数据传输能力,系统还可推广应用到分子动力学等对定浮点运算能力及实时性有较高要求的超高性能计算领域;通过更换标准的XMC ADC板卡,整个系统可实现雷达DBF处理和STAP处理等多项功能。系统已应用到工程实践中,具有广阔的应用前景。

[1] 包利民,潘 奇.VPX 总线技术及其实现[J].电子机械工程,2009(2):57-60.

[2] 欧旺军.基于多核处理器的PD雷达信号处理算法设计[D].西安:西安电子科技大学,2014.

[3] 郑东卫,陈 矛,罗丁利.VPX总线的技术规范及应用[J].火控雷达技术,2009(4):73-77.

[4] 张明志.基于DSP和FPGA的并行处理系统硬件设计[D].北京:北京工业大学,2011.

[5] 杨 方.基于Tms320c6678的多核DSP并行处理应用技术研究[D].北京:北京理工大学,2014.

[6] VPX:VMEbus for the 21st century[M].America:GE Fanunc Embedded Systems,Inc,2007:3-6.

[7] 46.0-2007 ANSI/VITA.American National Standard for VPX Baseline Standard[S].

[8] 48.0-2007 ANSI/VITA.Mechanical Specifications for Microcomputers Using Ruggedized Enhanced Design Implementation[S].

[9] 徐 赟.基于Tms320c6678处理器的图像处理平台设计[D].成都:中国科学院光电技术研究所,2015.

[10]邢乃福.雷达高速数据传输技术研究[D].成都:电子科技大学,2013.

宋玉霞 女,(1973—),硕士,高级工程师。主要研究方向:雷达制导。

李 贵 男,(1982—),硕士,工程师。主要研究方向:雷达制导与对抗。

Design and Application of a Radar Processing System Based on TMS320C667x and VPX

SONG Yu-xia,LI Gui,GAN Feng,SHAO Jiang-yu

(SouthwestChinaInstituteofElectronicTechnology,ChengduSichuan610036,China)

For radar processing systems based on CPCI or VME,the data transmission and processing capability is a bottleneck.To address this issue,the design of a highly real-time processor based on multi-core DSP TMS320C667x from TI and VPX is presented,the design of software,hardware,electric structure and backplane topological structure is introduced,and the applications in SAR imaging and monopulse processing are proposed.The testing results in engineering application shown that this system has a better processing performance than traditional signal processor and a high-speed data transmission network matching with its high performance,and it has a good prospect of application.

processing system;TMS320C667x;VPX;SAR imaging;monopulse processing

10.3969/j.issn.1003-3106.2016.11.18

宋玉霞,李 贵,甘 峰,等.基于TMS320C667x和VPX的雷达处理系统设计及应用[J].无线电工程,2016,46(11):71-74.

2016-08-11

中国西南电子技术研究所发展基金资助项目(2011-098Y)。

TN958.94

A

1003-3106(2016)11-0071-04