基于FPGA的视频采集显示系统设计及研究

2016-02-06黄志斌

黄志斌

(江苏无线电厂有限公司,江苏 南京 210012)

基于FPGA的视频采集显示系统设计及研究

黄志斌

(江苏无线电厂有限公司,江苏 南京 210012)

文章首先对FPGA技术及其特点进行了简要阐述,在此次基础上,基于FPGA技术,对视频采集显示系统的相关设计问题进行了研究。文章期望能对视频采集显示系统设计水平的提升及系统性能的完善有所帮助。

FPGA;视频采集;显示;系统设计

1 FPGA技术及其特点

1.1 FPGA的构成

现场可编逻辑门阵列(Field programmable gate array,FPGA)是在PAL,GAL,GPLD基础上发展起来的一种现场可编程门阵列,适用于内部硬件逻辑更改,具备较强的设计灵活性。FPGA内部的组成部分包括嵌入式RAM、可编程逻辑单元、布线、专用硬盘、功能单元等,其中可编程逻辑单元极为丰富,能够满足设计者的多种系统设计需求。器件内部周边为可编程输入/输出单元,用于连接外部芯片输入输出管脚与内部控制模块,可编程输入/输出单元由可编程连线资源连接起来,使FPGA具备强大的逻辑功能。

1.2 FPGA的应用优势

与CPLD,PAL/GAL相比,FPGA的优势更为明显,具体表现为:

(1)逻辑功能强大。FPGA采用SRAM编程技术实现系统的快速运行,增强其逻辑功能;布线资源丰富,只需擦除更改程序,即可满足系统设计所需的不同逻辑功能;可编程I/O资源丰富,可满足复杂数字逻辑设计。

(2)设计灵活。FPGA内部的嵌入式RAM支持多种操作模式,异步先入先出(First Input First Out,FIFO)数据缓冲器可拓展FPGA的设计范围,使设计选择更加灵活;FPGA内部包含的逻辑门数较多,可满足复杂设计要求[1]。

(3)操作简便。为保证FPGA系统的可靠性,在使用FPGA芯片之前需进行稳定性测试,在此之后设计者只要利用软硬件环境便可设计系统功能;在实现FPGA系统不同逻辑功能时,设计者可通过多次反复编程予以实现,无需更改硬件电路。

2 基于FPGA技术的视频采集显示系统设计

2.1 系统总体设计方案

视频采集显示系统由两片FPGA、视频解码芯片、外存储器件SRAM等组成。其中,FPGA采集前端图像、处理后端数据;视频解码芯片将模拟信号转换为数据信号;存储器缓存数据[2]。在该系统中,由FPGA控制的视频解码芯片通过I2C总线进行初始化配置,输入8位视频数据、同步HS、场同步VS等。将视频数据转换成标准RGB格式的数据,在FPGA的控制下,配合时序信号,截图显示所需的像素,将其存入到SRAM中,显示在LCD/VGA屏幕上。视频采集系统的模块与功能具体包括:

(1)视频采集模块。采用4片视频解码芯片采集4路模拟视频信号,分离信号中的亮度与色度,获取同步信号和YUV分量。

(2)中央控制单元。这是视频采集显示系统的核心,由FPGA和外部晶振电路构成。FPGA负责采集视频信号,整合和存储视频数据,实现SRAM读写操作切换,连接外围电路进行通信。

(3)存储器模块。该模块将视频解码芯片输出的场同步信号周期作为切换的时间间隔,SRAM按照存储单元地址分为4个空间,用于4路视频信号存储,保证各路信号均可正常显示。

(4)电源模块。接入外部5 V电源,为内部芯片工作提供5 V电压,并将5 V电源进行低压处理,获得3.3 V和2.5 V电源,提供给其他器件使用。

(5)FPGA配置模块。每次启动系统后需加载相应程序,采用主动配置与被动配置相结合的方式重新配置FPGA,利用串行配置器件完成配置。

2.2 系统的具体工作流程

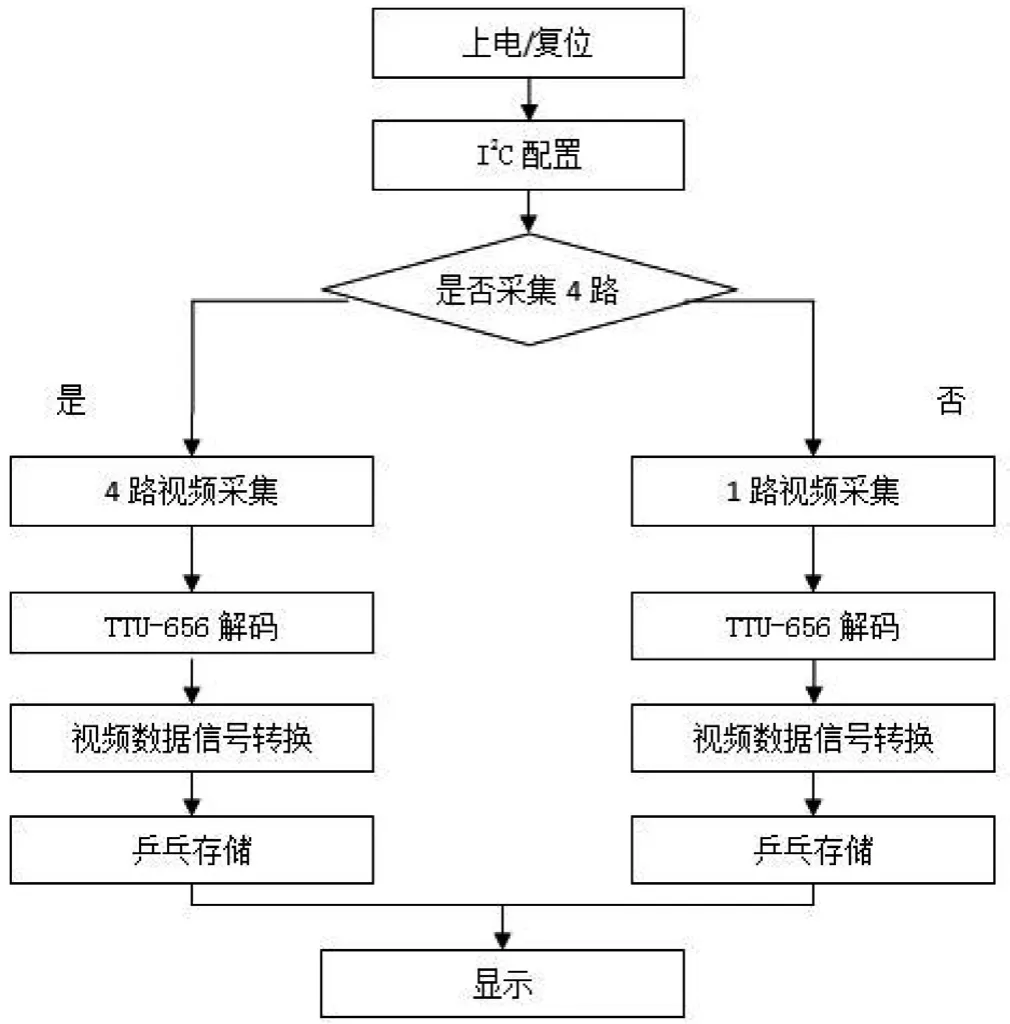

系统上电后,由配置芯片重新配置FPGA;配置完成后,FPGA对视频解码芯片进行初始化;视频解码芯片进入工作状态,采集4路模拟视频信号;FPGA初步处理4路数字视频信号;处理后,将4路视频数据存储到SRAM中;在TFTLCD上显示所采集的数字化视频信息;利用IO口,可在外部切换采集通道,对系统进行复位操作。具体工程流程如图1所示。

2.3 系统硬件与软件的设计方案

2.3.1 硬件设计方案

①视频解码。利用CCD摄像头采集模拟视频信号,包括亮度、色差、同步信号等。由于FPGA不能直接采集处理模拟视频信号,所以必须通过模数转换模块将其转换为数字视频信号。在转换过程中,需要先分离模拟信号中的亮度和色度,获取YUV分量,而后对YUV分量进行数字化,转换成RGB空间。

②视频缓冲。由FPGA负责检测和采集视频解码芯片输出的数字视频数据,FPGA是半定制电路,可弥补定制电路的缺陷,免除传统可编程器件门电路数的限制。FPGA采用逻辑单元列阵,内部包括输入输出模块、逻辑模块和内部连线。FPGA利用嵌入式平台保证运行的可靠性和稳定性,所以视频采集显示系统可利用FPGA检测和缓冲控制数字视频信号[3]。

图1 视频采集显示系统工作流程

2.3.2 软件程序设计方案

本系统的软件设计采用Quartus6.0作为开发平台,通过该平台来完成程序逻辑设计、仿真分析及下载等工作。

3 系统设计方案的具体实现

3.1 系统硬件的实现

本系统的硬件主要由两大部分组成,一部分是采集模块,另一部分是FPGA模块,下面分别对其实现过程进行论述。

3.1.1 采集模块的实现

①视频解码芯片。本系统的在对采集模块进行实现的过程中,选用了国内某公司自主研发的GM7113C视频解码芯片,之所以选用该芯片是因为它采用了当前较为流行的CMOS工艺,芯片能够对视频信号进行有效的解码,同时还能与DSP相接组成应用系统[4]。

②解码电路的设计。本次设计中选用的视频解码芯片的供电电压为3.3 V,属于低压供电,由此确保了芯片运行过程中的低能耗,各个电源可以通过100 nF的电容与地线进行可靠连接,这样能将高频干扰有效滤除掉。SDA和SCL接口为总线接口,其能够与FPGA相连接,由于这两个接口属于双向接口,故此需要在电路设计中分别在两个接口上各接一个上拉电阻,电阻值可控制在4.7 K。

3.1.2 FPGA模块的实现

①选型。本系统设计中,FPGA芯片选用的是EP2C8Q208芯片,由于该芯片采用的是全铜层工艺,故此其裸片尺寸相对较小。

②FPGA与SRAM接口电路的设计。本系统在设计时,图像缓存选用了IS61LV51216AL-10T,这是一个静态且高速的RAM,它的容量可以达到512 Kb,读写时间均为10 ns,符合系统的应用需要。

③FPGA与显示模块接口电路的设计。本系统在显示模块选用的是TFT-LCD液晶显示屏,分辨率为640*480,其所显示的图像格式为标准的RGB666格式,所需的数据线条数为18根,系统显示缓存的数据线为16位,在FPGA与显示模块进行连接时,可以采用565的电路连接方式,并通过低位补0的方法对差的3位数据信号进行补充。

3.2 系统软件的设计

3.2.1 LCD显示控制器

在本系统中,LCD控制器是通过硬件描述语言编程来实现的,它由以下几个部分组成:缓存读写控制、数据格式处理、时序产生。同时,外围接口包括微控制器接口、SRAM接口、LCD显示屏接口。

3.2.2 图像防抖动

对图像抖动问题的解决方法较为常用的有两种,一种是在系统设计中加如缓冲机制,借助FIFO的数据存储特性,实现数据在异步时钟间的无缝传输;另一种是同步时钟。鉴于第二种方法实现过程更加简单,所以设计时选用同步时钟进行图像防抖动。

4 结语

综上所述,FPGA技术以其自身所具备的逻辑功能强大、设计灵活、操作简便等优点,在相关系统的设计开发中获得应用。本文基于FPGA技术,对视频采集显示系统的设计进行了分析,通过FPGA技术的运用,使整个系统的设计过程得以简化,缩短了设计周期,提高了设计效率和质量。

[1]贡镇.基于FPGA的实时视频图像采集与显示系统的研究与实现[D].淮南:安徽理工大学,2013.

[2]岳振国.基于FPGA的视频采集与预处理系统的研究与设计[D].南京:南京邮电大学,2014.

[3]马超.基于FPGA的多通道视频图像采集预处理系统设计[D].北京:中国科学院研究生院,2014.

[4]时旭.基于FPGA的视频图像采集系统的设计[D].吉林:吉林大学,2016.

Design and research of video capture and display system based on FPGA

Huang Zhibin

(Jiangsu Radio Power Plant Co., Ltd., Nanjing 210012, China)

In this paper, the FPGA technology and its characteristics are briefly described in this paper, on the basis of the FPGA technology, the design of the video capture display system is studied. Through the discussion of this paper, aiming at improve the design level of the video capture display system and the performance of the system.

FPGA; video capture; display; system design

黄志斌(1987— ),男,江西抚州,本科;助理工程师;研究方向:基于FPGA的产品开发及应用。