星载统一测控载波跟踪环相位噪声分析*

2016-01-27陈翔,陈瑞龙

星载统一测控载波跟踪环相位噪声分析*

陈翔**,陈瑞龙

(上海航天测控通信研究所,上海 201109)

摘要:为了保证测速和测距精度,有效手段之一是在星载统一测控应答机上采用嵌套环路结构的载波跟踪环完成相干载波提取。由于利用了相干本振补偿多普勒频移,必须考虑输入相位噪声对本振相位噪声的影响。为了准确预测环路输出相位噪声性能,对环路中各部件贡献的相位噪声进行了分析。针对不同噪声源,运用信号流图的分析方法建立了对应的环路相位噪声模型,通过仿真计算得到了不同输入信号功率条件下的环路输出相位噪声功率谱,与实际电路的测试结果对比,证明了该环路相位噪声模型的准确性。应用该模型能提高环路设计的准确性和效率。

关键词:统一测控;载波跟踪环;嵌套环路;相位噪声模型

1引言

微波统一测控系统是国际上应用最广泛的陆基测控系统,残留载波统一测控应答机是该系统中的关键组成设备,一般装载在卫星、飞船、运载等空间飞行器上,配合地面测控站完成飞行器测速、测距、遥控、遥测以及通信的功能,是天地对接的重要通道。为了保证测速和测距精度,有效手段之一是在星载统一测控应答机上采用载波跟踪环完成相干载波提取[1]。

现有的报道文献中对锁相环相位噪声的研究方向主要集中在锁相频率合成,研究对象用于为通信接收机或者发射机提供本振或者为数字信号处理提供工作时钟,环路的参考频率和接收前端的输入载波频率来自于相互独立的振荡源,环路相位噪声与接收前端的输入载波相位噪声不相关,环路结构既有单环[2]也有双环[3],关键性能指标是相噪,S频段工作频率典型的相噪指标可达-97 dBc/Hz@1 kHz[4],研究方法多用理论分析加仿真。本文的研究方向是锁相接收机,研究对象用于捕获和跟踪地面站发出的上行信号,检测提取信号的载波频率和相位,确保下行信号的载波频率和相位与上行信号是相干的,从而完成高精度的测速和测距功能。为了满足在带宽受限的条件下跟踪低信噪比、大多普勒带宽以及快速频率扫描信号的要求,使用了嵌套环路结构,环路相位噪声指标会随着输入信噪比的降低而恶化,环路输出作为本振频率合成锁相环的参考,又会影响本振的相噪指标。为了快速准确地预测环路相位噪声性能,本文借鉴了部分文献的研究方法[5],在理论分析的基础上既进行环路相位噪声建模仿真,又进行了试验验证。

2环路结构分析

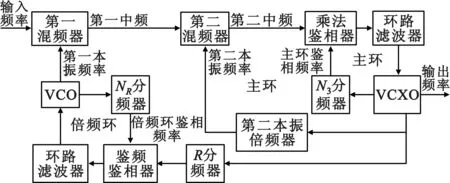

载波跟踪环的环路结构如图1所示,主要由主环和倍频环组成,主环用于提取带有多普勒频移的上行信号载波频率和相位,同时控制倍频环的参考输入,倍频环用于提供相干接收本振,与上行信号混频产生中频信号,因此在环路锁定的情况下抵消了很大一部分多普勒频移,降低了对本振频率稳定度的要求。实际环路中还包含了低噪声放大器、中频滤波器、中频自动增益控制(AGC)放大器,因为滤波器和放大器的带宽都远大于主环的环路带宽,所以在建立环路模型时可以不考虑滤波器和放大器的影响。环路中主环的输出频率一路经过分频作为主环鉴相频率,一路作为倍频环的参考鉴相频率,一路作为第二本振倍频器的参考频率。倍频环和第二本振倍频器的输出分别作为第一、第二混频器的本振频率,经过两次下变频将载波跟踪环的输入信号频率降到与主环鉴相频率一致,从而完成闭环。由于利用了相干本振补偿多普勒频移,必须考虑输入相位噪声对本振相位噪声的影响。

图1 载波跟踪环的环路结构

3环路相位噪声分析与建模

3.1相位噪声源分析

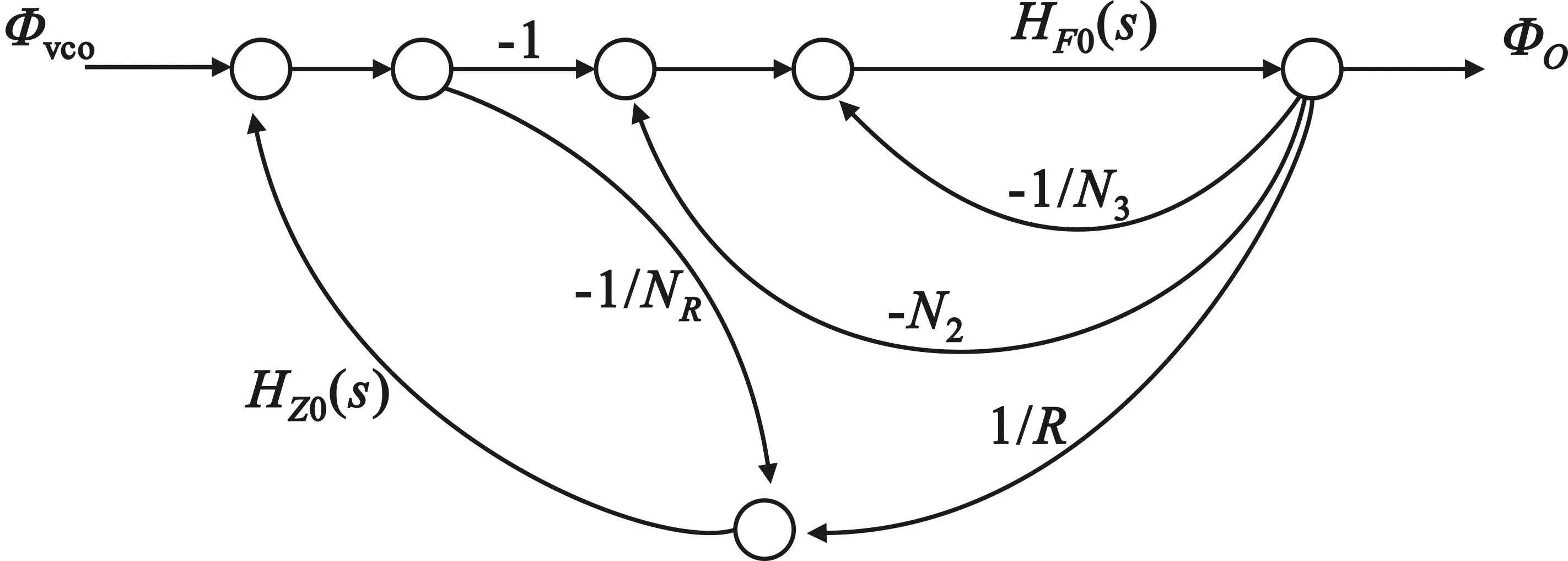

主环的组成部分包括乘法型鉴相器PD1、环路滤波器F(s)、压控晶体振荡器(VCXO)、反馈分频器。倍频环的组成包括鉴频鉴相器PD2、电荷泵(CP)、环路滤波器Z(s)、压控振荡器(VCO)。每一个组成部分都为整个环路的相位噪声做出了贡献,为了便于分析,把这些单元电路看作无噪声的理想部件,噪声用独立的等效噪声源表征[6]。基于以上分析,闭环相位噪声模型如图2所示。

图2 闭环相位噪声模型

在闭环相位噪声模型中,噪声源的组成比较复杂。除了输入相位噪声外,每一个电路部件是一个噪声源,这些噪声源组成了环路固有噪声。需要对这些噪声源的特性进行分析,以明确对最终环路输出相位噪声起主要作用的噪声源。此外,一般假设所有的噪声源都是独立的,每个噪声源经过环路的衰减、倍增或过滤后,再对所有的输出噪声功率谱进行叠加,就可以计算出整体环路的相位噪声。

3.1.1输入相位噪声

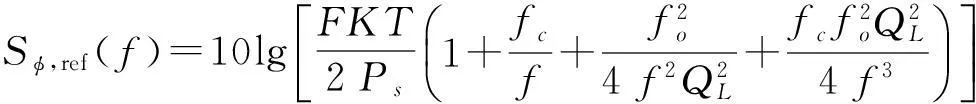

输入相位噪声φi包括地面站发射载波的参考相位噪声φref和接收机热噪声φT。发射载波的参考相位噪声属于振荡器型,相位噪声功率谱密度用Leeson模型[7]表示为

(1)

式中,F是噪声系数,K是Boltzman常数,T为温度,Ps为振荡器输出功率,QL为有载品质因数,fO为输出频率,fc为闪烁噪声拐角频率。

接收机热噪声属于白噪声,根据级联放大链路的热噪声模型和调相原理[1],热噪声贡献的相位噪声功率谱密度用对数形式表示为

(2)

式中,级联放大链路等效噪声系数为

(3)

当星载应答机通过测控天线接收到来自地面站的上行信号时,由于接收机具有自动增益控制功能,如果接收信号功率强,接收增益就小,热噪声被信号压制,此时上行信号载波本身的相位噪声是输入相位噪声的主要来源;如果接收信号功率弱,接收增益就大,信号可能被热噪声淹没,此时热噪声成为输入相位噪声的主要来源。因此,接收信号功率的强弱会直接影响环路相位噪声的组成,这也是载波跟踪环与一般频率合成锁相环的重要差异。

3.1.2固有相位噪声

固有相位噪声是指除输入相位噪声以外的组成环路各部件贡献的相位噪声,需要分析的主要部件包括VCO/VCXO、鉴相器、环路滤波器、混频器。

主环内的VCXO和倍频环内的VCO所带的相位噪声都属于振荡器型,也可以用Leeson模型表示。主环内的鉴相器和前级混频器都采用双平衡混频器实现,混频器的输出噪声主要是热噪声功率和本振相位噪声功率的叠加,因此主环鉴相器和前级混频器的相位噪声模型可以等效为式(2)所示的热噪声模型,混频器的单边带噪声系数和变频损耗可以直接计入级联放大链路等效噪声系数的计算公式(3)中去。

倍频环采用的鉴相器,其相位噪声功率谱密度表示如式(4):

Sφ,PD2(f)=FOM+20lg(fo)-10lg(fs)=

FOM+10lg(fs)+20lg(NR)。

(4)

其中,FOM表示鉴相器芯片的归一化相位噪声,对于确定的芯片这是一个固定参数,可以从厂家的技术手册中获得;fo是输出频率;fs是鉴相频率;NR是倍频环的反馈分频比。

主环和倍频环的环路滤波器都采用有源积分滤波器,环路滤波器的噪声源主要是电阻器和运算放大器。电阻器产生的噪声电压均方根值如式(5)表示:

(5)

式中,R为电阻值,B为工作带宽。

运算放大器产生的输入噪声电压均方根值为VA,可以从器件技术手册上查到若电压增益为A,VCO的压控灵敏度为KVCO,主环滤波器中电阻R11、R12、R13的噪声电压传递函数分别为TR11(s)、TR12(s)、TR13(s),计算表达式如表1所示,其中,τ1n=R1nC(n=1~3)。倍频环滤波器中电阻噪声电压的传递函数表达式在文献[8]中给出了详细结果,此处不再赘述。

电阻和运算放大器产生的噪声对压控振荡器进行调频,可以等效为压控振荡器产生的相位噪声,噪声功率谱密度表示为

, (6)

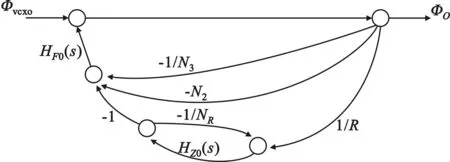

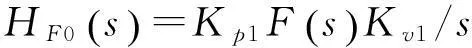

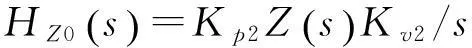

3.2嵌套环路相位传递模型的建立

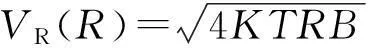

鉴于嵌套环路结构复杂,运用信号流图对闭环相位传递模型进行简化,由于不同的相位噪声源在环路中的注入位置不同,得到的相位传递模型信号流图结构也就有所不同,如图3所示。

(a)输入相位传递模型

(b)倍频环VCO相位传递模型

(c)鉴相器相位传递模型

(d)VCXO相位传递模型

(8)

(9)

(10)

利用梅森增益公式计算不同相位传递模型的传递函数,结果见表2。由于环路滤波器的相位噪声通过式(6)~(7)等效转换成VCO/VCXO的相位噪声,因此环路滤波器的相位传递模型与VCO/VCXO的相位传递模型是一致的。

表2 不同相位噪声源的传递函数

3.3环路相位噪声的仿真分析

由于环路的各种相位噪声相对于振荡器的输出功率都是微弱的,因此可以运用线性叠加原理将各个噪声源在对应的相位传递函数作用下产生的输出相位噪声功率进行叠加。在环路锁定的前提下,环路输出的总相位噪声功率谱密度表示为

(12)

利用MATLAB对上述模型进行仿真,为了模拟真实电路的行为,仿真参数设置与表3所列出的实际环路设计参数相同。

表3 实际环路设计参数

相位噪声环路传递增益的仿真曲线如图4所示。一般主环环路带宽远小于倍频环环路带宽,在这一前提下,环路对输入相位噪声和鉴相器的相位噪声呈现低通特性,对VCXO的相位噪声呈现高通特性,对VCO的相位噪声呈现带通特性。

图4 环路相位噪声功率传递增益-频率曲线

在主环环路带宽以内,VCXO和VCO相位噪声功率的闭环传递增益以40 dB/dec的斜率呈现高通特性。在主环环路带宽和倍频环环路带宽之间,对输入相位噪声和鉴相器相位噪声的功率传递增益按-20 dB/dec的斜率下降;对VCO相位噪声的功率传递增益按20 dB/dec的斜率上升。在倍频环环路带宽以外,输入相位噪声的功率传递增益按-20 dB/dec的速率下降;鉴频鉴相器相位噪声的功率传递增益按-40 dB/dec的速率下降。这是因为主环和倍频环的环路滤波器都采用有源积分滤波器,整个环路对各噪声源的相位传递增益是主环的相位传递增益和倍频环的相位传递增益叠加的结果。

4模型的验证与讨论

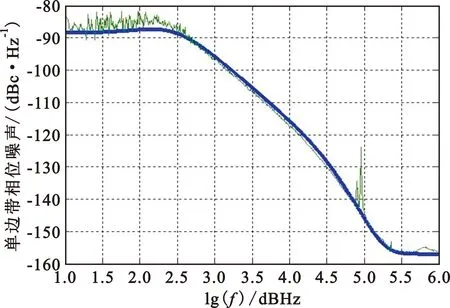

为了验证环路模型的正确性,对环路锁定条件下的实际电路进行了测试。测试方法是用Agilent公司的信号源E8267D产生输入信号,先用低相噪信号分析仪E5052B测试E8267D的相位噪声作为第一组数据,用于模拟地面站发射载波的参考相位噪声,再用E5052B测试环路输出的相位噪声作为第二组数据,用于与仿真结果比对。将第一组数据导入计算机,参与MATLAB模型的仿真计算,对计算结果作图得到仿真预测曲线。主环VCXO的实测相位噪声曲线与仿真预测曲线比对如图5所示。

(a)Ps=-40 dBm

(b)Ps=-120 dBm

为了衡量仿真模型的准确程度,相位噪声功率谱的仿真曲线与实测曲线的均方根误差计算如表4所示。可见,当输入信号功率Ps从-40 dBm变化到-120 dBm,实测结果和仿真结果之间呈现良好的一致性。在信号功率变化80 dB范围内,仿真与实测的最大均方根误差为2.13 dB。相对于输入弱信号,输入强信号时环路相位噪声模型的预测准确性更高。导致这一趋势的原因主要是接收链路里AGC的存在,输入强信号的链路增益远小于输入弱信号的链路增益,因此输入强信号时,由于放大器、混频器等非线性电路产生的杂散频率分量比较少,链路稳定性比较高。

表4 相噪功率谱密度仿真和实测结果的均方根误差

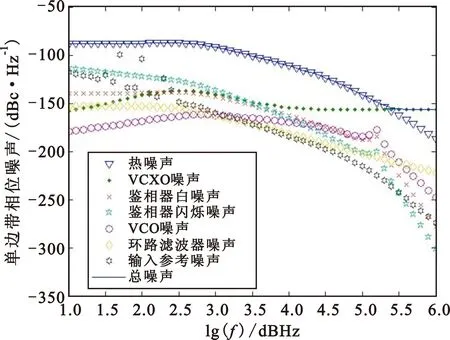

当输入信号功率变化时,各种噪声源对总噪声贡献的仿真结果如图6所示。

(a)Ps=-40 dBm

(b)Ps=-120 dBm

输入强信号时,在环路带宽内频偏近端,环路输出相位噪声主要来自于输入参考噪声和鉴相器噪声的合成;在频偏中段,环路输出相位噪声主要来自于鉴相器噪声和热噪声的合成;在环路带宽外的频偏远端,环路输出相位噪声主要来自于VCXO噪声。随着输入信号功率的减弱,在频偏的近端和中段,热噪声功率谱逐渐淹没了输入参考噪声和鉴相器噪声功率谱,成为最主要的噪声成分,在频偏远端,环路输出相位噪声仍然来自于VCXO噪声。

5结束语

由于环路结构的差异,导致统一测控载波跟踪环的环路相位噪声特性不同于一般频率合成锁相环相位噪声特性。为了定量分析这种差异,对星载统一测控载波跟踪环相位噪声特性进行了分析和建模,在不同输入信号功率条件下,对实际电路的输入和输出相位噪声功率谱进行测试,并与模型仿真计算的结果进行了对比,证明了采用相干本振的嵌套环路本振相位噪声需要考虑输入相位噪声的影响,环路输出的总相位噪声可以等效为由各种噪声源经各自对应的环路传递函数作用后叠加而成。理论分析和试验验证的结果也证明了星载统一测控载波跟踪环相位噪声模型能够比较准确地预测环路输出相位噪声功率谱。以往产品研制都是继承已有产品的设计参数,完成产品装配后才能测试验证是否满足指标,如不满足指标需要重新调试,应用该模型可以比较准确地预测环路相位噪声特性,使设计值尽量接近目标值,从而能够提高环路设计的准确性和研制效率。

参考文献:

[1]韩奎选.微波统一测控系统设计导论[M].北京:国防工业出版社,1984:156.

HAN Kuixuan. An Introduction to Microwave Uniform TT&C System Design[M].Beijing:National Defence Industry Press,1984:156.(in Chinese)

[2]杨沛,张磊,王平连,等.锁相环相位噪声的研究与仿真[J].电子测量技术,2009,32(4):35-37,48.

YANG Pei,ZHANG Lei,WANG Pinglian,et al. Research and Simulation of Phase Noise in PLL[J].Electronic Measurement Technology,2009,32(4):35-37,48.(in Chinese)

[3]胡晓文,方立君.一种双环锁相频率合成器的研究[J].合肥工业大学学报(自然科学版),2009,32(2):174-176.

HU Xiaowen,FANG Lijun. Research on a double phase-locked loop frequency synthesizer.[J].Journal of Hefei University of Technology(Natural Science),2009,32(2):174-176.

[4]张福洪,陶士杰,栾慎吉.锁相式频率合成器相位噪声分析与仿真[J].电子器件,2009,32(3):608-611.

ZHANG Fuhong,TAO Shijie,LUAN Shenji. Phase Noise Analysis and Simulation of PLL Frequency Synthesizer[J].Chinese Journal of Electron Devices,2009,32(3):608-611.(in Chinese)

[5]邓贤进,李家胤,张健.锁相频率合成器相位噪声的精确估计与仿真[J].西南科技大学学报,2006,21(1):59-63.

DENG Xianjin,LI Jiaying,ZHANG Jian. Accurate Phase Noise Prediction and Simulation in PLL Synthesizers[J]. Journal of Southwest University of Science and Technology,2006,21(1):59-63.(in Chinese)

[6]Lascari L.Accurate Phase Noise Prediction in PLL Synthesizers[J].Applied Microwave&Wireless,2000(7):30-38.

[7]Leeson D B.A Simple Model of Feedback Oscillator Noise Spectrum[J].Proceedings of the IEEE,1966,54(2):329-330.

[8]Kim Y W,Yu J D.Phase Noise Model of Single Loop Frequency Synthesizer[J].IEEE Transactions on Broadcasting,2008,54(1):112-119.

陈翔(1982—),男,山东青岛人,2008年获工学硕士学位,现为上海航天测控通信研究所工程师,主要研究方向为卫星测控通信;

CHEN Xiang was born in Qingdao,Shandong Province,in 1982.He received the M.S. degree in 2008. He is now an engineer. His research concerns space TT&C and communication.

Email:cxtisme@163.com

陈瑞龙(1988—),男,黑龙江虎林人,硕士,工程师,主要研究方向为射频电路设计。

CHEN Ruilong was born in Hulin,Heilongjiang Province,in 1988. He is now an engineer with the M.S. degree. His research concerns RF circuit design.

引用格式:陈翔,陈瑞龙.星载统一测控载波跟踪环相位噪声分析[J].电讯技术,2015,55(4):435-440.[CHEN Xiang,CHEN Ruilong.Phase Noise Analysis of Spaceborne Uniform TT&C Carrier Tracking PLL[J].Telecommunication Engineering,2015,55(4):435-440.]

Phase Noise Analysis of Spaceborne

Uniform TT&C Carrier Tracking PLL

CHEN Xiang,CHEN Ruilong

(Shanghai Spaceflight Institute of TT&C and Telecommunication,Shanghai 201109,China)

Abstract:To guarantee speed and range measurement accuracy, one of the effective means is to apply the carrier tracking phase locked loop(PLL) with nested loop structure in the spaceborne uniform TT&C transponders for acquiring coherent carrier.Because coherent local frequency is used to compensate Doppler shift,it is necessary to consider the effect of input phase noise on local oscillator phase noise.To predict loop output phase noise performance precisely,loop phase noise models of different noise components are built by means of analyzing signal flow graph and phase noise each component contributes.Output phase noise power spectrum density(PSD) with different input signal power is simulated and calculated.The accuracy of loop phase noise is verified by comparing the result of simulation with that of actual circuit. Using this model can improve loop design accuracy and efficiency.

Key words:uniform TT&C;carrier tracking PLL;nested loop;phase noise model

作者简介:

中图分类号:TN927

文献标志码:A

文章编号:1001-893X(2015)04-0435-06

通讯作者:**cxtisme@163.comCorresponding author:cxtisme@163.com

收稿日期:*2014-11-04;修回日期:2015-01-26Received date:2014-11-04;Revised date:2015-01-26

doi:10.3969/j.issn.1001-893x.2015.04.015