AES—128算法的集成电路设计方法

2016-01-15王春蕾

王春蕾

摘要:该文从降低资源消耗的目标出发,提出了AES-128算法的集成电路设计方法。使用Verilog HDL语言进行RTL级建模,采用ModelSim工具进行功能仿真,完成了FPGA验证,综合结果表明本设计实现了降低硬件资源消耗的目标。

关键词:AES-128;加密;解密

中图分类号:TP301.6 文献标识码:A 文章编号:1009-3044(2015)18-0038-02

1.概述

随着计算机网络的发展,信息的安全性和保密性尤为重要。加密技术是对通信系统或者存储系统中的数据信息进行保护的一种重要方式。高级加密标准AES(Advanced Encryption Standard)密码算法,是一种高效、安全的对称加密算法,目前已经成为加密各种形式电子数据的标准,被广泛应用于通信、网络、金融等领域。本文从降低资源消耗的目标出发,提出了AES-128算法的集成电路设计方法。

2.AES-128算法原理

2.1AES-128算法简介

AES密码算法是一种迭代分组算法,采用128bits的数据分组长度,三种可选密钥长度128bits,192bits和256bits。本文采用128bits密钥长度的AES算法,加密过程需要经过10轮迭代,每一轮操作包括字节替换(SubBytes)、行移位(shiftRows)、列混合(MixColumns)和子密钥加(AddRoundKey)四种变换。解密过程是加密过程的逆过程。其中,在加密和解密过程中所需要的每轮子密钥由种子密钥经过一个密钥扩展算法产生。

2.2ALES-128算法工作模式

算法工作模式是指以128位的明文分组长度为基础,构造一个对待加密数据进行分组、加解密的密码系统。论文实现了AES-128算法的ECB非反馈模式和CBC反馈模式,符合低功耗、低成本的设计目标。

2.2.1电子密码本ECB(Electronic Code Book)模式

加解密过程是首先将明文或密文分成128位长度的数据分组,如果最后一个分组不足128位,则进行填充,然后对每一个分组进行加解密。由于每次加解密使用相同的初始密钥,所以加密相同的明文分组将产生相同的密文分组。密码分析者有可能利用这些规律得到明文、密文对,对信息安全造成威胁。但是,该模式可并行运算,具有速度优势,一般用于短数据加密。

2.2.2密码分组链接CBC(Cipher Block Chaining)模式

CBC模式克服了ECB模式的缺陷,加密相同的明文将产生不同的密文。加密过程的输入是当前明文和前面密文异或的结果,所以相同的明文分组会产生不同的密文分组。同样,解密过程的输人是前面密文分组和当前解密后的明文分组异或的结果。

3.体系结构设计

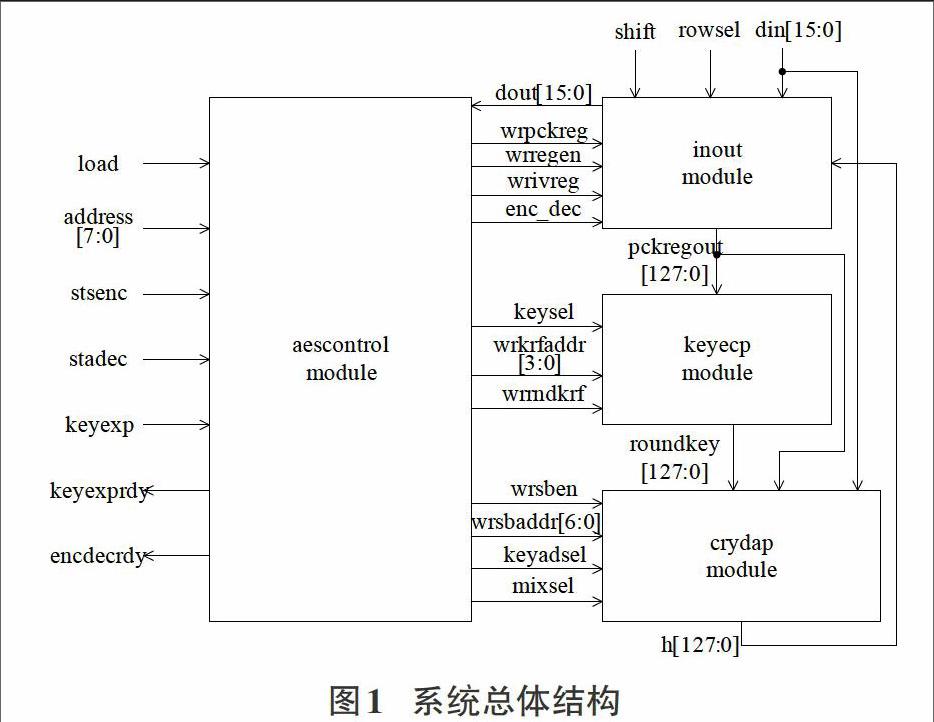

如图1所示,本系统由控制模块(aescontrol module)、输入输出寄存器模块(inout module)、密钥扩展模块(keyexp module)和加/解密模块(crydap module)组成。

3.1控制模块

该模块产生控制信号,负责协调其它模块有序地工作。

3.2密钥扩展模块

该模块实现初始密钥的11轮密钥扩展功能,并将产生的轮密钥输入到加,解密模块。一方面,本系统采用密钥扩展电路与加/解密电路分时的工作方式;另一方面,考虑到最终要将本系统模型下载到FPGA中进行验证测试,FPGA芯片能够提供足够的RAM单元;因此,该模块采用先扩展后存储的静态密钥调度方式,将每一轮扩展得到的轮密钥分别存储在128位寄存器中。该设计方法充分利用了硬件资源,同时又提高了处理速度,符合设计要求。

3.3加/解密模块

该模块根据控制信号分时进行加密或解密,执行具体的10轮轮迭代操作。由于解密过程是加密过程的逆过程,不能使用完全相同的电路,为了消除硬件结构的差异,设计中将字节变换和列混合变换进行了优化处理。其中,字节变换采用查找表的实现方法,列混合变换和逆列混合变换通过算法优化进行整合。

3.4输入输出寄存器模块

该模块负责数据的串并转换以及实现ECB、CBC两种工作模式。它由四个128位移位寄存器组成,分别是初始变量寄存器,明文,密文寄存器,密钥寄存器,输出寄存器。本设计采用16位的数据端口,通过移位将8个时钟周期内依次输人的16位明文/密文、密钥、初始变量分别保存在相应的移位寄存器中,并送到加懈密模块和密钥扩展模块;同样,加懈密模块产生的结果被送到该模块的输出寄存器中,采用16位数据移位输出的方法输出。

4.Verilog模型建立与仿真

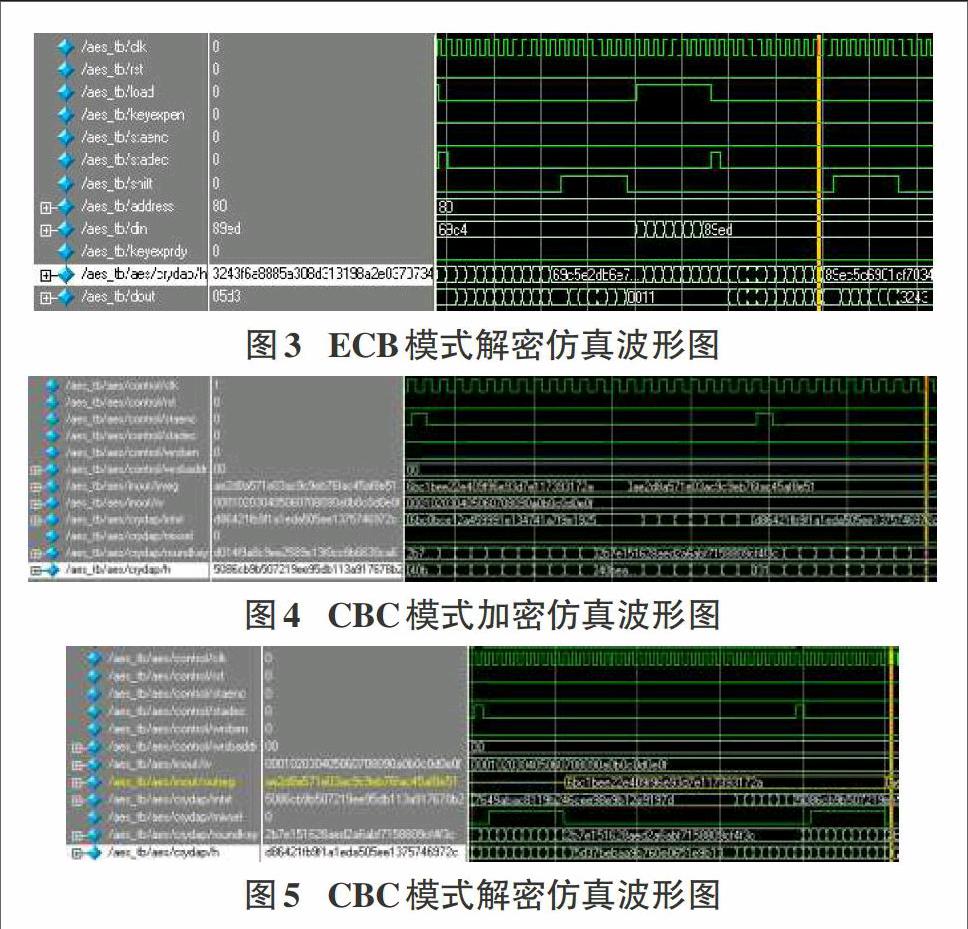

本系统使用Verilog HDL硬件描述语言对上述体系结构进行建模,使用ModelSim开发工具进行仿真验证。根据文献,使用测试数据进行ECB模式和CBC模式下的功能测试,具体仿真波形图如图所示,仿真结果完全正确。

5.FPGA实现与测试

在前面仿真验证的基础上,选用Mtera公司Cyclone系列的EPlCl2Q240C8 FPGA芯片,使用QuartusII 7.0综合工具进行系统的逻辑综合、布局布线和时序仿真。综合报告如图6所示。综合结果表明该设计方案的综合结果表明本系统硬件资源消耗较少,基本达到了低成本的预期设计目标。

6.总结

本文提出了AES-128算法的集成电路设计方法,在所设计的体系结构框架下,使用Verilog HDL语言进行建模,采用Mod-elSim工具进行功能仿真。通过测试本系统在ECB和CBC模式下的仿真结果,验证了系统逻辑功能的正确性。最后在Altera公司的QuartusII 7.0开发工具上完成综合编译,综合结果表明本设计实现了降低硬件资源消耗的目标。