阱接触面积对PMOS单粒子瞬态脉冲宽度的影响

2016-01-08刘蓉容,池雅庆,何益百等

阱接触面积对PMOS单粒子瞬态脉冲宽度的影响*

刘蓉容1,池雅庆1,2,何益百1,窦强1

(1.国防科学技术大学计算机学院,湖南 长沙 410073;

2.电子元器件可靠性物理及其应用技术重点实验室,广东 广州 510610)

摘要:使用TCAD模拟工具分析了纳米工艺下阱接触面积对PMOS SET脉冲宽度的影响。结果表明,纳米工艺下,当存在脉冲窄化效应时,增加阱接触面积会导致SET脉冲变宽,这与传统的通过增加阱接触面积可抑制SET脉冲的观点正好相反。同时,还分析了不同入射粒子LET值以及晶体管间距条件对该现象的作用趋势。

关键词:阱接触面积;单粒子瞬态;PMOS;脉冲宽度

中图分类号:TP303 文献标志码:A

doi:10.3969/j.issn.1007-130X.2015.06.004

收稿日期:*2014-04-30;修回日期:2014-08-14

基金项目:国家重点实验室开放基金(ZHD201202)

作者简介:

通信地址:410073 湖南省长沙市国防科学技术大学计算机学院

Address:College of Computer,National University of Defense Technology,Changsha 410073,Hunan,P.R.China

ImpactofwellcontactareaonthePMOSSETpulsewidth

LIURong-rong1,CHI Ya-qing1,2,HEYi-bai1,DOU Qiang1

(1.CollegeofComputer,NationalUniversityofDefenseTechnology,Changsha410073;

2.NationalKeyLaboratoryofScienceandTechnologyonReliabilityPhysics

andApplicationTechnologyofElectricalComponent,Guangzhou510610,China)

Abstract:We analyze the impact of well contact area on the PMOS SET pulse width in nano-technology using TCAD simulations. Simulation results show that in nano-technology, increasing the well contact area can broaden the SET pulse width due to the pulse quenching effect, which contradicts the traditional view that increasing the well contact area can effectively mitigate the SET pulse. Meanwhile, the tendency of this phenomenon under different incident particle LET values and transistor gaps is also analyzed.

Keywords:wellcontactarea;singleeventtransient;PMOS;pulsewidth

1引言

单粒子瞬态SET(SingleEventTransient)是应用于空间辐射环境下的集成电路的重要可靠性问题。高能粒子入射器件导致的单粒子瞬态会沿着电路的组合逻辑路径传播,如果该瞬态在路径末端被时序单元锁存则会产生错误数据。随着集成电路工艺的缩减,工作电压的降低以及工作频率的升高使得组合逻辑中SET导致的软错误越来越普遍,并且在先进工艺下将超过存储单元中产生的错误[1]。

SET落在锁存单元“建立-保持”窗口,从而导致软错误的概率与SET脉冲宽度正比例相关,分析影响脉冲宽度的相关因素,对于提出有效的SET加固措施具有重要意义。改变衬底浓度、阱掺杂浓度等虽然可以抑制SET脉冲宽度[2,3],但由于涉及工艺参数的调整,可行性较低。基于版图的分析成为学者们的研究重点。学者们研究发现,面积较大的阱接触可以在粒子轰击之后更好地维持阱电势,降低电荷的收集量,从而有效地抑制SET脉冲[4,5]。纳米工艺下,电荷共享效应普遍存在,粒子轰击位置邻近的多个晶体管都可能同时收集电荷[6]。因此,在分析阱接触面积对SET脉冲宽度的影响时,多个器件的电荷收集成为必须考虑的因素。

本文使用TCAD(Technology-Computer-Aided-Design)模拟工具,探讨分析了纳米工艺下阱接触面积对SET脉冲宽度的影响。由于PMOS(P-channelMetalOxideSemiconductorfieldeffecttransistor)晶体管产生的SET是电路全部SET的主要贡献,同时PMOS晶体管之间的电荷共享效应更为显著[7],因此本文仅以PMOS晶体管为研究对象。模拟结果表明,在考虑了多个器件的电荷收集的情况下,增加阱接触面积对于抑制SET脉冲并不总是有效。入射粒子LET(LinearEnergyTransfer)值的变化以及晶体管间距的变化,都可能导致阱接触面积对SET脉冲宽度的影响呈现不同的趋势。

2模拟设置

2.1器件模型

我们使用Synopsys公司的SentaurusTCAD工具对一个六级反相器链进行SPICE/3D混合模拟,如图1所示。其中第二级和第三级的PMOS晶体管(即P1和P2)使用3D器件模型,电路中的其余部分均采用SPICE集约模型。PMOS晶体管的尺寸为Wp∶Lp= 450nm∶65nm,NMOS晶体管的尺寸为Wn∶Ln=300nm∶65nm。

Figure 1 6-stage inverter chain for 3D simulation 图1 用于混合模拟的六级反相器链

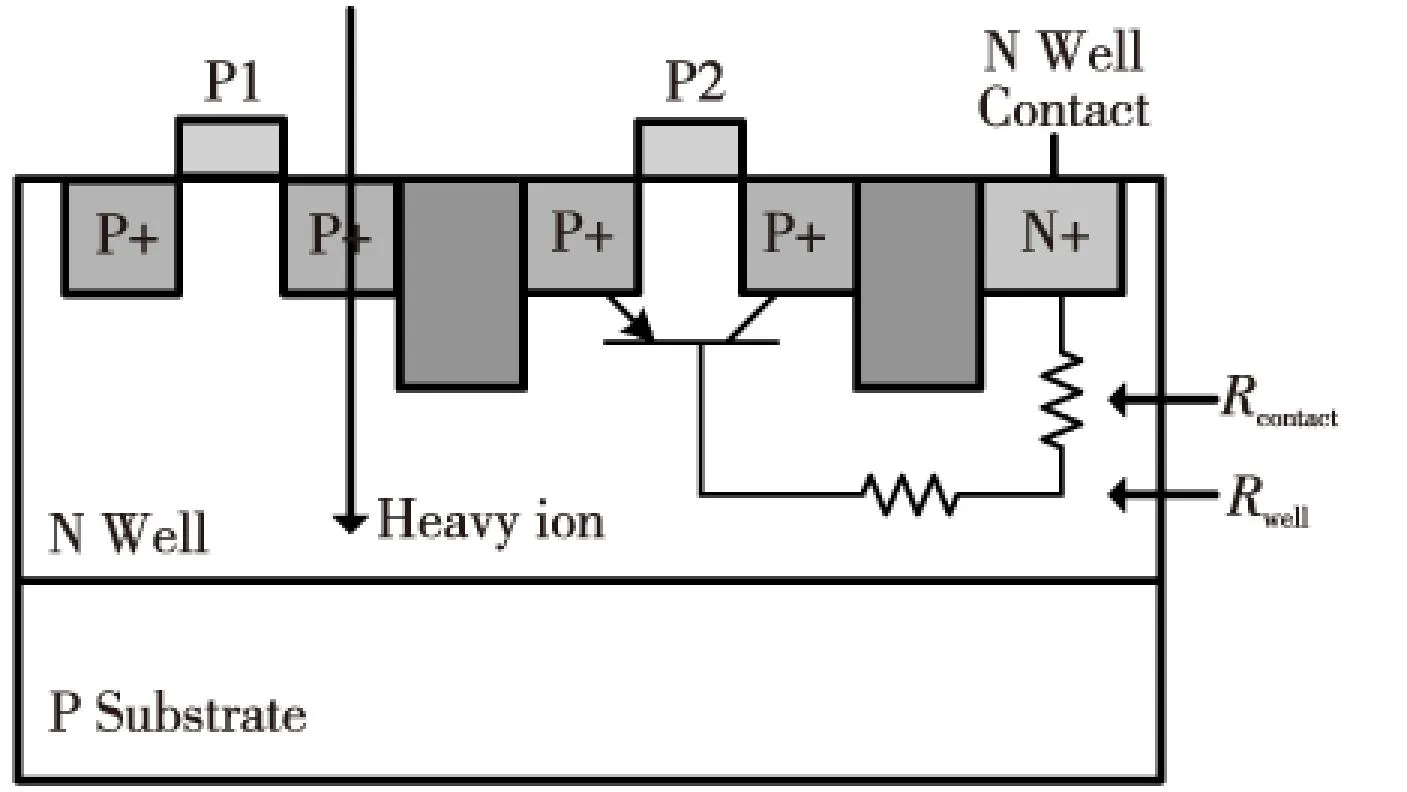

图2所示为用于模拟的3DTCAD器件结构。整个器件的尺寸为 10μm× 10μm× 5μm,N阱宽度为3.78μm。两个PMOS晶体管P1和P2位于器件中间,二者之间的间距为0.9μm。PMOS晶体管根据某商用65nm体硅CMOS工艺的PDK(ProcessDesignKit)工具进行了校准。

Figure 2 3D TCAD models with different well contact structures 图2 具有不同阱接触结构的3D TCAD器件模型

为了分析阱接触面积对SET脉冲宽度的影响,我们对器件模型中的阱接触进行了不同的构造。在第一种结构中,长条型阱接触位于N阱中间位置并横亘整个N阱,与PMOS晶体管距离210nm,如图2a所示。阱接触宽度为0.38μm,阱接触面积与N阱面积的比例即为10.05%。在图2b所示第二种结构中,我们构造了10个尺寸为0.38μm× 0.5μm的阱接触,它们相距0.5μm。我们将其称为分离型阱接触。该结构中,阱接触面积与N阱面积的比例为5.03%。在后续的两种分离型结构中,我们使用了同样尺寸的阱接触,但它们之间的距离分别为1μm和4μm,与此相对应,阱接触面积与N阱面积的比例分别为3.52%和1.51%。在最后一种结构中,如图2c所示,仅仅只构建了一个尺寸为0.38μm× 0.5μm的单点型阱接触。该结构中,阱接触面积与N阱面积的比例为0.50%。

2.2模拟条件

器件的工作电压设置为1.0V。整个模拟过程中,反相器链的输入始终保持为“低”,因此P1为关断状态,是敏感节点,而P2为开启状态,是非敏感节点。没有粒子轰击时,根据反相器链的电学特性,中间节点(图1中的n3)以及末端(图1中的n7)处的电压均为“低”。模拟采用LET为30MeV-cm2/mg 的重离子进行。根据SRIM(Stopping and Ranges of Ions in Matter)软件计算出的离子入射硅的径迹参数,我们将粒子径迹的深度和半径分别设置为5 μm和50 nm。模拟过程中,粒子的轰击位置为P1晶体管的漏极中心,且垂直于轰击器件的表面。粒子轰击之后,我们首先提取轰击节点处(n3)产生的SET脉冲宽度,随后在反相器链的末端(n7)再次提取SET脉冲宽度。

模拟中使用以下的物理模型:(1)费米-狄拉克统计;(2)禁带窄化模型;(3)掺杂浓度相关的Auger复合以及SRH复合模型;(4)载流子-载流子碰撞迁移率模型;(5)入射粒子模型为高斯分布,特征系数为1/e,半径50nm,半衰时间指数为0.25ps;(6)载流子输运使用流体动力学模型。所有的模拟在高性能服务器上进行。

3结果与分析

图3显示了当入射粒子LET值为30MeV-cm2/mg时,阱接触面积变化对n3处SET脉冲宽度的影响。从图3中可以看出,脉冲宽度随着阱接触面积的增加而降低。阱接触面积占N阱面积的比例从0.50%增大至10.05%,n3处的SET脉冲宽度从712ps下降至495ps。图4显示了采用同样粒子入射时,阱接触面积变化对n7处SET脉冲宽度同样具有显著的影响,但影响趋势则跟图3恰好相反。当阱接触面积占N阱面积的比例从0.50%增大至10.05%时,n7处脉冲宽度从89ps急剧增加至490ps。

Figure 3 Impact of well contact area on the pulse width of SET at node n3 图3 n3处SET脉冲宽度与阱接触面积的关系

根据以上结果,从抑制SET脉冲在组合逻辑路径中传播的角度考虑,降低阱接触面积可以有效降低SET的脉冲宽度。这与NarasimhamB等人在文献[4]中的结果正好相反。在他们的研究中,增加“阱接触面积/阱面积”的百分比,可以有效抑制SET脉冲宽度。导致这一相反结论的主要原因可以归结于脉冲窄化效应的影响[8]。脉冲窄化效应可以通过延迟的电荷收集而导致向下传播的SET脉冲宽度变窄。根据图3和图4,我们将不同阱接触面积下n3与n7处的SET脉冲宽度进行比较,可以发现,当阱接触面积比例为10.05%时,n3处的脉冲(即粒子轰击处产生的初始脉冲)与n7处的脉冲(即经过反相器链传播之后的脉冲)宽度几乎相同。而当阱接触面积比例为0.50%时,n7处的脉冲明显窄于n3处的脉冲。因此,以上数据表明降低阱接触面积,显著增强了脉冲窄化效应。

Figure 4 Impact of well contact area on the pulse width of SET at node n7 图4 n7处SET脉冲宽度与阱接触面积的关系

电荷共享的强弱是影响脉冲窄化效应的关键因素之一。具有较强电荷共享的电路会导致脉冲窄化效应更为显著,并进而使得传播之后的SET脉冲宽度更窄。阱接触面积的变化不仅会影响被直接轰击的P1晶体管的电荷收集以及产生的SET脉冲宽度,同时也会对P2晶体管的电荷共享强弱程度产生影响。P2晶体管的电荷收集主要由寄生双极放大效应产生,该部分电量与粒子入射产生的电荷从N阱中被泄放出的速度直接相关。电荷从N阱中跑掉的速度越慢,N阱中的过剩电荷量越高,从而导致阱电势恢复变慢,形成更明显的双极放大效应。阱接触的电阻,作为电荷泄放通路的组成部分,是决定电荷泄放速度(即恢复电流)的关键因素,如图5所示。较大面积的阱接触,即较小的Rcontact,可以降低电荷泄放通路上的电阻,加快阱电势的恢复速度,从而降低P2晶体管的电荷收集量,相应地,脉冲窄化效应也被弱化。因此,阱接触对n3处的初始脉冲和n7处的窄化后脉冲的影响正好相反。

Figure 5 Schematic diagram of the charge sharing in P2 transistors 图5 P2晶体管的电荷共享示意图

4讨论

4.1与粒子LET的相关性

为了进一步分析不同粒子LET情况下,阱接触面积对SET脉冲宽度的影响,我们使用LET值为5~50MeV-cm2/mg的粒子进行了模拟。图6给出了阱接触面积所占比例为10.05%和0.5%两种情况下,n7处SET脉冲宽度随粒子LET的变化。首先我们可以从图6中看出,两种情况下,SET脉冲宽度一开始都是随着LET的增大而增加,当LET值增大到一定程度时,脉冲宽度又随着LET的增大而减小。这与文献[2]中的结果相符。从图6中可以观察到的另一个现象是,阱接触面积不同,SET脉冲宽度达到峰值所需要的LET值也不同。当阱接触面积所占比例为10.05%时,脉冲宽度峰值出现在LET值为20MeV-cm2/mg处,而当阱接触面积所占比例为0.50%时,脉冲宽度峰值出现在LET值为30 MeV-cm2/mg处。这一现象导致两条曲线在LET值约为23 MeV-cm2/mg处出现了交叉。

Figure 6 Impact of well contact area on the pulse width of SET at node n7 with different particles LET values 图6 不同粒子LET下阱接触面积对n7处脉冲宽度的影响

当入射粒子LET值小于23MeV-cm2/mg时,由于电荷共享导致的脉冲窄化效应极不明显,SET脉冲宽度在传播过程中基本不会发生变化,因此,增加阱接触面积可以抑制初始脉冲宽度,从而抑制反相器链末端的SET宽度;而当入射粒子大于23 MeV-cm2/mg时,此时脉冲窄化效应成为主要因素,增加阱接触面积削弱了该效应,反而导致SET宽度的增加。因此,设计者在进行加固设计时,需要结合电路实际应用的辐射环境,决定阱接触面积的大小。

4.2与器件间距的相关性

P1晶体管和P2晶体管之间间距不同时,阱接触面积对SET脉冲宽度的影响也可能表现出不同趋势。我们保持其他模拟条件不变,将P1和P2的间距从0.9μm逐渐增大至1.2μm、1.5μm、1.8μm以及2.1μm,使用LET值为30MeV-cm2/mg的粒子进行了模拟。图7所示为阱接触面积所占比例为10.05%和0.5%两种情况下,n7处SET脉冲宽度以及n7/n3脉冲宽度比值随P1和P2间距的变化。从图7a中可以看出,当阱接触面积比例为10.05%时,n7处的SET脉冲宽度不受P1和P2晶体管的间距变化的影响,始终保持为495ps。而阱接触面积比例为0.5%的情况下,SET脉冲则随着间距的增加而增加,并且当间距为2.1μm时,达到612ps,超过了较大阱接触面积下的495ps。

Figure 7 Impact of well contact area on the pulse width of SET at n7, and ratio of n7/n3 pulse width with different transistor spacing 图7 不同晶体管间距下阱接触面积对n7处脉冲宽度和 n7/n3宽度比值的影响

晶体管的间距的变化会影响器件之间的电荷共享强弱程度。通过前文的分析可知,当阱接触面积为10.05%时,即使晶体管间距为0.9μm,也没有形成电荷共享。因此,图7b中n7处的脉冲始终与n3处的脉冲宽度一致。对于阱接触面积比例为0.50%这种情形,随着晶体管间距的逐渐增大,电荷共享导致的脉冲窄化效应减弱,n7/n3脉冲宽度的比值逐渐上升,当间距增大到2.1μm时,由于电荷共享效应完全消失,n7处脉冲等于n3处的脉冲。上述结果表明,当晶体管间距较小时,减少阱接触面积可以降低SET脉冲宽度。

5结束语

通常,增加阱接触面积来抑制SET脉冲宽度被认为是一种有效的加固手段。本文使用TCAD工具,对纳米工艺下PMOSSET脉冲宽度与阱接触面积的相关性进行了模拟分析。结果表明,在考虑了纳米工艺下普遍存在的电荷共享之后,增加阱接触面积会削弱脉冲窄化效应,反而导致在组合逻辑路径中传播的SET脉冲更宽。当入射粒子LET较高或者晶体管间距较近时,由于电荷共享效应更为显著,增加阱接触面积对SET脉冲宽度的负面影响也越明显。该结果意味传统的加固思路面临失效甚至会恶化电路的抗辐射特性。因此,对于设计者来说,需要考虑电路实际应用的辐射环境以及版图设计等因素,根据晶体管间电荷共享的强弱程度来选择适当的阱接触大小。

参考文献:

[1]MavisDG,EatonPH.SEUandSETmodelingandmitigationindeepsubmicrontechnologies[C]//Procofthe45thInternationalReliabilityPhysicsSymposium,2007:293-305.

[2]QinJun-rui,ChenShu-ming,LiuBi-wei,etal.TheeffectofP+deepwelldopingonSETpulsepropagation[J].ScienceChinaTechnologicalScience,2011,55(3):665-672.

[3]QinJun-rui,ChenShu-ming,LiuBi-wei,etal.Themodulationeffectofsubstratedopingonmulti-nodechargecollectionandsingle-eventtransientpropagationin90-nmbulkCMOStechnology[J].ChinesePhysicsB,2011,20(12):129401.

[4]NarasimhamB,BhuvaBL,SchrimpfRD,etal.EffectsofguardbandsandwellcontactsinmitigatinglongSETsinadvancedCMOSprocesses[J].IEEETransactionsonNuclearScience,2008,55(3):1708-1712.

[5]AhlbinJR,AtkinsonNM,GadlageMJ,etal.InfluenceofN-wellcontactareaonthepulsewidthofsingle-eventtransi-

ents[J].IEEETransactionsonNuclearScience,2011,58(6):2585-2591.

[6]AmusanA,WitulskiAF,MassengillLW.Chargecollectionandchargesharingina130nmCMOStechnology[J].IEEETransactionsonNuclearScience,2006,53(6):3253-3258.

[7]JagannathanS,GadlageMJ,BhuvaBL,etal.IndependentmeosurementofSETpulswidthsfromN-HitsandP-Hitsin65-nmCMOS[J].IEEETransactionsonNuclearScience,2010,57(6):3386-3391.

[8]AhlbinJR,MassengillLW,BhuvaBL,etal.Single-eventtransientpulsequenchinginadvancedCMOSlogiccircuits[J].IEEETransactionsonNuclearScience,2009,56(6):3050-3056.

刘蓉容(1986-),女,湖南湘阴人,硕士生,助理工程师,研究方向为微处理器设计和微电子。E-mail:rongrongliu3@126.com

LIURong-rong,bornin1986,MSCandidatassistantengineer,herresearchinterestsincludemicroprocessordesign,andmicroelectronics.

池雅庆(1982-),男,四川雅安人,博士,助理研究员,研究方向为微处理器设计、微电子。E-mail:Yqchi@nudt.edu.cn

CHIYa-qing,bornin1982,PhD,researchassistant,hisresearchinterestsincludemicroprocessordesignandmicroelectronics.

何益百(1986-),男,四川广安人,博士,研究方向为微处理器设计、微电子。E-mail:heyibai@gmail.com

HEYi-bai,bornin1986,PhD,hisresearchinterestsincludemicroprocessordesignandmicroelectronics.