面向安全启动的SPI Flash控制器

2015-12-23吴雪涛戴紫彬张立朝

吴雪涛,戴紫彬,张立朝

(信息工程大学 密码工程学院,河南 郑州450001)

0 引 言

串行接口NOR Flash简称SPI Flash,它具有读取速度快、稳定性高、易用性强等优点,已成为最常见的非易失性存储介质之一[1]。

在以SPI Flash为主要存储载体的SoC设备中需要加入专用的控制器来完成对SPI Flash的多种操作[2]。目前,常见的SPI Flash控制器主要有全硬件和软硬件结合两种实现方式[3,4],文献 [3]采用软硬件结合的实现方式,可操作性强、适用性广泛但是无法支持系统启动;文献 [4]采用全硬件的实现方式,读取速度快、能够支持系统启动,但是在读取过程中无法进行数据加解密操作,因此其中重要数据尤其是启动代码的安全性无法保障。

针对上述情况,为提高系统启动过程和片外存储功能的安全性,本文基于AHB总线协议设计了一款ESSB (encryption storage and security boot)型SPI Flash控制器,在保证其使用效率的同时可支持系统安全启动和加密存储。本文设计的控制器采用缓存结构提高读写速度,提出了一种二次解析方法对SPI Flash的繁杂功能和操作进行优化,提高了可操作性。

1 SPI Flash差异性分析

不同厂商生产的SPI Flash芯片各有特点,为设计具有广泛适用性的控制器,需要研究多种芯片的差异性,找到它们的共同点,并针对适用性较广的结构进行设计,以提高兼容性。

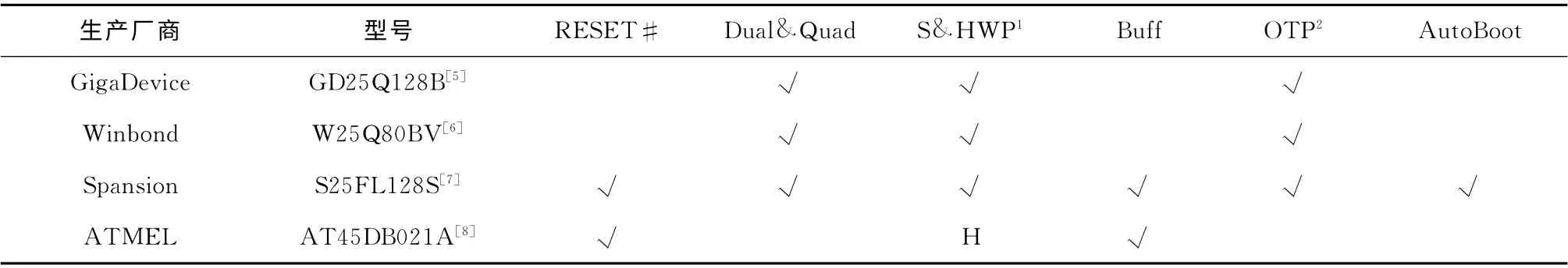

表1 通过对GigaDevice(兆易半导体)、Winbond (华邦电子)、Spansion (飞索半导体)、ATMEL (爱特梅尔半导体)等几大主要SPI Flash厂商生产产品的对比发现了几点不同:①管脚信号数目方面在是否支持Reset#上各有不同;②功能方面在是否支持双端 (dual)和四端 (quad)模式、是否设置了缓存上略有差异,如ATMEL 的双SRAM Buffer结构;③部分芯片还有其特殊功能,如飞索半导体的AutoBoot。但是在主要功能和结构上是具有很多相同点的:操作码 (OP code)基本一致,操作时序基本一致,必要功能均得到很好支持等。除ATMEL 的AT45系列外其余几个厂商所生产的芯片在主要操作上完全相同,如操作代码和操作时序,且他们在功能上除一些附加功能外是通用的,因此就上述通用操作代码集和基本功能设计的控制器是具有广泛适用性的。

表1 主流SPI Flash厂商产品功能对比

据以上分析,本文设计的控制器能够支持读写、快速读写、擦除、安全区域读写等主要功能,兼容两种访问接口,即能够支持RESET#信号的硬件复位功能,其余信号为CS#、SO、WP#、SI、HOLD#、SCLK。对Flash芯片的控制都是通过SI、SO、WP、HOLD这4个控制信号来控制完成的。

2 SPI Flash控制器设计

SPI Flash在SoC设备中主要作为程序存储器,用来存储启动程序、操作系统等代码量不大的固件程序,也可用来存储少量重要数据。针对许多应用场景对系统启动过程的高效性和高安全性要求,本文所设计的SPI Flash控制器加入了Boot Supporter结构,实现了高效的系统启动,同时集成了独立的数据保护电路,保证了启动代码及重要数据的完整性和安全性。

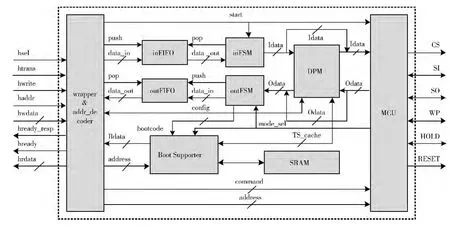

2.1 控制器总体结构

为保证各功能模块的独立性和灵活性,采用模块化设计方法,该控制器整体结构如图1所示。本文设计的ESSB型SPI Flash控制器由以下几个模块组成:接口和地址译码模块 (wrapper &addr_decorder)、输入控制模块 (inFSM)、输出控制模块 (outFSM)、微控制器模块 (MCU)、启动支持模块 (boot supporter)、SRAM、数据保护模块(DPM)和输入输出FIFO 等。

控制器的信号传递过程为:接口和地址译码模块接收AHB总线信号,直接向微控制模块发出操作指令,由输入(输出)FIFO 和控制模块完成数据的传输,传输完成后由控制模块完成串并转换,根据需要对数据进行加解密,生成指令序列,最后由微控制器匹配成SPI Flash芯片所能接受的时序完成相应操作。

图1 SPI Flash控制器结构

2.2 接口和地址译码模块

为了使控制器更好地与总线配合,设计了接口和地址译码模块 (wrapper &addr_decorder)以解析总线时序并处理跨时钟域问题。由于SPI Flash的功能较为繁杂可操作性差,在进行某些操作前还需要几个先行配置操作,为用户的使用带来了极大不便。本文提出了一种二次解析的方法将其优化。wrapper &addr_decorder模块对总线的请求进行先后两次解析才转换为Flash芯片可接受的命令,第一次解析是通过总线信号解析出用户所执行的操作,并自动完成配置操作形成操作流;第二次解析是将此完整的操作流解析为相应指令序列传输给Flash芯片。采用这种方法,用户既无需了解SPI Flash芯片各功能的OP Code也无需了解某项操作所需的配置操作而只需简单地了解一套连续的数值各代表哪种操作即可,提高了使用性。

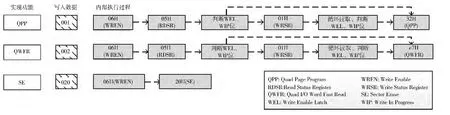

本文设计的控制器在wrapper &addr_decorder模块中设置了一组可直接访问的命令寄存器,总线对命令寄存器写入不同数据将被解析出不同的操作,而后在内部填充好配置操作产生出完整的功能代码传送给Flash芯片,完成相应操作,例如:写入0x001即实现QPP (四端页写)功能,内部将自动依次向SPI Flash芯片输入06H (写使能)、01H (写状态寄存器)指令代码,然后由MCU 自动循环读取状态寄存器的数值直到写入完成,最后输入32H (四端页写)指令代码。本文所使用的OP Code集为上一节分析得出的具有较强普遍性的代码集,为防止出错常用操作的写入数据采用热编码机制。其中QPP、QWFR (四端快速读)、SE (扇区擦除)的OP Code与命令寄存器中输入数据的对应以及它们在Wrapper模块内部的执行过程如图2所示。

图2 命令寄存器功能映射及执行过程

2.3 启动支持模块

由于SPI Flash的读写速度较SRAM 等易失性存储介质慢得多,所以多用于程序的存储而执行一般在SRAM 上完成。为支持系统启动代码的加载和执行过程,本文设计的控制器中加入了Boot Supporter模块,包括Boot Supporter和SRAM。该模块既能很好地支持启动程序的执行过程又能提高启动速度,在非启动应用下作为DPM 模块临时数据的缓存,能够减小硬件开销,提高使用效率。

Boot Supporter与SRAM 共同实现系统的启动功能。由于SPI Flash的一个扇区为4 K 字节,而且一般情况下SoC设备的启动代码不会超过4K 字节,所以将SRAM 的容量设置为4K 字节。Boot Supporter作为启动过程的控制器,既能够模拟SRAM 的时序,完成对SRAM 的读写操作,又能够接受来自MCU 和DPM 的信号实现更复杂的功能。在其内部设置有状态寄存器,为方便读写,设置为32 bit。在系统启动阶段MCU 通过mode_sel信号修改相应的标识位使Boot Supporter模块进入启动模式。在启动模式下,为了完成启动代码的读写,Boot Supporter模块支持AHB总线经wrapper模块对SRAM 中的启动代码进行直接读写;启动过程完成后,model_sel信号使其退出启动模式,为保护SRAM 中缓存的数据不再支持直接读写。在非启动模式下,DPM 模块工作的过程中需要缓存大量的数据,为此特别扩展了其缓存功能,DPM 模块可以直接将需缓存数据经Boot Supporter传输至SRAM 中,此时Boot Supporter的功能简化为SRAM 控制器,在整个SPI Flash控制器内形成一个闭合的独立存储空间,保证了DPM 运行过程中数据的安全性。

2.4 数据保护模块

在安全性需求较高的应用场景下,为保证系统的安全启动,启动代码需要加密存储,因此仅能够完成代码的加载和执行是不够的,还需要通过加密来保证其安全性。

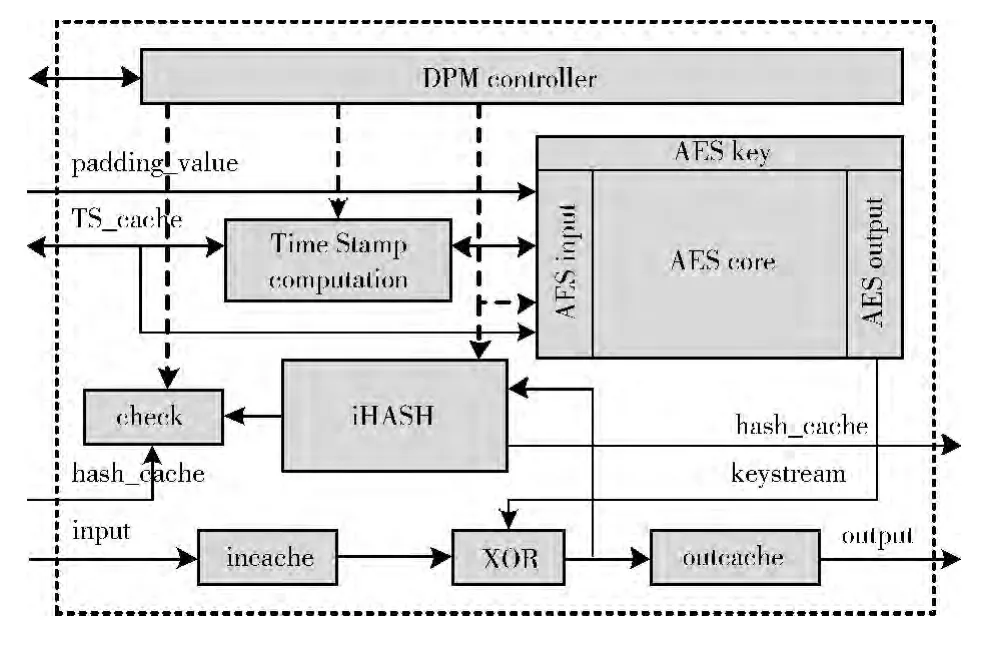

为了对Flash芯片中的数据进行加密存储,本文采用了AES-TAC/iHASH 片外存储安全防护技术[9]作为独立的数据保护模块DPM (data protection module),并针对本文特点加以改进。文献 [9]的设计中为安全合理地保存iHASH 模块产生的标签以及AES-OTP模块所产生的时间标签TS (time stamp)在其结构中加入了标签缓存,这样一来硬件开销会明显增大,本文的设计中由于Boot Supporter模块 (见2.3)的存在很好地解决了这个问题,减小了硬件开销的同时也保证了标签的安全性;在文献 [9]的工作流程中,明文经过iHASH 模块产生的标签也被加密存储在缓存中,在本文的应用中无需将其标签再次加密存储,提高了运行效率。图3为DPM 模块内部的结构。为抵抗窃听攻击且增强灵活性,AES core所需密钥采用外部注入的方式,本文设计的数据保护模块,可抵抗篡改攻击、拷贝攻击、窃取攻击、监听攻击等攻击模型有力地保证了数据的完整性和安全性。

图3 DPM 模块结构

在DPM 模块中设置有配置寄存器和标识寄存器。配置寄存器用来指示当前输入的数据是否需要加密存储功能。配置寄存器的配置由wrapper模块解析特定的命令完成,在数据进入前配置完成,当检测到数据输入完成信号后根据配置寄存器的值完成相应的操作。标志寄存器可被随时读取以了解当前运行状态,设有工作状态、工作模式、iHASH 值生成、完整性检测、密钥注入完成、keystream生成、数据加密、数据解密等标志位以表示响应工作状态。

需要加以说明:在相当多的情况下我们存储的数据并不需要进行加密或是添加杂凑值。为了增强电路的灵活性,使得控制器容易识别出此段代码是否经过了加密处理。本文人为地将整个Flash芯片存储区域划分为两部分,其中一部分用来存储需加密存储的数据,另一部分存储未加密数据。写入时,当写入区域与加密设置不符合时提示错误,读取时根据所读取的区域进行是否进行解密运算。

3 控制器操作流程

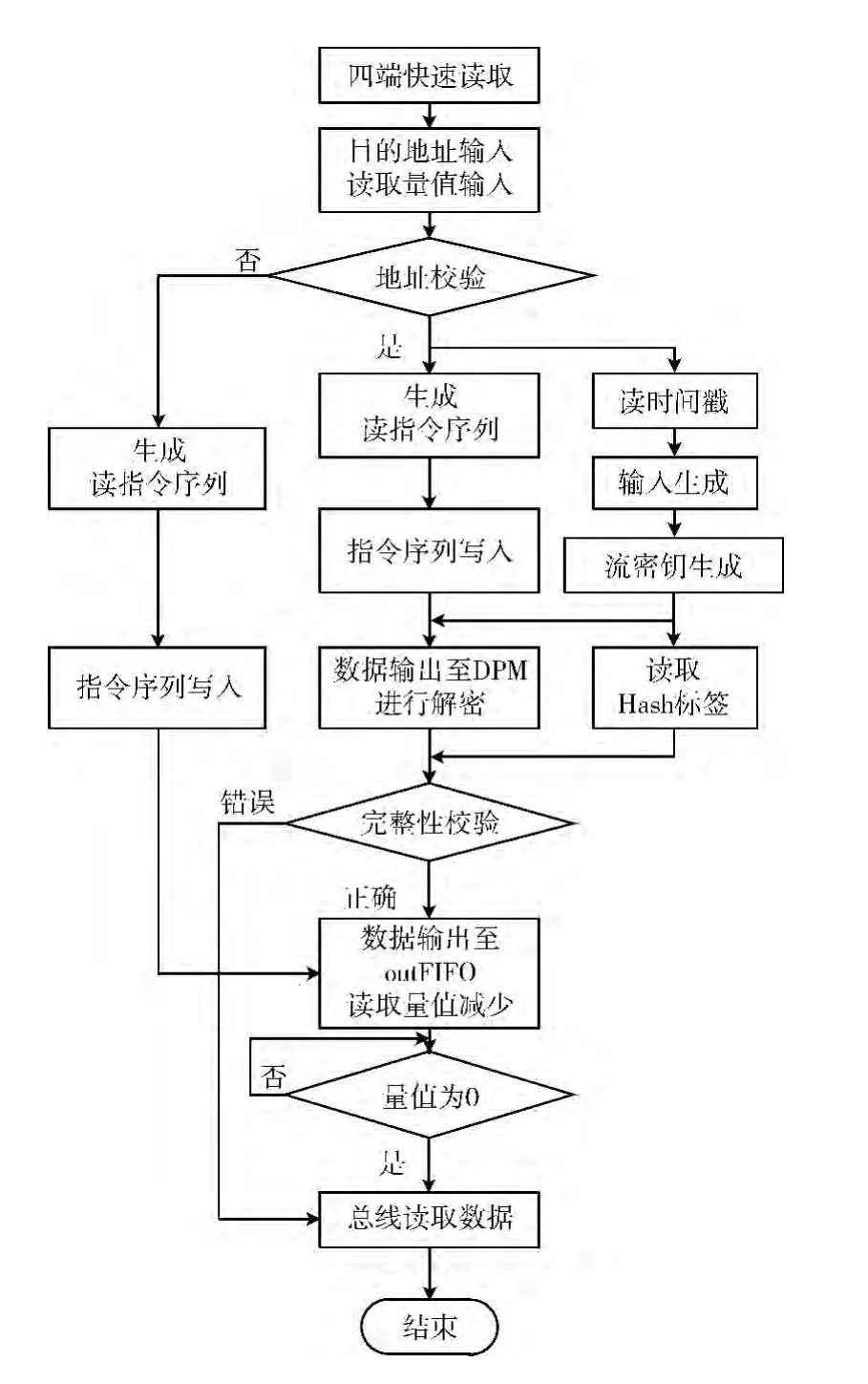

SPI Flash的操作时序较为复杂,本文设计的控制器通过优化使其复杂度大大降低,下面给出其操作流程。图4以四端快速读取操作为例给出了的一般的工作流程。

经优化后的操作流程有较高的一致性,依次可分为4个阶段:输入阶段、校验阶段、序列阶段、接收阶段,不同的操作可能只有其中的几个甚至只有一个阶段。输入阶段需要使用者向命令寄存器输入与操作对应的命令代码、向地址寄存器输入操作执行的地址、向数据端口输入即将操作的数据,不同的操作需输入的内容会有所不同。对于各不同寄存器的输入没有次序要求。校验阶段将对输入的内容进行检查,如果出现错误将向使用者报告并要求重新输入,如果无误将会继续下一步操作。序列阶段将生成能够直接输入至Flash芯片接口的指令序列,如果当前操作涉及数据写入则直到数据准备好即发出start启动信号时,才能生成由命令代码、操作地址、操作数组成的指令序列,如果不涉及数据则可由指令代码和操作地址甚至只有指令代码组成指令序列。接收阶段将由Flash芯片根据请求输出相应的响应,例如读状态寄存器操作的寄存器数值,读操作的读出数据等。

图4 控制器工作流程

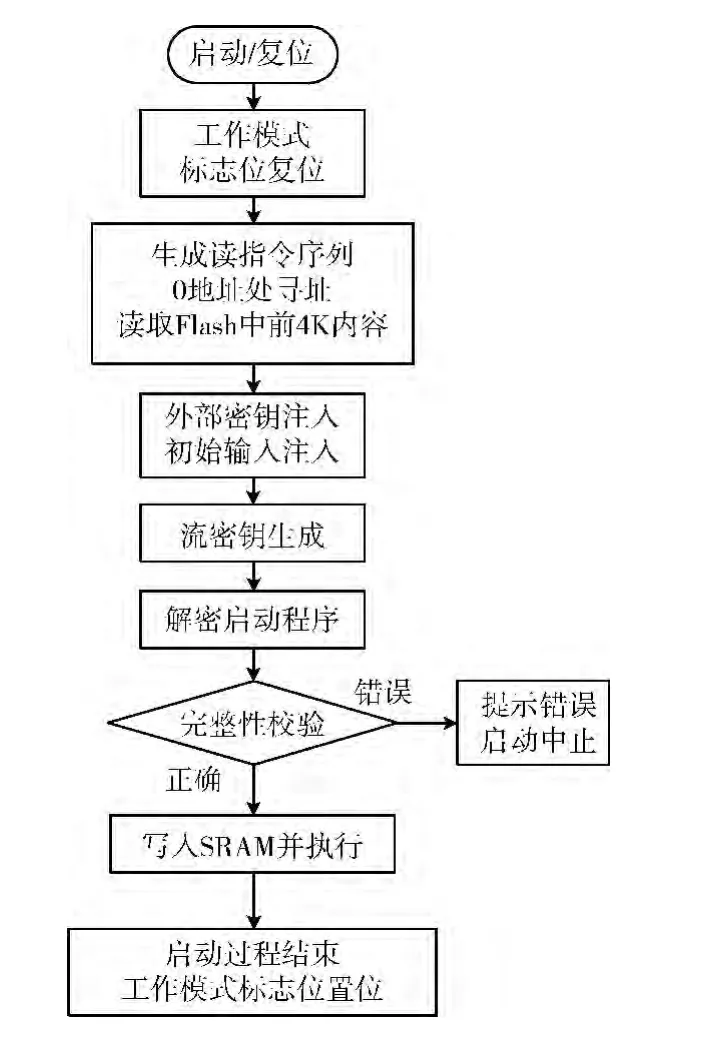

由于启动阶段的操作流程比较特殊,所以在图5单独给出,下面对启动阶段的工作流程做详细介绍。系统上电启动或复位后,MCU 检测到复位信号,自动将操作地址设置为SPI Flash 中的起始地址,生成读指令序列输入至Flash芯片,读出前4K 内容,读取完成后等待外部密钥注入,以此密钥运行数据保护模块进行解密,解密完成后运行完整性校验,期间任何过程未通过则输出提示信息后关闭系统,反之,则运行启动代码。

4 性能参数

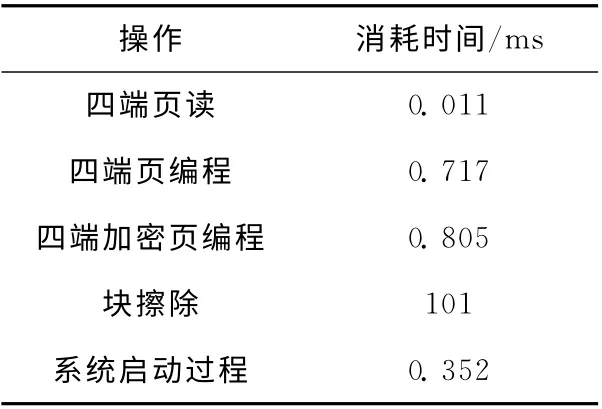

为验证设计的正确性,采用Verilog HDL 语言对本文设计的SPI Flash 控制器编程实现,SPI Flash 芯片选用Giga Device的GD25Q128B,利用Synopsys公司的VCS软件进行功能验证,包括数据加解密和系统启动在内的所有功能均正确无误,在50 MHz时钟下,各主要操作消耗时间情况见表2,与相关设计相比具有较高性能[10]。并利用Design Compiler软件在SMIC 0.18μm 工艺库下进行综合,整个IP核的等效门数为9.78万门。

图5 系统启动工作流程

表2 主要操作时间消耗

在功能验证的基础上搭建了硬件测试平台,采用Altera公司的Stratix Ⅲ系列FPGA 芯片EP3SL150F1152C2N进行了硬件验证,并利用Tektronix公司的TLA5202系列逻辑分析仪得到了Flash芯片接口处实际的信号波形图,确认了其功能的正确性。实验结果表明,本文所设计的结构可以实现安全高效存储,可以较为容易地移植到其它系统中去,可以支持多种SPI Flash芯片,具有普遍适用性。

5 结束语

本文以SPI Flash控制器为研究对象,面向密码SoC的应用场景,采用二次解析的方法对其操作方式进行优化,嵌入Boot Supporter结构和独立的SHA-256和AES算法模块同时保证了数据安全性和完整性,设计了一款可支持启动加载和安全存储的SPI Flash控制器,解决了其写入速度慢、操作繁杂、安全性不足等问题。通过VCS功能仿真和FPGA 板级测试验证了本文设计的可用性,在未增加资源消耗的情况下提高了安全性和高效性,实现了SPI Flash的启动支持和安全存储。本文所设计的控制器为数据的安全存储提供了有力支持,其设计思想、整体结构和操作流程具有一定普遍适用性和参考价值。

[1]Chu CC,Lin YM,Yang CH,et al.A fully parallel BCH codec with double error correcting capability for NOR flash applications [C]//IEEE International Conference on Acoustics,Speech and Signal Processing,2012:1605-1608.

[2]Talole PT,Sawale ST.Performance enhancement by the design of flash controller for x8NAND flash memory devices[J].International Journal of Computer Applications,2010,1 (9):24-29.

[3]CHEN Chaowen,PENG Guojie,WANG Yiwen,et al.Design of NOR flash controller based on PLB general bus [J].Microelectronics &Computer,2014,31 (5):83-86 (in Chinese). [陈超文,彭国杰,王忆文,等.基于PLB 总线的NOR FLASH 控制器设计 [J].微电子学与计算机,2014,31(5):83-86.]

[4]LUO Li,XIA Jun,DENG Yu.Design and verification of general SPI flash controller [J].Computer Engineering,2011,37 (8):22-24 (in Chinese). [罗莉,夏军,邓宇.通用SPI Flash控制器的设计与验证 [J].计算机工程,2011,37 (8):22-24.]

[5]Technical Datasheet.GD25Q128B [S].

[6]Technical Datasheet.W25Q80BV [S].

[7]Technical Datasheet.S25FL128S [S].

[8]Technical Datasheet.AT45DB021A [S].

[9]CAI Luting,XU Jinfu,ZHANG Lichao.Security management of off-chip memory based on AES-TAC/iHASH [J].Computer Engineering and Design,2014,35 (3):841-845(in Chinese). [蔡路亭,徐金甫,张立朝.基于AES-TAC/iHASH 的片外存储器安全防护 [J].计算机工程与设计,2014,35 (3):841-845.]

[10]TIAN Peng,NIE Zedong,ZHANG Zhengping,et al.Design of a nor flash controller IP compatible AHB bus[J].Microelectronics & Computer,2013,30 (6):88-91 (in Chinese).[田鹏,聂泽东,张正平,等.一种兼容AHB总线的Nor Flash控制器IP 设计 [J].微电子学与计算机,2013,30 (6):88-91.]