USB在动态可重构总线测试系统中的设计

2015-12-23陕天龙周继芹王春亮张伟功

陕天龙,周继芹,王春亮,张伟功

(1.首都师范大学 高可靠嵌入式系统技术北京市工程技术研究中心,北京100048;2.首都师范大学信息工程学院,北京100048;3.北京数学与信息交叉科学2011协同创新中心,北京100048)

0 引 言

动态可重构高速串行总线 (UM-BUS)[1]是一种利用多通道冗余实现总线动态容错的新型总线,可实时监测各通道故障,利用多通道冗余实现总线系统的动态容错[2],并通过这些冗余通道的并发传输提高通信速率。同时,UMBUS总线的远程访问存储能力,能够在不改变嵌入式计算机系统逻辑结构的前提下,使各功能模块分布在不同的物理位置,嵌入到测控目标对象中,突破了传统机箱结构的限制。

针对于这种体系结构的UM-BUS总线,为了验证它在总线速率、带宽灵活性、动态容错能力和故障隔离等方面的优势,并帮助对采集后总线数据的处理,加快系统对总线故障通道定位速度,优化冗余容错能力,借鉴总线测试的研究成果[3]提出了UM-BUS测试系统。该测试系统可作为总线测试节点设备,以总线线缆方式接入总线,进而对总线进行测试。

UM-BUS测试系统具体工作时,数据采集模块首先采集总线数据进行缓存,然后将数据传输到PC,进行分析处理后完成无过滤监听、总线状态分析和故障注入等测试功能。UM-BUS是一种高速串行总线,因此UM-BUS测试系统对系统数据有高速性传输要求。基于此要求,并经过综合分析和比较,采用USB3.0技术完成数据采集模块和PC之间通信的设计。

1 UM-BUS测试系统设计

1.1 UM-BUS总线简介

UM-BUS总线采用多线路并发冗余的总线型拓扑结构,如图1所示,它最多可以采用32条通道进行数据的并发传输,能够对最多31 个通道故障进行动态容错。正常通信时,总线控制器会将通信数据包均匀分配到所有通信通道中;如果某些通道出现故障,总线控制器通过实时监测故障,将通信数据包动态均匀地分配到其它健康通道中进行通信,实现对总线通道故障和节点电路故障的动态容错。

图1 UM-BUS总线型拓扑结构

UM-BUS总线采用节点直接互连方式,最多可连接31个总线节点设备,设备间传输采用8b/10b编码,总线具有远程存储访问能力。此外,总线是基于MLVDS (multipoint low voltage differential signaling)信 号 传 输 方 式,单通道速率达到200 Mbps,通信速率最高可达6.4Gbps。

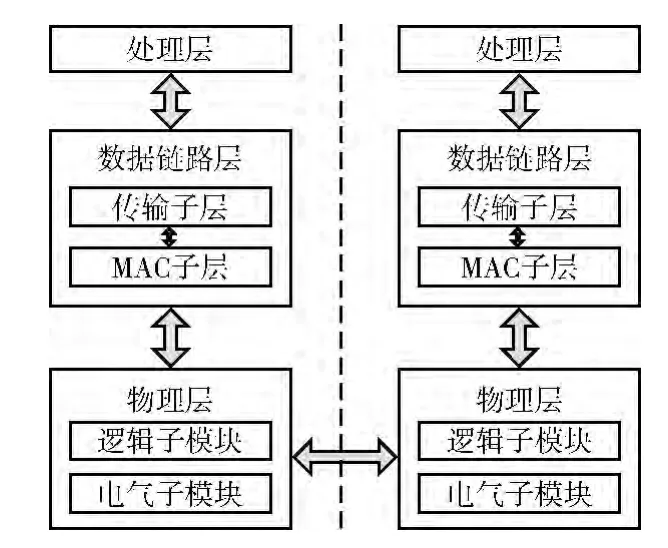

UM-BUS总线通信协议分为处理层、数据链路层和物理层3个层次[4],如图2所示。总线协议模型中,物理层的逻辑子模块实现8b/10b数据编解码、编码差错校验等功能[5],电气子模块规定总线的物理连接特性;数据链路层的传输子层实现数据分组传输,MAC (media access control)子层主要完成通道状态及传输管理;处理层作为总线系统的控制层管理整个总线的通信工作。

图2 UM-BUS总线协议层次结构

1.2 UM-BUS测试系统

1.2.1 测试功能

UM-BUS测试系统能够对总线上的原始数据进行实时采集、检测、处理和记录,可用于UM-BUS总线系统的故障实时分析和事后分析,并可以模拟总线故障,对总线系统中各设备的容错能力进行测试验证。

测试系统主要实现3个功能:无过滤监听、故障注入和总线状态分析。无过滤监听是UM-BUS测试系统采集总线数据包后,将之直接转存到PC中,为软件分析提供数据源;总线状态分析,是实现对被测数字系统的定时采样分析、状态分析及信号质量检测,以及实现对被测系统数据总线的大范围实时监测;故障注入是为了验证总线遇到特定故障时的响应完成情况,是否符合预定设计。

实现总线测试功能的基础是PC 接收并处理UM-BUS总线数据包。总线数据包由总线通道上的数据经过片内总线协议处理生成,根据类型的不同分为长包数据、短包数据、ERR 包数据和MAC 包数据。其中长包和短包是UMBUS总线协议的两种格式,区别在于短包是16字节的命令头,长包由命令头和数据两部分组成。ERR 包数据中记录错误状态等信息,MAC包数据是线路故障信息表数据。

1.2.2 带宽需求

UM-BUS总线采用最多32 条通道进行数据的并发传输,每条通道速率达到200 Mbps。UM-BUS测试系统是针对于8通道的UM-BUS总线进行测试的,当总线采用8通道并发传输时,有效带宽为149.5 MB/s。经过分析和比较,这个速率满足大多数测试和应用的带宽要求,为了将这些高速数据传输到上位机PC进行分析处理,完成总线测试功能,在UM-BUS测试系统中设计并应用了USB3.0[6,7](universal serial bus 3.0)技术。

1.3 CYUSB3014芯片

通用串行总线USB3.0的最大传输速率高达5Gbps,达到了总线测试系统的高速通信要求。USB3.0对USB2.0的向下兼容性和USB 接口在世界范围内的广泛应用,使USB3.0具有通用性的特点。此外,USB3.0的全双工通信保证数据可以同时进行双向传输,它采用的全局性电源管理方案能够提高系统的电源效率。设计选用CYUSB3014[8]芯片作为USB3.0控制器。

CYUSB3014芯片是Cypress公司出品的EZ-USB FX3架构的USB3.0 控制芯片,由通用串行总线集成。CYUSB3014芯片内部主要有以下几部分:

(1)拥有200MHz的ARM926EJ内核,该内核能直接访问16KB指令紧密连接存储器核8KB 数据紧密连接存储器,还为固件调试提供了JTAG 接口。

(2)拥有可编程的100MHz GPIF II接口,支持8位、16位、32位并行数据总线,提供256个可编程状态。应用时根据需求,固件程序[9]利用API库函数对芯片的GIPF II接口进行相应配置。

(3)芯片集成了512KB嵌入式SRAM,以及8KB指令缓存和数据缓存。

(4)拥有连接多种外设模块,如I2C、UART、I2S和SPI,芯片能够在它们之间实现灵活的DMA 连接。

1.4 系统整体设计方案

1.4.1 系统整体结构

UM-BUS测试系统中,系统要求PC 能够对由数据采集模块处理后的总线上的数据进行采集,实现无过滤监听。同时,上位机能够向下位机发送命令,实现故障注入等进一步功能需求。系统整体结构如图3所示。

图3 系统整体结构

系统由以下几部分构成:

(1)UM-BUS数据采集模块。数据采集模块能够采集总线数据,通过总线协议生成总线数据包,实现总线和节点设备间的通信。

(2)USB3.0 控 制 模 块。USB3.0 控 制 模 块 通 过 对USB3.0设备控制器的配置、控制和数据传输,控制读写状态和数据方向,使USB3.0正常通信。

(3)高速缓存控制模块。该模块相当于SDRAM 控制器,它和数据采集模块以及USB3.0 控制模块,三者共同完成测试系统对SDRAM 的控制,实现高速缓存。

(4)USB3.0 设 备 控 制 器:CYUSB3014 芯 片。CYUSB3014芯片作为协处理器,将SDRAM 中的数据通过USB3.0总线传输到PC,实现数据通信。

(5)UM-BUS总线接口,由MLVDS驱动器完成FPGA 和总线间的通信;SDRAM 存储器,作为系统高速缓存;PC模块,它对接收到的总线数据进行分析处理后实现总线测试功能。

整个系统的通信数据为32位,大体数据流程是:数据采集模块首先采集总线数据,将数据存入SDRAM 进行缓存;然后PC向下发出命令,USB3.0控制模块接收到命令后,将SDRAM 中的数据通过USB3.0总线传输到PC中;最后PC对总线数据进行分析和处理,实现各项总线测试功能。

1.4.2 软硬件设计方案

硬件方面,在FPGA 中设计了USB3.0 控制模块和高速缓存控制模块。USB3.0控制模块有USB读写时序控制、数据方向控制、对SDRAM 控制器的控制和故障注入等功能。高速缓存控制模块则设计了一个双口SDRAM 控制器,该控制器的左口被设计为的数据输入口,控制器的右口被设计为的数据输出口,使SDRAM 存储器实现对UM-BUS测试系统的高速数据缓存。

软件方面,利用Cypress公司提供的EZ-USB FX3 完整软件及固件包,将USB应用与内嵌系统环境结合,开发了USB3.0的固件程序,使测试系统完成整体数据通信。另外,为了验证通信数据的高速性和可靠性,根据Cypress公司提供的应用程序接口API函数,设计了PC 应用程序,并完成验证。

2 硬件设计

硬件 部 分 主 要 分 为USB3.0 模 块、FPGA 模 块 和SDRAM 模块,硬件程序均由VHDL 语言编写。其中,SDRAM 模块作为系统的高速缓存,由两片SDRAM 存储器组成,被FPGA 模块控制。下面主要介绍USB3.0 模块和FPGA 模块。

2.1 USB3.0模块设计

USB3.0模块采用CYUSB3014 型号的USB 设 备 控 制器。根据总线测试系统传输要求,将USB 芯片配置为Slave FIFO 模式,此模式下的USB 芯片作为协处理器,FPGA 作为外部控制器。固件程序会将GPIF II接口配置为Slave FIFO 模式的接口,同时FPGA 芯片由硬件程序产生Slave FIFO 模 式 的 时 序,以 保 证FPGA 和CYUSB3014 芯片间的正常通信。

固件程序为CYUSB3014芯片提供了两条DMA[10]通道作为FIFO 缓冲区,采用自动DMA 方式进行数据传输。DMA 通道的软件结构封装了套接口、缓冲区和描述符3个元素。套接口是一种抽象层,PC 应用程序通过它来发送和接收数据。描述符把套接口和缓冲区联系起来,使用户通过寻找套接口使用缓冲区进行数据缓存。

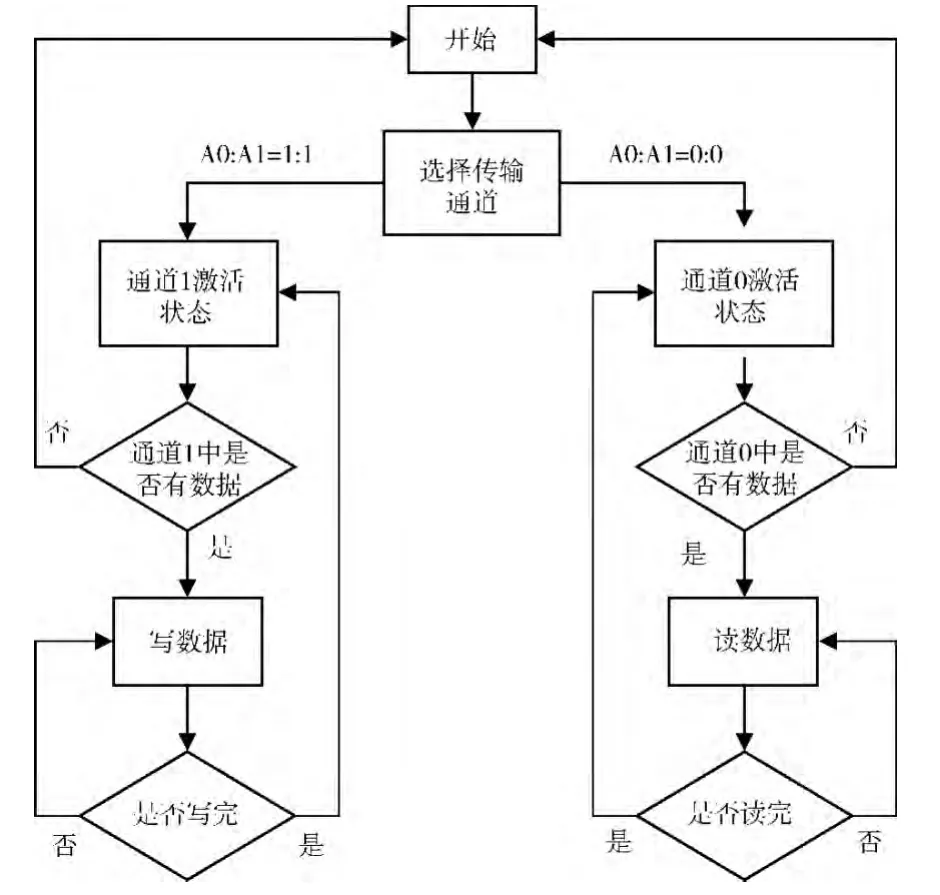

USB3.0模块内部的工作流程如图4所示。硬件程序中的A0和A1接口信号作用是选择USB 芯片中的DMA 通道,另外用FLAGA 和FLAGB接口信号分别表示两个通道缓冲区中是否存在数据。

2.2 FPGA模块设计

UM-BUS测试系统选择Virtex-5 系列的XC5VLX85T型号的FPGA。设计的FPGA 模块,包括USB3.0 控制模块和高速缓存控制模块两部分。USB3.0控制模块独自完成USB读写时序控制逻辑和数据方向控制逻辑,通过对USB设备控制器的配置、控制和数据传输,使USB3.0 进行准确、高速的数据传输;高速缓存控制模块与USB3.0 控制模块两者共同完成SDRAM 存储器控制逻辑,实现了总线数据的高速缓存处理。

图4 USB3.0模块工作流程

2.2.1 USB读写时序控制逻辑

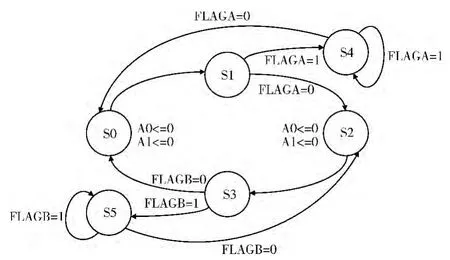

该设计的USB3.0数据传输方式是bulk传输,bulk传输方式支持传输大量数据的高速通信设备。硬件程序控制USB3.0以bulk传输方式读写数据,完成USB读写时序控制逻辑,它的状态机如图5所示。图中S0是判断总线测试系统对USB传输方向需求的状态,S1~S5表示USB 的写数据状态机,S6~S11表示USB的读数据状态机。

实现USB3.0读数据和写数据的双向传输能力,是系统为了完成完整总线测试功能而对USB3.0 控制模块提出的基本要求。USB3.0读取PC 数据时,硬件程序运行读状态机,然后时序信号从USB3.0控制模块传输到USB 芯片的GPIF II接口,USB3.0进入读PC数据状态,USB3.0控制模块接收到通过USB3.0总线传输的PC数据。与之对应的,当系统需要把从USB3.0 控制模块读取的总线数据写入PC时,硬件程序运行写状态机,USB3.0进入写数据状态,PC就能从USB3.0的通道缓冲区中读取数据。

图5 USB读写时序控制状态机

2.2.2 数据方向控制逻辑

PC软件可以把数据方向信息通过USB 芯片上的接口(比如UART)传输给USB3.0控制模块,然后编译成数据方向信号进行方向控制。但为了降低软硬件设计难度和系统复杂性,本文并没有利用PC软件向下位机传输数据方向控制信号,而是根据USB芯片中的DMA 传输机制,通过VHDL硬件语言,在测试系统中设计并应用了一种由USB3.0控制模块自动控制数据方向的方法。

控制数据方向的方法,在于USB3.0 控制模块判断USB的DMA 通道状态后,自动选择通道进行通信。固件程序在USB芯片中通过套接口固化了两条DMA 通道,通道传输的数据方向是:通道0只能从PC读取数据,同时向USB3.0控制模块写入数据;通道1只能从USB3.0控制模块读取数据,同时向上位机PC写入数据。当USB3.0控制模块将A0和A1 信号置于低位时,USB 芯片选择通道0,FLAGA 和FLAGB信号分别表示通道0的空/满状态;当USB3.0控制模块将A0和A1信号置于高位时,USB芯片选择通道1,FLAGA 和FLAGB信号分别表示通道1的空/满状态。

测试系统中USB3.0 负责双向的数据通信。总线数据被USB3.0控制模块传输到USB 芯片的通道1,准备进入PC;同样,PC发出命令后,命令数据被传输到通道0,准备进入USB3.0控制模块。USB3.0控制模块通过判断通道的空/满状态,实时监测哪个通道中有数据,从而判断软件是在读操作还是在写操作,然后产生相应的接口时序,实现读写操作。控制数据方向的状态机如图6 所示,其中S0~S3用于系统循环监控USB 的DMA 通道中数据状态,S4表示USB写数据状态,S5表示USB读数据状态。

图6 数据方向控制状态机

2.2.3 SDRAM 存储器控制逻辑

SDRAM 存储器是UM-BUS测试系统的高速缓存,总线上的数据被数据采集模块完成采集处理后,会生成PC软件需要的长包数据、短包数据、ERR 数据和MAC 数据,SDRAM 存储器控制逻辑负责对这些数据的高速缓存处理。设计的SDRAM 控制器是猝发式数据读写模式,这样有利于高速实时地向SDRAM 读写数据,从而提高整个测试系统的高速性和可靠性。

图7是SDRAM 的控制逻辑框架。高速缓存控制模块是SDRAM 控制器,直接控制SDRAM 进行数据的读取。USB3.0控制模块和UM-BUS数据采集模块,通过控制高速缓存控制模块,间接控制SDRAM,完成存储器地址空间的分配、SDRAM 猝发数据与USB数据的传输时序配合、以及对PC的命令解析等工作,实现测试系统中SDRAM 的具体功能。

图7 SDRAM 的控制逻辑

SDRAM 控制器被设计成一个逻辑上的双口控制器,外部数据从控制器左口进入,最后从控制器右口读出。图8是整个SDRAM 控制逻辑的状态机,其中S0和S2是等待命令状态。S1 表示数据采集模块有存储数据请求时,SDRAM 控制器成为左口模式,数据采集模块产生的数据进入控制器,然后存入SDRAM。S3 表示USB3.0 控制模块有读取数据请求时,SDRAM 控制器成为右口模式,数据从存储器中被控制器读取出后被传输到USB3.0 控制模块。

图8 SDRAM 控制逻辑状态机

3 测试及结果

经过实际测试,USB3.0成功应用在总线测试系统中,如何验证通信数据的高速性和可靠性成为重要问题。为此,该文分别针对USB3.0 带宽测试和数据可靠性测试,分别进行了设计与实现。

3.1 带 宽

3.1.1 带宽测试设计

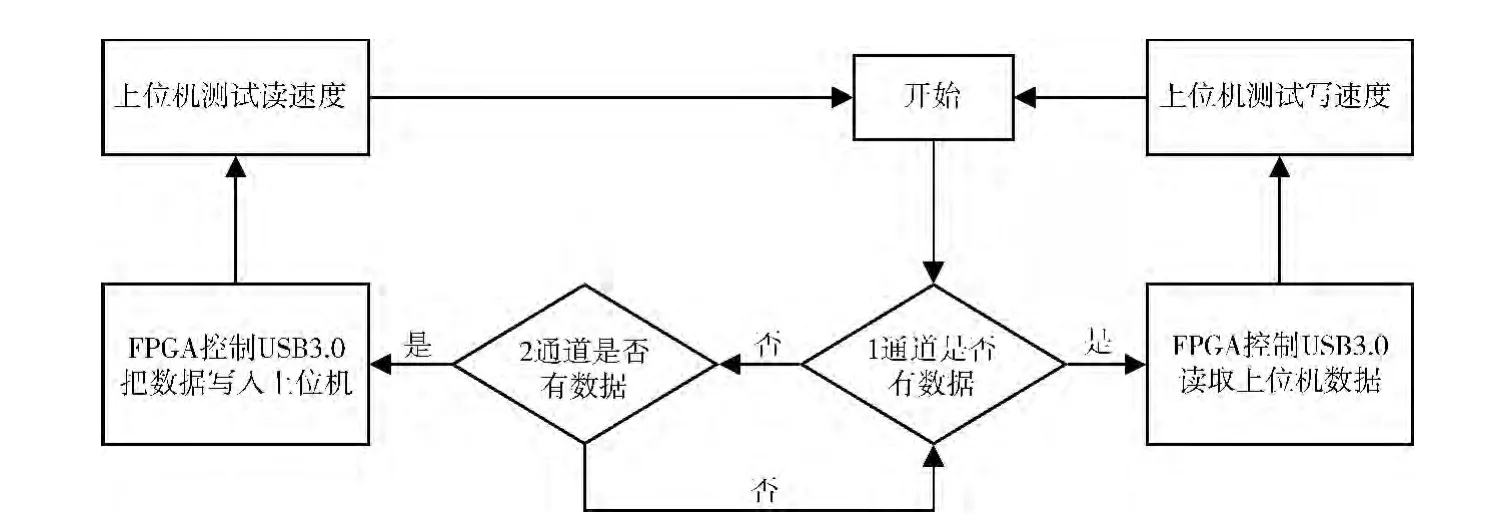

带宽测试设计只是为了验证UM-BUS 测试系统中USB3.0的数据传输高速性,并不实际应用在UM-BUS总线测试系统中。

如图9 所示,FPGA 硬件程序设计了一个循环监测USB芯片缓冲区通道的状态机。当一个通道中有数据时,USB3.0控制模块控制USB3.0进行相应数据方向下的数据操作,PC软件测试数据传输速度。此设计中用于测试写速度的数据由PC软件生成,用于测试读速度的数据由下位机硬件程序产生。

图9 USB3.0带宽测试流程

3.1.2 带宽测试结果

把VHDL硬件程序下载到FPGA 芯片中,为了测试设计中USB3.0的最大数据传输速度,PC 生成大量伪随机数列,通过USB3.0向下位机的USB3.0控制模块持续传输,测试USB3.0最大读速度;相应的,USB3.0控制模块生成大量伪随机数列,通过USB3.0向PC 传输,测试USB3.0最大写速度。经过多次测试,USB3.0的平均读、写速度稳定在180MB/s以上,最大读、写速度均超过190MB/s,达到8通道的总线测试系统的高速数据传输要求。

3.2 数据可靠性

3.2.1 数据可靠性测试设计

数据可靠性测试设计是对总线测试系统中PC、USB、FPGA 和SDRAM 四者间的数据通信可靠性进行整体验证与分析。

如图10所示,PC 软件产生并向USB3.0 发送一个固定大小的测试数据包,该测试数据包经过USB3.0、FPGA和SDRAM 三者的数据传输和处理,最后返回PC进行数据显示和检验,以对系统的数据可靠性进行分析。

图10 系统数据可靠性测试流程

3.2.2 数据可靠性测试结果

PC中软件生成一定大小的32 位伪随机数列,存储到SDRAM 中。存储完毕后再将通信数据读回,软件界面显示读回的数据。通信数据总量不少于50GB,按照字节对比的方式,比较和验证PC生成的和接收的数据,并未发现接收到错误数据。由此推算,应用在UM-BUS测试系统中的USB3.0通信数据误码率低于2*10-8。

验证完伪随机数列数据的可靠性后,PC 软件还会模拟数据采集模块生成的长包、短包等总线数据,分区存储到SDRAM 中后,由软件读回并显示,软件命令格式见表1。同样,经USB3.0传输的总线数据误码率低于2*10-8,数据的可靠性得到了肯定。

表1 软件命令

4 结束语

该文设计了USB3.0 技术在动态可重构总线测试系统中的应用,解决了总线测试系统中USB3.0控制模块和PC间的高速数据传输问题,并完成测试系统中的SDRAM 高速缓存处理。通过软硬件开发对设计进行验证,为实现总线测试做好基础。验证结果表明,Slave FIFO 模式下USB3.0的数据传输速率达到180MB/s,经系统中多个模块处理后的数据可靠性也得到验证,满足总线测试系统对8通道UM-BUS总线进行测试的高速传输要求。

[1]WANG Jiajia.Design and implementation of a dynamically reconfigurable bus controller [D].Beijing:Capital Normal University,2012:1-65 (in Chinese). [王嘉佳.动态可重构总线控制器的设计与实现 [D].北京:首都师范大学,2012:1-65.]

[2]KONG Fanli,HUANG Jinquan.The synchronization techniques for redundancy architecture based on CAN bus [J].Avionics Technology,2013,44 (1):43-47 (in Chinese).[孔凡立,黄金泉.基于CAN 总线的冗余系统同步技术研究[J].航空电子技术,2013,44 (1):43-47.]

[3]LI Xiaoya,SHANG Lina,ZHANG Qinqin.Design and implementation of 1553 bus testing and simulation system [J].Modern Electronics Technique,2012,35 (10):53-60 (in Chinese).[李筱雅,尚丽娜,张芹芹.1553总线测试仿真系统设计与实现 [J].现代电子技术,2012,35 (10):53-60.]

[4]DENG Zhe,ZHANG Weigong,ZHU Xiaoyan,et al.Design and implementation if data transmission management method for dynamic reconfigurable bus [J].Computer Engineering,2013,39 (1):264-269 (in Chinese).[邓哲,张伟功,朱晓燕,等.动态可重构总线数据传输管理方法设计与实现 [J].计算机工程,2013,39 (1):264-269.]

[5]DU Rui,ZHANG Weigong,DENG Zhe,et al.Parallel CRC algorithm design and implementation of new bus [J].Computer Engineering and Design,2013,34 (1):131-135 (in Chinese).[杜瑞,张伟功,邓哲,等.新型总线中并行CRC算法的设计与实现[J].计算机工程与设计,2013,34 (1):131-135.]

[6]GAO Zhenjiang.USB3.0technology [J].Electronic Component &Device Applications,2009,11 (7):77-80 (in Chinese).[高振江.USB3.0通用串行接口技术 [J].电子元器件应用,2009,11 (7):77-80.]

[7]WANG Zhenglin,LIU Jin,XUE Kaifang.Application of USB technology in the system of digital packaging printing machine[J].Microcomputer &Its Applications,2012,31 (20):27-29 (in Chinese).[王政林,刘晋,薛凯方.USB技术在数字包装印刷机系统中的应用 [J].微型机与应用,2012,31(20):27-29.]

[8]XU Yong,QI Xin,TAO Zhiyong.Hardware platform design for GPP software-defined radio system based on USB3.0 [J].Application of Electronic Technique,2013,39 (2):103-106(in Chinese). [徐永,齐心,陶智勇.基于USB3.0的GPP软件无线电系统的硬件平台设计 [J].电子技术应用,2013,39 (2):103-106.]

[9]ZHANG Cong,ZHANG Tao.Firmware design based on peripheral controller of USB3.0 [J].Chinese Journal of Electron Devices,2013,36 (3):383-388 (in Chinese). [张聪,张涛.基于USB3.0 设备控制器的固件设计 [J].电子器件,2013,36 (3):383-388.]

[10]WANG Jialiang,ZHAO Shuguang.PCI-E interface implementation and DMA engine design with FPGA [J].Computer Technology and Development,2011,21 (6):181-184(in Chinese).[王嘉良,赵曙光.用FPGA 实现PCI-E 接口和DMA 控制器设计 [J].计算机技术与发展,2011,21(6):181-184.]