基于FPGA的通信实验箱设计

2015-12-22蔡晨晖林创华

蔡晨晖,林创华

(佛山科学技术学院自动化系,广东佛山528000)

近年来,由于国内FPGA技术发展迅速,所涉及的领域越来越广泛,促使数字电路实验平台的研发也热闹起来。数字电路实验箱是数字电路不可或缺的硬件实验平台,传统的数字电路实验箱一般具有一定的规格,其元器件的数量有限导致可实验种类较少[1],若想完成功能复杂的实验内容,必须借助面包板。当实验电路十分复杂时,就要相应增加面包板使用的数量,这不仅使实验过程变得很繁琐,而且还增加了实验的难度。

FPGA因其现场可编程特性和高速数据处理能力而倍受青睐,加上其程序设计简单,对初学者来说容易上手,把它应用于数字电路实验设备可以很好地弥补传统实验箱的不足[2-5]。笔者设计了一款基于FPGA的通信实验箱,该通信实验箱能够满足多种通信系统实验的教学要求,可实现复杂波形的产生、变换、编码及解码,使学生能够将理论与实践相结合地进行系统学习与研究。

1 实验箱系统总体设计

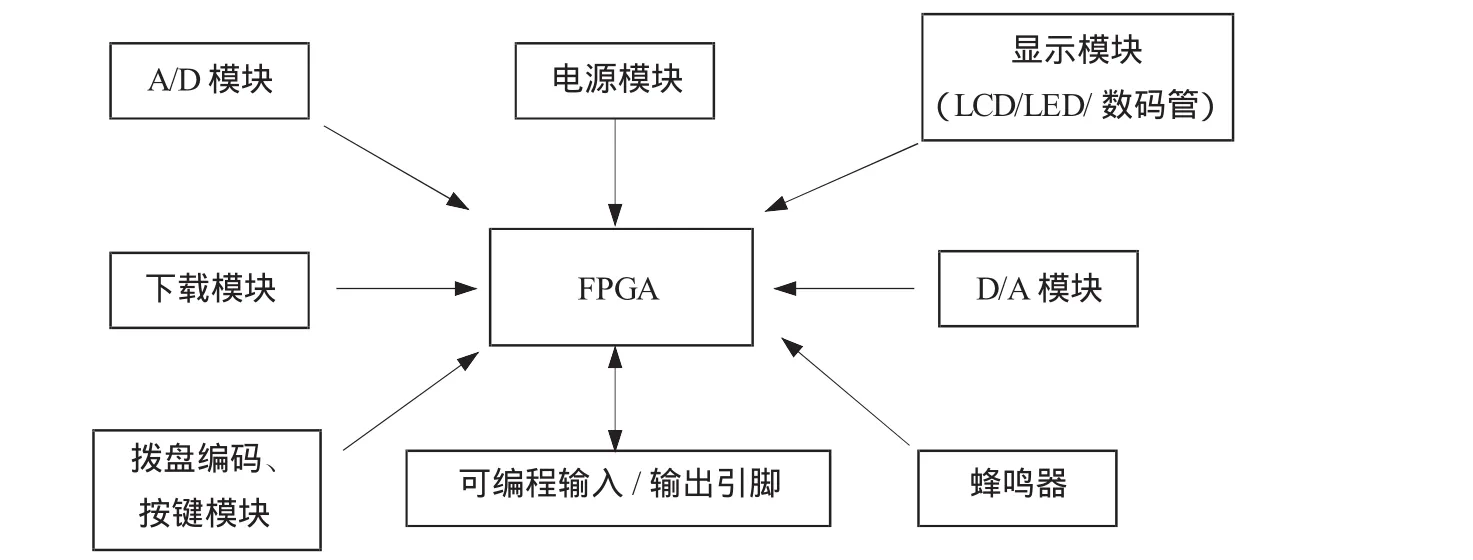

为满足大部分实验的需求,本文所设计的FPGA通信实验箱主要具备以下功能模块[6]。

(1)FPGA芯片模块:成本适中,拥有大量可编程I/O接口,满足百万门运算能力和速率,能完成必要的数字通信运算。

(2)电源模块:为系统芯片及各个部分提供电源,分为1.2 V、3.3 V、5 V与12 V,芯片电源又分内核与I/O。

(3)A/D数据转换模块:负责把输入的模拟信号转换成电平信号,发送到FPGA芯片进行运算处理,然后再发送到D/A数据转换模块。

(4)D/A数据转换模块:把从A/D数据转换模块发送过来的电平信号转换成模拟信号,在时钟控制下进行结果输出,可通过示波器观察。

(5)编程下载口模块:把调试好的程序烧录到FPGA芯片中。

(6)显示模块:利用7段数码管与LCD屏幕实现显示功能。

(7)蜂鸣器:软件模拟报警。

(8)LED灯:设置8个发光二极管,用于显示FPGA控制的信号。

(9)拨码开关:模拟高、低电平的输入。

(10)按键输入模块:模拟复位操作及一些复杂应用中的信号输入。

(11)可编程引脚模块:为系统芯片提供外扩引脚,也可做一些简单应用。

系统的硬件布局如图1所示。

图1 FPGA通信试验箱构成

FPGA芯片采用Cyclone II EP2C8T144,原因是其性价比高、处理数字量大、速度快。芯片共有144个引脚,除去内核与I/O口电源线、地线、时钟线以及锁相环线等54个引脚后,剩下的90个I/O接口可供外界功能设备使用。

2 系统关键技术

2.1 电源系统设计

实验箱系统主要用到+5 V、+3.3 V和+1.2 V这三个等级直流电压,其中5 V电压负责向外围器件供电,3.3 V和1.2 V电压分别为FPGA芯片的I/O口与内核供电。为了让FPGA芯片稳定运行,必须减小其所需的电压纹波。

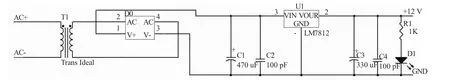

首先要利用LM7812产生12 V通信系统电源,并用LED灯指示是否正在运行,如图2所示。

图2 +12 V供电电路图

220V的交流电通过变压器变压后流入整流桥进行整流,再经由稳压器LM7812稳定输出+12 V电压[7]。为了让电压稳定、纹波减小,增强抗干扰能力,本系统采用一个100 pF的无极性电容和一个470 uF的电解电容对整流桥整流后的电压进行滤波,再利用一个100 pF的无极性电容加一个330 uF的电解电容对稳压三极管输出的+12 V电压进行滤波[8],如图2所示。

对于+5 V的电压,将由+12 V转换电压输入,再经过LM7805低压电源芯片进行电压转换,并通过由陶瓷电容和电解电容组成的滤波电容滤波后,输出+5 V的稳定电压。

3.3 V的稳定直流电压采用LM1117-3.3VLDO电源芯片产生,其最大输出电流为800 mA,供电电路同样增加了滤波电容对输出电压进行滤波。

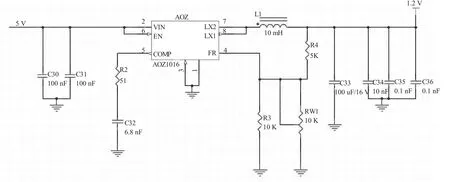

1.2 V的稳定内核电压由AOZ1016开关电源芯片产生,在供电电路中需要注意电阻的搭配,如图3所示。图3中AOZ1016开关电源芯片的输入电压为5 V,在输出口设置了10 mH的电感用作储能,使用5 K与10 K的电阻作为输出电压时的匹配电阻,使输出电压稳定在1.2 V。

图3 +1.2V供电电路图

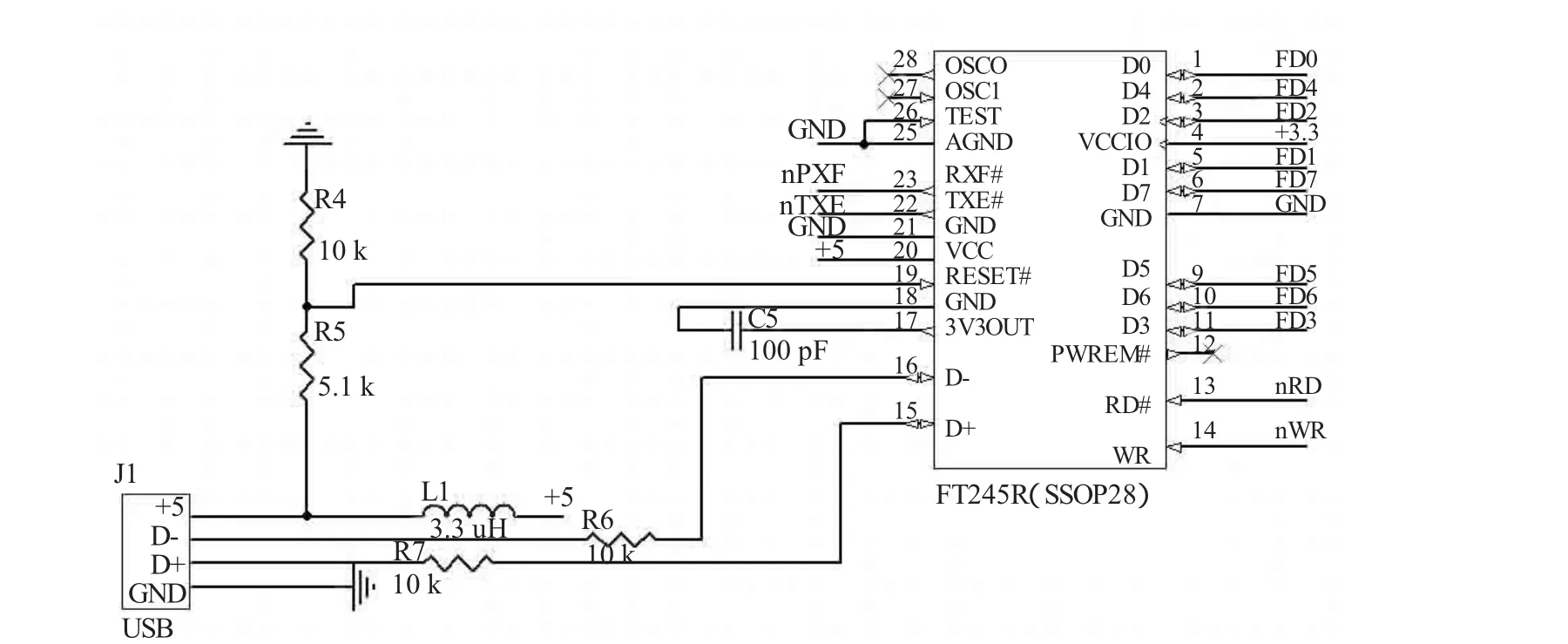

2.2 下载配置工具USB Blaster电路设计

USB-Blaster是通过计算机的USB接口对FPGA以及配置芯片进行编程、调试等操作。首先通过PC端获取5 V电源,采用LM1117-3.3 V稳压芯片转换成3.3 V。另外,连接PC需要用到一块USB转并口芯片,采用FT245RL芯片可实现串并转换,其电路如图4所示[9]。

下载器的控制芯片选用CPLD芯片EPM240T100C5,为了兼容更多型号的FPGA芯片,本实验箱还配置了一块电平缓冲转换芯片MAX3378,它能将USB Blaster的传输电平与目标FPGA实验箱的配置电平进行匹配,防止FPGA芯片遭受过高电平冲击,并通过JTAG接口与目标实验箱的FPGA芯片相连。

图4 USB串并转换电路

2.3 数模、模数转换电路设计

数模、模数转换电路是本系统最关键的部分,也是难点最多的部分,它关系到实验箱的最终实验结果是否稳定,能否实现通信系统的各项功能和波形的平滑变换。

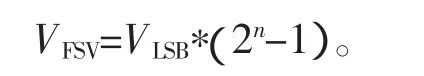

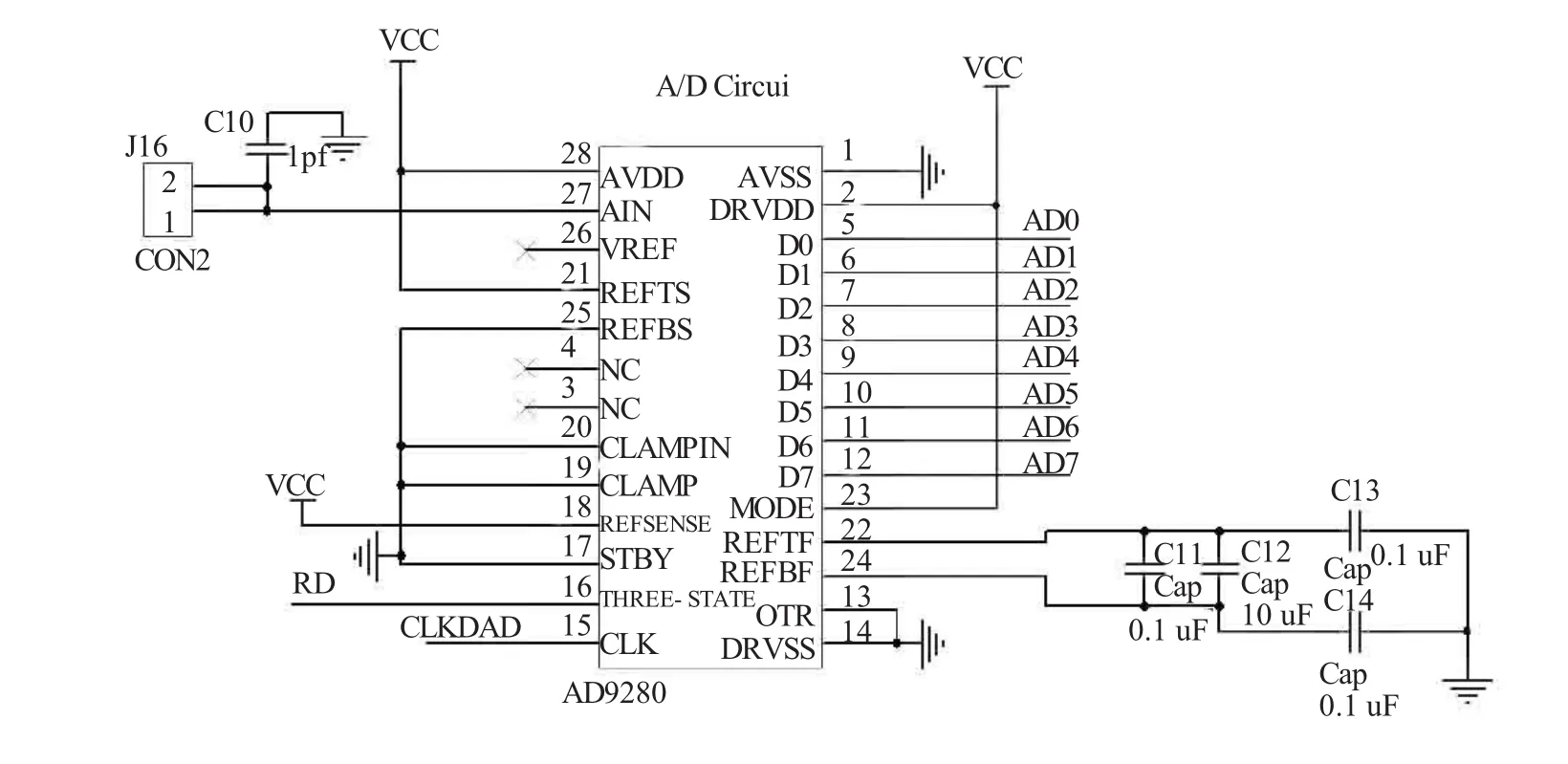

A/D转换器的工作原理是把模拟信号转换成数字信号,一般要经过采样、保持、量化和编码4个步骤。模拟信号具有幅度、时间连续的特点,数字信号则是离散的。D/A转换器的工作原理是把数字信号转换成与之成正比的模拟信号,输出的电压波形是阶梯形而不是连续的,相邻阶梯之间的差值称为最小分辨电压VLSB,满量程输出电压为VFSV,两者的关系为

本系统采用的A/D转换器是基于DAC原理,即发送一个数字信号到D/A转换器上,输出一个与之成正比的模拟电压信号,然后比较输出的模拟电压信号与待转换的模拟电压信号,若不相等,则调整发送的数字信号直至与A/D转换量相同。本文选用的A/D转换芯片是AD9280,它是一款8位单芯片的32MSPS模数转换器(ADC),采用单电源供电,自带一个片内采样保持放大器以及基准电源,为确保输出电压的稳定性,还在芯片内部设计了电压滤波电路,其电路设计如图5所示。

图5 A/D转换电路原理图

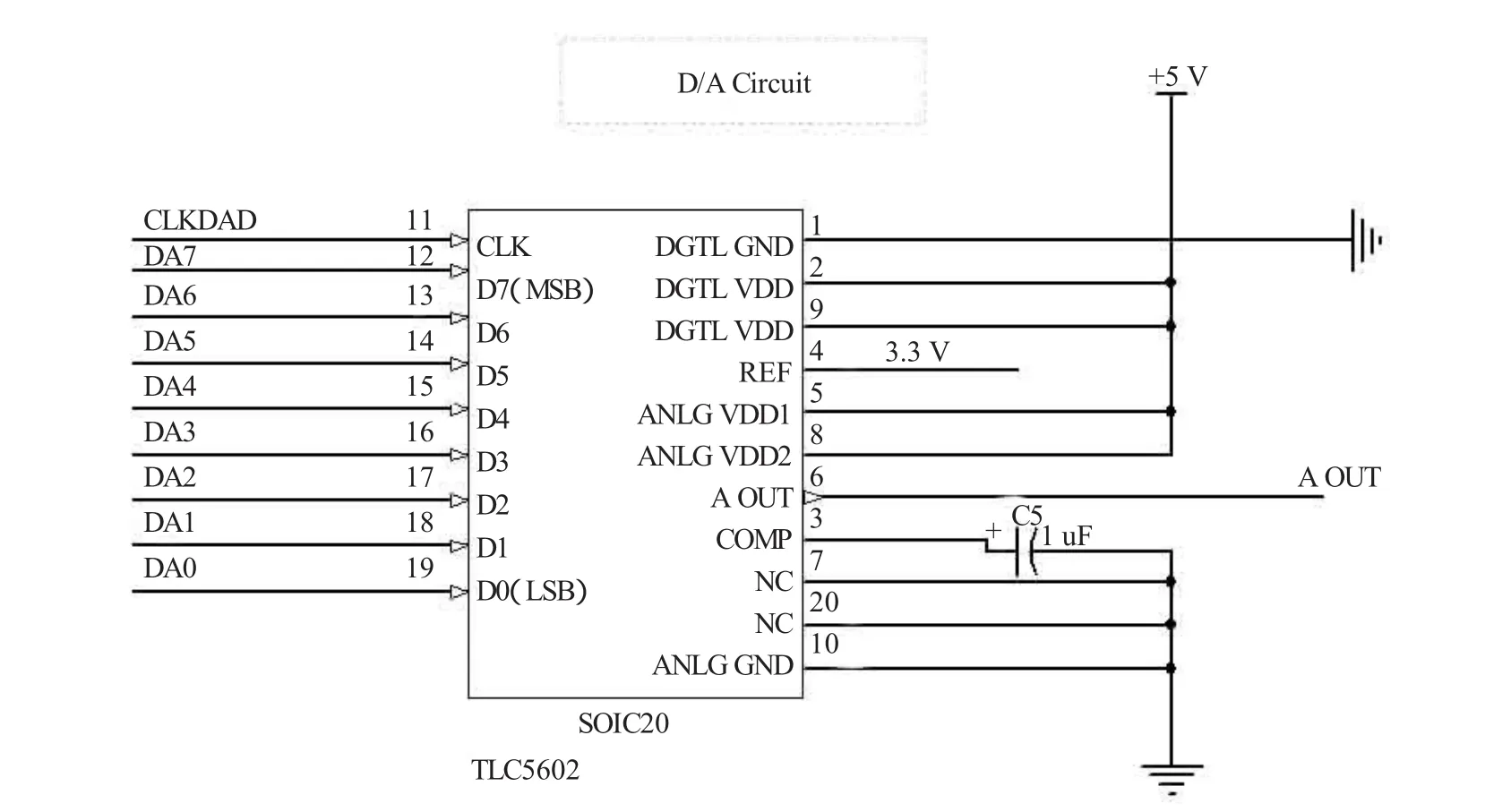

对于D/A转换器,本系统采用TLC5602芯片,该芯片为8位权电流型D/A转换器,低功耗,超高速,最高转换速率可达30 MSPS,它能够消除因模拟开关导通时产生的电阻影响,从而提高D/A转换的精确度,总体上比传统的电阻型转换器要好,其电路设计如图6所示。

图6 D/A转换电路原理图

由于TLC5602输出的是4~5 V电压,要使之变成0~5 V的电压,就要先降压至0~1 V再对其进行放大。降压电路可使用差分放大电路,放大倍数设为5倍,在一端输入4 V电压,另一端输入的是TLC5602的输出电压。待降压放大后,仍需对信号进行滤波,确保输出电压的稳定性,本系统采用的是有源运放二阶RC低通滤波电路,具体方案可查看文献[10],本文不再赘述。

3 小结

针对目前高校课程的实验需求,提出了一款基于FPGA的通信实验箱的设计方案,首先介绍了系统的硬件布局及各个硬件模块的功能,然后分析了电源系统、下载配置工具和数模、模数转换电路等模块的电路设计,为使用FPGA的广大工程技术人员提供了一个设计参考。

[1]覃洪英.数字电路实验中实验平台选择及教学方法改进[J].中国电力教育,2011(34):134-135.

[2]张庆玲.EDA实验开发机设计[J].西安航空技术高等专科学校学报,2005,23(3):59-60.

[3]高立新.FPGA实验开发板的设计与研制[J].安徽电子信息职业技术学院学报,2010,9(5):33-34.

[4]赵刚,何志敏,陈利学.基于FPGA的EDA综合实验系统设计[J].微计算机信息,2012,28(1):49-51.

[5]郑玲玲.天煌教仪系列产品介绍[J].电气电子教学学报,2006,28(3):114-116.

[6]曾志廉,何清平,邹候文.通用FPGA实验系统的设计与应用[J].微计算机信息,2007,23(4):234-235.

[7]纪晓佳.基于EP2C8的FPGA教学实验板设计与实现[D].青岛:山东科技大学,2011.

[8]任加维.FPGA实验系统的改进设计[D].西安:西北大学,2013.

[9]王海杰.基于EP2C8T144C8N的FPGA通信系统实验箱设计与开发[D].杭州:浙江工业大学,2011.

[10]黄训琳.基于FPGA技术的通信实验箱设计与分析[D].杭州:浙江工业大学,2011.