基于FPGA的HDB3编码和解码器的设计与实现

2015-12-20吴光辉殷严刚

吴光辉,殷严刚,姜 愉

(1.广西移动钦州分公司;2.广西师范大学;3.钦州学院)

基于FPGA的HDB3编码和解码器的设计与实现

吴光辉1,殷严刚2,姜 愉3

(1.广西移动钦州分公司;2.广西师范大学;3.钦州学院)

本人通过对HDB3编解码原理进行分析和研究,提出一种基于FPGA的HDB3编解码方法,并通过硬件描述语言构建了其编译码模型,使用EDA 技术实现仿真,验证了其设计的有效性,其功能符合HDB 3编译码的要求。

HDB3编解码;FPGA;Verilog HDL;Quartus II

0 引言

HDB3 码 (high density bipolar),即三阶高密度双极性码,是AMI码 (alternate mark inversion, 双极性传号交替反转码)的改进型。HDB3 码可以由专用集成电路及相应匹配的外围中小规模集成芯片来实现, 但集成程度不高,不易升级和维护,用FPGA 设计HDB3编解码器,能将 HDB3 编解码和通信系统中的其它电路(如复接和分接电路)集成在一个 FPGA芯片上,克服了分立硬件电路带来的抗干扰差和不易调整等缺陷。

(3)为了使脉冲序列仍不含直流分量,则必须使相邻的破坏点 V脉冲极性交替。

(4)为了保证前面两条件成立,必须使相邻的破坏点之间有奇数个“ 1” 码。 如果原序列中破坏点之间的“ 1” 码为偶数,则必须补为奇数,即将破坏节中的第一个“ 0” 码变为“ 1” ,用 B脉冲表示。 这时破坏节变为“ B00V” 形式。 B脉冲极性与前一“ 1” 脉冲极性相反,而 B脉冲极性和 V脉冲极性相同。

1.2 HDB3码译码

1 HDB3码编译码原理

1.1 HDB3码编码

HDB3 码是一种 AMI 码的改进型,它的编码原理可简述为,在消息的二进制代码序列中:

(1)当连“ 0” 码的个数不大于 3 时,HDB3 编码规律与AMI 码相同,即“ 1” 码变为“ +1”、“ - 1” 交替脉冲。

(2)当代码序列中出现4个连“ 0” 码或超过4个连“ 0”码时,把连“ 0” 段按 4 个“ 0” 分节,即“0000” ,并使第 4 个“ 0”码变为“ 1”码,用 V脉冲表示。这样可以消除长连“ 0” 现象。为了便于识别V脉冲,使 V脉冲极性与前一个“ 1” 脉冲极性相同。这样就破坏了 AMI 码极性交替的规律,所以 V 脉冲为破坏脉冲,把 V 脉冲和前 3 个连“ 0” 称为破坏节“ 000V” 。

虽然 HDB3 码的编码规则比较复杂,但译码却比较简单。从上述原理看出: 每一个破坏符号 V总是与前一非 0 符号同极性(包括 B在内)。 这就是说,从收到的符号序列中可以容易地找到破坏点 V, 于是也断定 V符号及其前面的 3 个符号必是连0 符号,从而恢复 4 个连 0 码,再将所有- 1 变成+1 后便得到原消息代码。

2 HDB3码编码模块设计

其编码过程 :首先插入V码 ,然后插入B码,最后是单双极性变换。如果按照编码规则的顺序设计,应该首先进行单双极性变换在完成插 V 和插 B 后,还需根据编码规则变换当前 B 码之后的非零码的极性,这需要大量的寄存器来保存当前数据的状态.导致电路非常复杂占用大量的FPGA内部逻辑单元 实现难度大 且成本高.

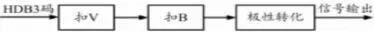

图1 HDB3码编码模块设计框图

2.1 插V过程

V码产生单元的功能实际上就是对消息代码里的四连0串的检测,当出现四个连0串的时候,把第四个0码变换成V码,而在其他情况下,则保持消息代码的原样输出。为了为以后的编码过程提供方便,将原信号中的一位码元用2位二进制传输码表示,在进行加V码时,同一用“11”标识之,原l码用“01”标识,0码用“00”标识。输入的代码经插V操作后全部转换成了双相码。

2.2 插B过程

B码产生单元的功能是保证附加V码后的序列不破坏“极性交替反转”形成的无直流特性,当相邻两个V码之间有偶数个非0码时,则把后一个V码之前的第1个非0码后面的0码变换成B码。

2.3 单双极性变换

根据HDB3的编码规则,我们可以知道,V码的极性是正负交替的,余下的1码和B码看成为一体且是正负交替的,同时满足V码的极性与前面的非零码极性一致。由此我们可以将其分别进行极性变换来实现。

3 HDB3码译码模块设计

每一个破坏符号V 总是与前一非0 符号同极性,从收到的符号序列中可以容易地找到破坏点V,于是也断定V 符号及其前面的3 个符号必是连0 符号,从而恢复4 个连0 码,再将所有-1,+1 变成1后便得到原消息代码。根据以上解码原理HDB3 的解码步骤可分为三步:(1) 扣 V;(2) 扣 B; (3)极性转换HDB3解码模块的设计框图如图2

图2 HDB3码解码模块设计框图

3.1 扣V过程

即检测信号中的 10001 或-1000-1 串,如果检测到 则把10001 或-1000-1 变为 10000 或-10000。具体操作是:我们定义一个10位寄存器 dffa [9:0] 用它来检测信号中的 “10001”或“-1000-1” 一旦检测到将他们的值分别变为“10000”或“-10000”

3.2 扣B码过程

即检测信号中的 1001 或-100-1 串,若检测到则把 1001或-100-1 变为 0000,

具体操作是:我们定义一个8位寄存器 dffb[7:0] 用这个寄存器来检测 “1001“或 “-100-1”一旦检测到 将他们的值都变为“0000”

3.3 极性转换

由于前面来的信号中有 01 和11 即 +1 和 -1 而实际情况是数字电路中只有0 和 1 所以要进行极性转换把双极性信号变为单极性信号使信号中只含有 0 和 1。算法为:如果输入的是00,则输出0。否则输出1。

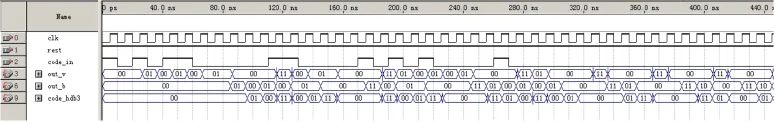

图3 编码模块波形仿真图

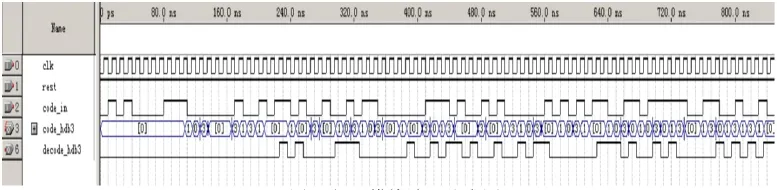

图4 解码模块波形仿真图

4 仿真分析

利用ALTERA 公司的Quartus II 开发软件实现具体设计,其主要步骤如下: 在QII中建立工程,及Verilog HDL.v源文件,输入代码后进行编译。然后再建立波形仿真文件对实验结果进行仿真。仿真正确后可进行引脚绑定,同过下载器烧写到FPGA芯片中观察实验效果。

4.1 编码模块仿真分析

对HDB3编码模块进行仿真验证,图3是仿真波形图。输入的二进制代码为 1010110000011000010101000010000000 000000 ,Code_in是二进制代码信息输入。下面进行输出的分析。

out_v是插v之后的输出。out_b是插入b之后的输出。Code_hdb3码是经过极性变换后的HDB3码输出,从图中可以看出:“01”为正电平,“11”为负电平,“00”为0电平,从波形可看出1和b码实现了正负电平交替,而v码与前面的最近的非零码极性相同。符合HDB3编码规则。

4.2 解码模块仿真分析

图4中code_in是一串伪随机序列二进制码,在经过编码模块编码后输出,code_hdb3即为HDB3码输出,然后再经过解码模块得到解码输出,decode_hdb3即为解码后的输出。从图中可以看出,输出波形与输入波形完全相同。

5 结论

本文所设计的HDB3 编解码模块简单实用,利用FPGA 实现HDB3 编解码功能具有很强的灵活性 可以集成到不同的通信系统中 提高系统设计的速度。本文提供了一种利用现代EDA技术,以ACEX系列FPGA芯片EPlK30为硬件平台,以Quartus II为软件平台,以Verilog HDL,为开发工具,适合于FPGA实现的HDB3编译码器的设计方案。并从整个从NRZ 码到HDB3码的编码过程以及解码过程作了一个详细的分析。且实验结果符合预期, 有很好的应用远景。

[1] 韩德红,孙筱萌,张显才. 基于FPGA的HDB3编解码器的设计与实现. 空 军雷达学院学报.2010.8第24卷第4期

[2] 吴海涛,陈英俊, 梁迎春. 基于FPGA的HDB3编解码器设计.微计算机信息, 2008 , 24( 6 2) : 236 – 238

[3] 段吉海 黄智伟.基于 CPLD/FPGA 的数字通信系统建模与设计[M].北京 电子工业出版社 2004

[4] 朱勤为,唐 宁,赵明剑. 利用FPGA 实现HDB3编解码功能.电子设计工程2009 年 12 月

[5] 基于EDA技术的HDB3编码器的设计与实现 中国百科网

The Design and Realization of HDB3 encoder and decoder based on FPGA

Wu Guanghui1,Yin Yangang2,Jiang Yu3

(1.Guangxi mobile Qinzhou branch;2.Guangxi Normal University;3.Qinzhou University)

I analysis and study of the principles of HDB3 code,propose a method of HDB3 codec based on FPGA.And Through hardware description language to build the model of codec.Using EDA technology to realize the simulation,I Verify the effectiveness of the design. Its features correspond HDB3 codec requirements

HDB3 code;FPGA;Verilog HDL;Quartus II