一种输入输出轨到轨CMOS运算放大器的设计

2015-12-20李有慧

李有慧

(无锡华润上华科技有限公司上海分公司,上海 201103)

轨到轨放大器是一种特殊类型的放大器,其共模电压范围可以从正电源电压到负电源电压[1]。轨到轨放大器应用范围广泛,尤其在电源电压日益降低的情况下。通常信号幅度会随着电源电压的降低而减小,在这种情况下,噪声对电路的影响会明显增大,信噪比则明显减小。使用轨到轨放大器,可获得最大的信号摆幅,使噪声对电路性能的影响降低。

实现轨到轨的方法之一是使用耗尽型器件。由于采用了离子注入技术,耗尽型器件的阈值电压可以是负值,尽管这种技术使得轨到轨输入级的电源电压可降低至1 V,但由于标准CMOS技术不支持耗尽型晶体管,因此这种方法在CMOS工艺中基本不被采用。

放大器的输出端易实现轨到轨,只需将两个输出晶体管的漏极相连,输出加容性负载,即可实现输出的轨到轨。但在输入端实现轨到轨则较复杂。原则上只能是折叠式共源共栅结构才能使输入端包含电源电压的轨。这种技术是实现所有轨到轨输入放大器的基础。

文中探讨了一种两级恒跨导的轨到轨CMOS运算放大器,由轨到轨恒定跨导输入级、求和电路及AB类输出级构成。为减小芯片面积、噪声和失调,将AB类输出级控制部分嵌入到折叠共源共栅求和电路中。与其他输入输出轨到轨运算放大器相比,由于其电路结构简单、紧凑、芯片面积小、性能高,所以可广泛应用于VLSI的设计中。采用CSMC 0.18μm工艺模型进行仿真并流片验证。

1 理论分析

1.1 输入级

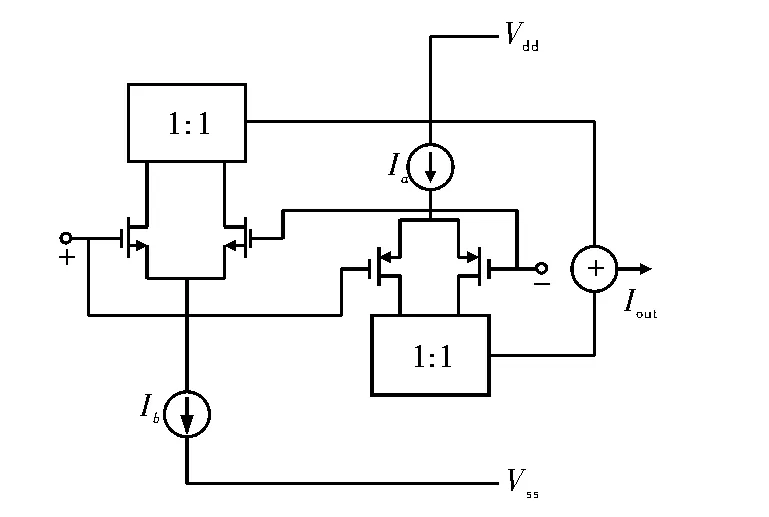

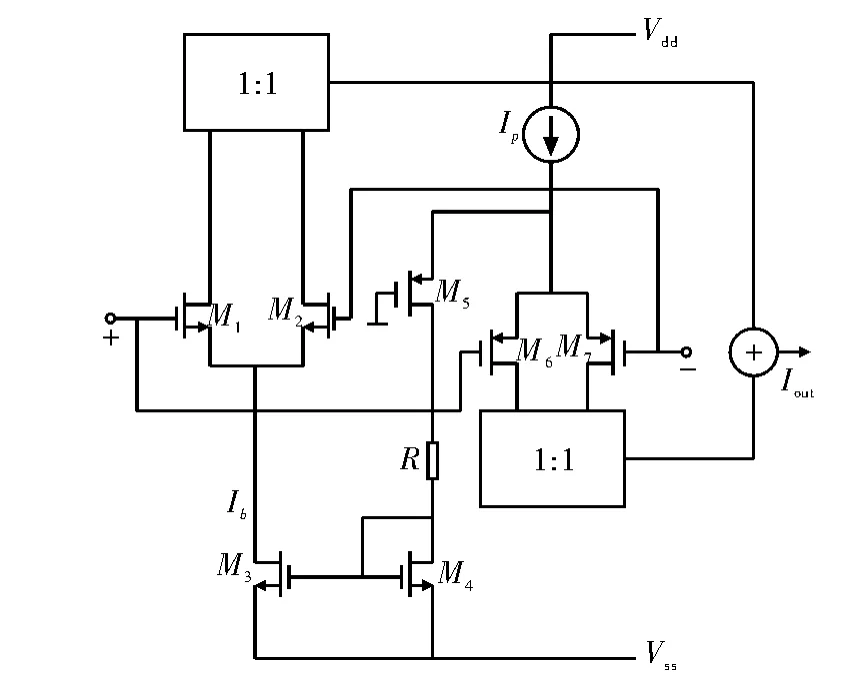

共模输入范围超过或至少包含两个电源电压轨需要输入级是NMOS和PMOS差分对并联。图1给出了一个这样的输入级,这级电路有两个不希望产生的特性[2]。

图1 轨到轨共模电压范围的输入级

(1)若输入对中的一对关掉了,输入电压失调会发生变化,这发生在狭窄的共模输入电压范围内。对这些接近轨的关断区域中,式(1)可用于近似共模抑止比(CMRR)

其中,Vic是共模输入输入电压;Vos是放大器的失调。对文献[3~4]所报告的轨到轨输入电路,式(1)给出了较低的共模抑止比(30~40 dB)。

(2)这级电路的跨导不恒定,不利于最优的频率补偿,且影响谐波总失真(THD)性能。文献[5]中给出的电路,如图2所示。解决了第2个问题,但若应用于CMOS电路,仍会有较差的CMRR特性,因电流在窄的共模输入信号范围内从一对切换到另一对。

图2 带恒流偏置的轨到轨共模电压范围的输入级

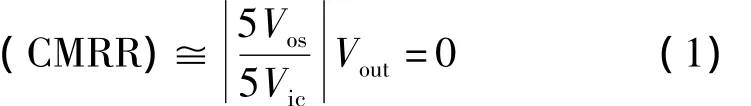

这一问题在图3所示的输入级中得到了解决。电阻R和M5所拉出来的电流基本正比于共模输入电压,因此将电流IP在两对输入对中进行分配。当共模输入电压变化时,一对的尾电流逐渐增加,另一对的尾电流逐渐减小。结果,失调电压渐进地变化,这样就提高了CMRR。在一个5 V设计中与原有的解决方案相比,通常CMRR可有20 dB的增加。来自负电源的电源抑止比(PSRR-)不会降低,因此M4-R-M5的通道只影响信号的共模部分。

无论两对输入对是工作在弱或中度反型区,均可获得近似恒定的跨导,因电流镜M3和M4使得尾电流的和保持恒定。M5在较低的输入共模信号下,有助于保持尾电流的和是个常数。其作用类似于电平位移器只有当M3饱和时才会迫使电流流入M4。

工作在弱反型区时n通道和p通道的斜率系数之间的差异[6]会影响跨导的和。这种影响可以通过选择合理的电流镜的比例来抵消。设计的运算放大器电路的输入级采用了图3所示的结构。

图3 改善后CMRR的轨到轨共模输入电压的输入级

1.2 电流求和电路

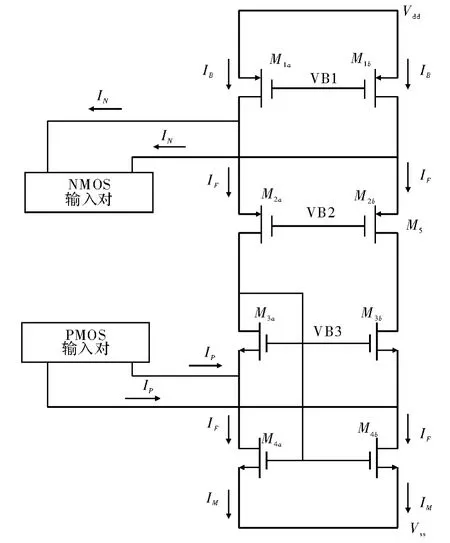

轨到轨运算放大器另一个重要模块是电流求和电路[7]。实现电流求和电路的传统方法如图4所示,此方法会导致零极点位置及低频增益的剧烈变化,不利于频率补偿。

图4 传统求和电路

如图4所示,M1a和M1b的偏置电流IB除了要为NMOS输入差分对提供电流IN外,还需提供偏置电流IF。因输入级NMOS差分对的电流随着共模电压VCM的变化而变化,其值可从0变化到2IN以上,其中IN为NMOS差分对在共模电压中间时的值。所以,晶体管M1a和M1b的偏置电流要能为NMOS差分对提供这样的电流增量还要为电流求和电路提供最小的静态电流。

另一方面,当共模输入电压为中间值或负电源电压时,M1a和M1b中额外部分的偏置电流将流过晶体管M2a和M2b,因此改变了这些晶体管的静态偏置电流,从而改变了其的跨导和输出阻抗。这些变化将导致运算放大器零极点位置以及低频增益的变化。为了优化运算放大器的低频增益、频率补偿、功耗及谐波失真,稳定这些晶体管的静态电流很重要。

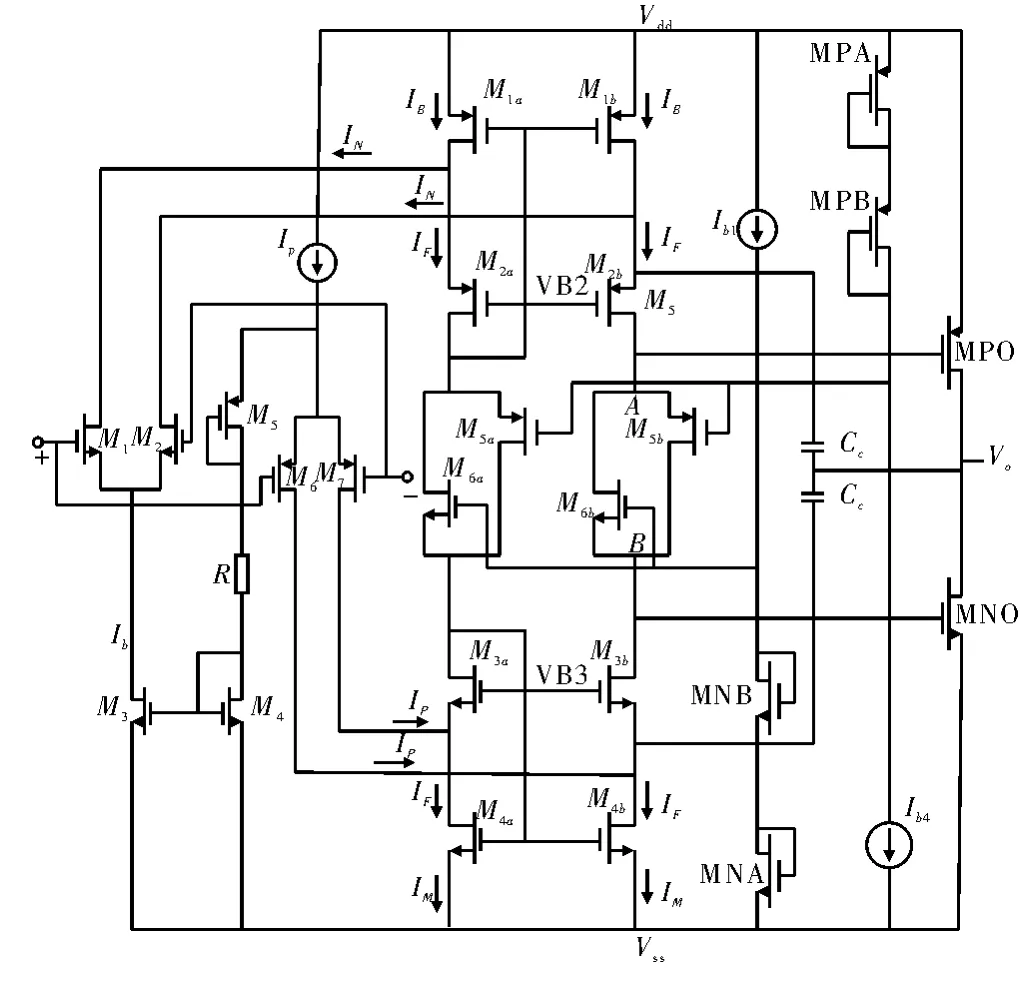

文中采用了浮栅电压源[8]来稳定求和电路中的静态电流,即在晶体管M2b和M3b的漏极之间插入浮栅电压源M5b和M6b,具体实现在图5运算放大器主体电路中给出。

图5 运算放大器主体电路

直流电流流过M5b和M6b,但没有交流电流从中通过,其屏蔽了交流行为,对来自第一级的电流表现为一个无穷大的交流阻抗。

1.3 输出级

在运算放大器输出级的设计中,为了提高效率,输出级必须要有大的摆幅和尽可能小的静态电流。共源极AB类输出级就具有这样的特点。

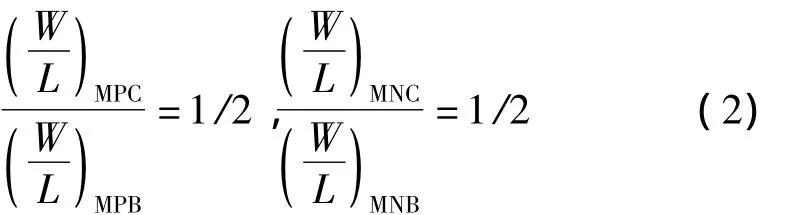

AB类输出级在没有输出电流时,输出晶体管被偏置在一个相对较小的静态电流下,有效地减小了交越失真[9],同时也可保证最大动态输出电流远大于静态电流,从而提高输出级的效率。AB类输出级的关键在于保持两个输出晶体管栅极间电压的恒定。如图6所示,在此的AB类控制采用两个浮栅MNC和MPC,相对于使用电阻,可有效减小芯片面积。AB类浮栅控制形成两个跨导线性环 MPA、MPB、MPC和 MPO以及MNA、MNB、MNC和MNO,确定了两输出管的静态电流,固定了两输出管MPO和MNO栅源之间的电压。

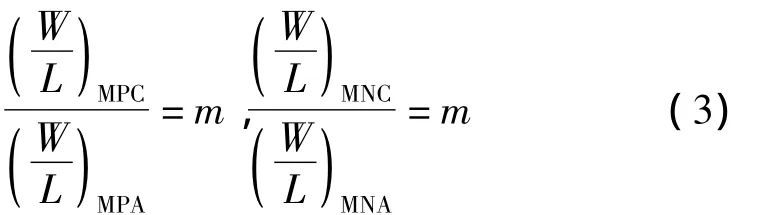

AB类输出级的具体原理如下:Iin1和Iin2为两个同相位的交流小信号电流源,设Ib1=Ib2=Ib3=Ib4=I;Iin1=0,Iin2=0。MPA、MPB和MPC构成了MPO的偏置电路,MNA、MNB和MNC构成了MNO的偏置电路,分别决定了MPO和MNO的静态偏置电流。设

因此,MPB和MPC,MPA和MPO同为一个栅源电压;同理,MNB和MNC,MNA和MNO也同为一个栅源电压,若 Ids,MPO=mI,Ids,MNO=mI;则

各管的宽长比还应满足如下要求

因A、B间可视为一个浮动电压源,交流小信号下可视为短路,即VA=VB。于是有如下两种情况:

(1)当Iin1=Iin2>0时(流入节点A和B),节点A和B电压将升高,最终MPO截止、MNO导通,VA=VB=VDD。

(2)当Iin1=Iin2<0时,MPO 导通、MNO 截止,VA=VB=0,从而实现轨到轨的大动态输出。

采用这种结构,当一个输出管的电流较大时,另一个输出管的电流能保持一个最小值Imin。该Imin可防止MOS管进入截止状态。只要MOS管不进入截止状态,就不会产生开关延迟和交越失真。

传统的米勒补偿要求在输出管的栅漏两端分别接入两个补偿电容。由于电容的前馈通路,米勒补偿引入了一个相平面右侧的零点,该零点减小了相位裕度,限制了单位增益带宽。

本文通过共源共栅补偿来消除这个零点,用较小的补偿电容就实现了频率补偿,获得了较高的单位增益带宽[10]。

2 仿真分析

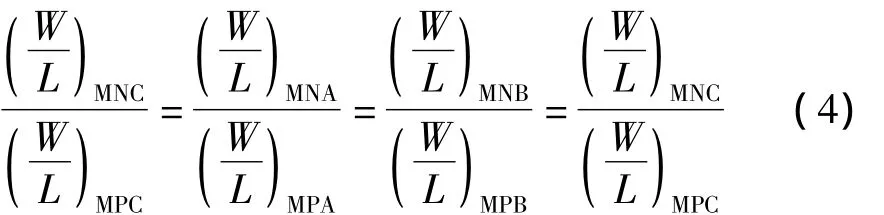

图7是输入级的总跨导gmtot随共模输入电压变化的仿真结果。横轴是输入共模电压,纵轴是输入级的总跨导,单位S。

图7 输入g mtot随共模输入电压的变化

在本文的设计中,共模输入电压从地变化到电源电压,输入gm的变化仅为5.5%。

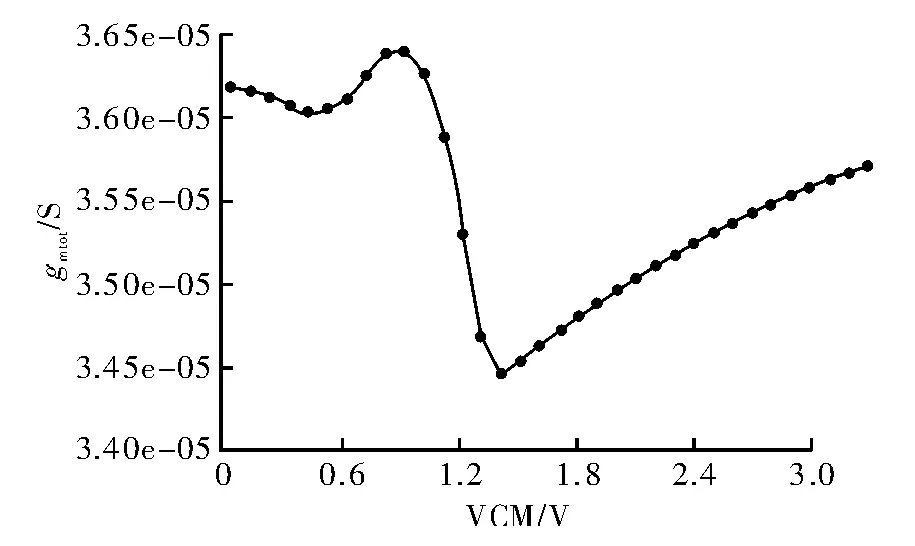

图8是运算放大器在电源电压为3.3 V,共模输入电压为1.65 V,负载电阻为10 kΩ,负载电容为10 pF,补偿电容为1.8 pF时的开环频率特性。仿真结果表明低频增益约为107 dB,相位裕度约为61°,单位增益带宽约为4.5 MHz。

图8 运放开环幅频和相频曲线

3 实验测试与分析

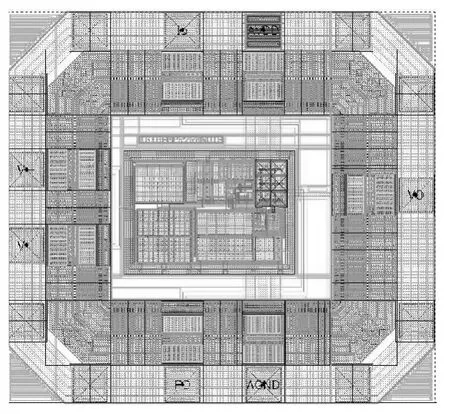

电路在CSMC0.18μm 1P6M工艺平台上进行了流片,芯片面积为0.067 km2。芯片照片如图9所示。

图9 放大器芯片照片

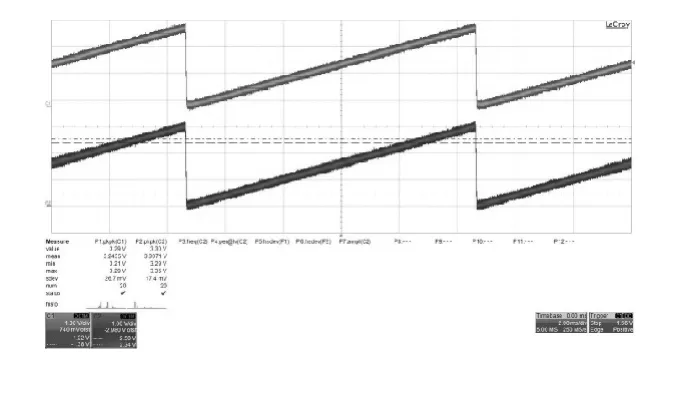

为测试电路的瞬态特性如输入输出轨到轨的特性,翻转速率(SR)和稳定时间(ST),将放大器接成单位增益缓冲器的形式进行测试。

图10是输入为0到电源电压3.3 V的斜波信号,输出跟随输入变化,也可从0~3.3 V。其中上面的波形是输入信号,下面的波形是输出信号。纵坐标是1 V/格,横坐标是2 ms/格。

图10 输入输出轨到轨的测试

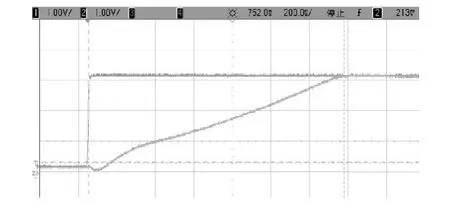

图11是SR的测试结果,为了测试上升沿的SR+而将波形进行放大,其中陡峭的信号是输入信号,缓慢的信号是输出信号。

图11 将上升沿放大后的SR测试结果

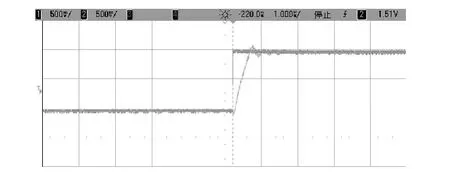

图12是ST的测试结果,为测试上升沿的ST+而将波形进行了放大,其中陡峭的信号是输入信号,缓慢的信号是输出信号。

图12 将上升沿放大后的ST测试结果

表1是该运算放大器典型性能的总结。其中SR+是上升沿的SR,SR-是下降沿的SR;ST+是上升沿的ST,ST-是下降沿的ST。

表1 运算放大器性能总结

4 结束语

探讨了一种输入输出轨到轨运算放大器的设计。该运算放大器的输入级总跨导在整个共模范围内变化仅为5.5%。运算放大器采用AB类推挽输出结构,并且将其与求和电路有机结合。整个运算放大器采用共栅米勒补偿,从而得到较大的带宽。芯片在华润上华0.18μm工艺平台上进行了流片。对芯片的性能进行了测试,测试结果和设计目标一致。此种运算放大器不仅可广泛应用于模拟集成电路和数模混合电路中,也可用于其他VLSI的设计中。

[1]Willy M CSansen.模拟集成电路设计精髓[M].陈莹梅,译.北京:清华大学出版社,2008.

[2]Matthijs O Pardoen,Marc G R Degrauwe.A Rail- to - rail input/output cmos poyer amplifier[C].IEEE Custom Integrated Circuits Conference,1989.

[3]Fischer J A,Koch R.A highly linear CMOS buffer amplifier[J].IEEE Solid - State Circuits,1987,22(3):330 -334.

[4]Steyaert M,Sansen W.A high-dynamic-range CMOS op amp with low -distortion output structure[J].IEEE Solid -State Circuits,1987,22(6):1204 -1207.

[5]Huijsing J H,Linebarger D.Low -voltage operational amplifier with rail- to - rail input and output range[J].IEEE Solid - State Circuits,1985,20(6):1144 -1150.

[6]Vittoz E,Fellrath J.CMOS analog integrated circuits based on weak inversion operation[J].IEEE Solid - State Circuits,1977,12(3):224 -231.

[7]许立峰,李冰.一种低压、恒跨导、轨对轨CMOS运算放大器设计[J].电脑知识与技术,2010(28):8140-8143.

[8]Hogervorst R,Tero J P,Eschauzier R G H.A compact 3 - V CMOSrail-to-rail input/output operational amplifier for VLSI cell library[J].IEEE Solid - State Circuits,1994(29):1505-1512.

[9]Seevinck E,Jager Wde,Buitendijk P.A low distortion output stage with improved stability for monolithic power amplifiers[J].IEEE Solid - State Circuits,1988(23):794 -801.

[10]Hurst P J,Lewis SH,Keane J P,et al.Miller compensation using current buffers in fully differential CMOS two-stage operational amplifiers[J].IEEE Transactions on Circuits System I,2004(51):275-280.