某雷达信号处理板的硬件设计与实现

2015-12-20张静

张 静

(中国航空计算机技术研究所第6研究室,陕西西安 710119)

雷达信号处理系统是由不同功能的若干电路板组成,用于实现系统所需的各种功能。在最初的雷达信号处理系统设计中,采用多个不同的电路板,由此造成了雷达处理板具有研制周期长、可靠性差、不便于维修的问题。近年来,随着高性能集成电路技术的成熟和超大容量现场可编程门阵列(FPGA)技术的快速发展,为设计一种多功能雷达信号处理板提供了可能。本文以双FPGA+DSP为核心,采用系统电路完成雷达信号处理的不同功能。所设计电路板可通过编程应用在不同的雷达上,实现雷达信号处理的不同功能[1-3]。

1 硬件系统设计框图

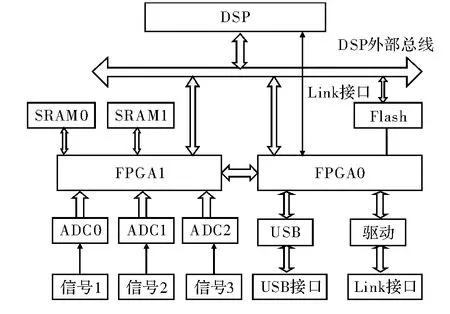

该信号处理板以AD公司的ADSP-TS101为核心,采用DSP加两片FPGA的系统结构。FPGA集中了大量中小规模器件的功能,而DSP主要进行信号处理。DSP和FPGA有各自的存储器,二者之间通过Link数据链路连接的松耦合结构,FPGA和上位机之间采用USB2.0连接,信号处理板包括一片Flash存储器和两片SRAM存储器。Flash存储器挂在DSP外部总线上,存储DSP引导程序、DSP应用程序和USB固件。SRAM用于存储经过预处理后的A/D采样数据。信号处理板上有两片FPGA,分别是信号处理FPGA(FPGA1)和接口控制FPGA(FPGA0),FPGA1主要用于A/D数据采样及信号处理,FPGA0主要用于实现信号处理板的接口控制。其优点是处理电路快速紧凑,同时兼有软件的灵活性。此外,可随时对FPGA编程便于及时补救设计或运行中的软硬件问题,信号处理板系统结构如图 1 所示[4-6]。

图1 信号处理板系统结构图

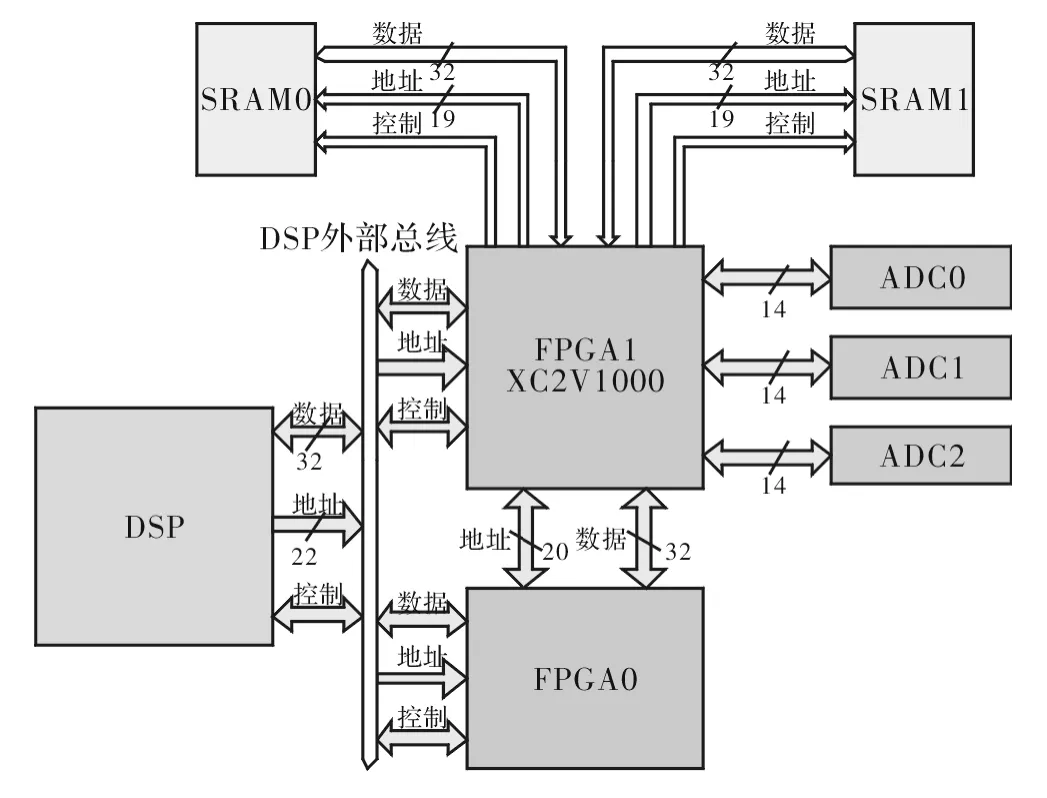

1.1 FPGA 电路的设计

信号处理板上有两片FPGA,分别是信号处理FPGA(FPGA1)和接口控制 FPGA(FPGA0),均采用Xilinx公司的Virtexii系列XC2V1000-4FG456I,高性能、高速度、低功耗的优点使其成为FPGA芯片的首选。该器件有100万系统门,1 280个CLB,40个18×18乘法器,1个工作时钟内即可完成乘法运算,8个时钟管理模块,最大IO管脚是432个。FPGA配置的ROM采用XQ18V04实现。

FPGA1主要用于A/D数据采样及信号处理,FPGA1的主要功能有:与ADC接口,以流水工作方式采集A/D数据;对采样的数据进行预处理;控制SRAM的读写,将预处理后的数据存入SRAM内,并控制DSP与FPGA通过乒乓操作模式分别读/写FPGA1外挂的两片SRAM;与FPGA0进行数据通讯。FPGA1电路示意图如图2所示。

图2 信号处理FPGA电路示意图

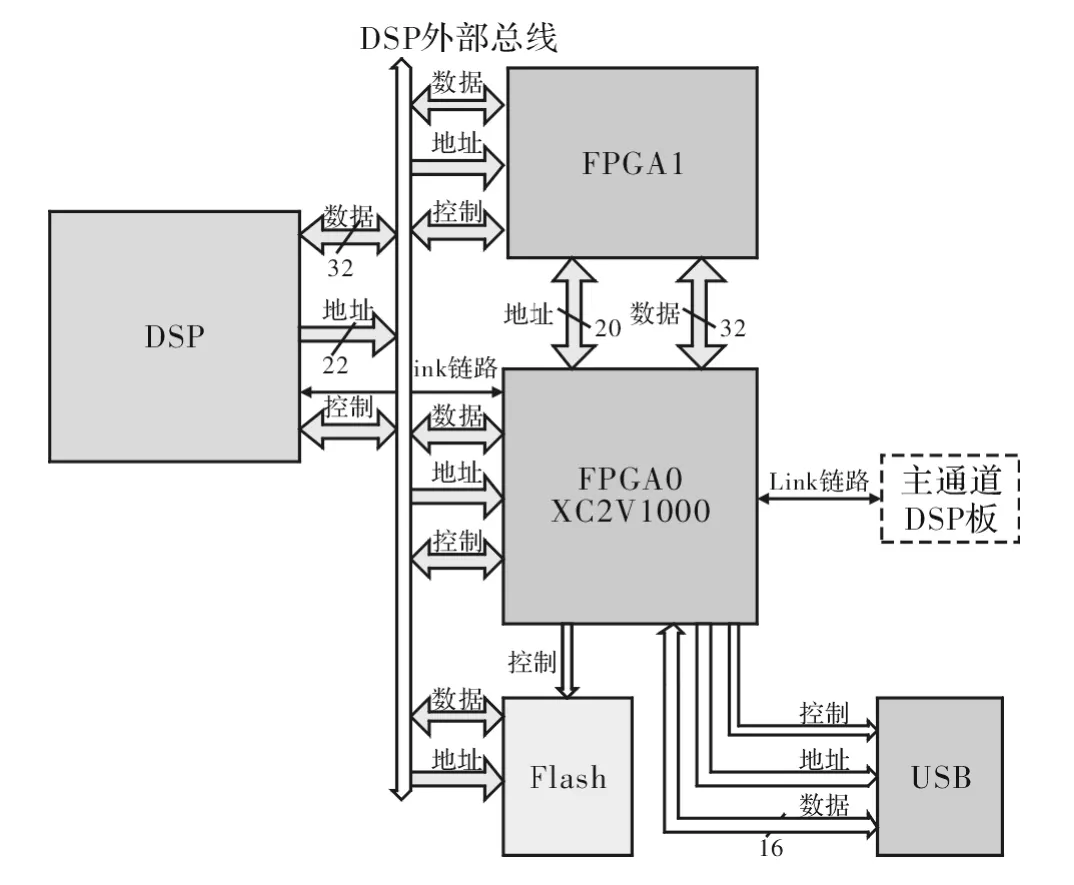

FPGA0主要用于实现信号处理板的接口控制,FPGA0的主要功能有:USB芯片控制和读写;接收USB接口发送的程序,通过Link向DSP加载程序;Flash存储器控制;将DSP的外部总线转换为ADSP-21060的Link端口,实现DSP与主通道DSP板的通讯;与FPGA1进行数据通讯。FPGA0电路示意图如图3所示。

1.2 DSP芯片电路的设计

目前高性能DSP有多种,综合比较各DSP的性能,ADPS-TS101主要有如下特性:内核工作时钟最高300 MHz,指令周期3.3 ns;提供最大1 500 Mflops运算能力,具有两个独立的运算单元,每个运算单元包括ALU、乘法器、64位移位器、32×32 bit寄存器堆和数据分配缓冲区(DAB),具有两个独立的运算单元,每个运算单元包括ALU、乘法器、64位移位器、32×32 bit寄存器堆和数据分配缓冲区(DAB),内部集成了6 Mbit的SRAM,6 Mbit的SRAM分为3个存储块,每块2 Mbit,具有3个独立的128位数据总线和3个32位地址线,分别连接到3个2 Mbit的内部SRAM中,可以实现数据、指令的存取和I/O访问,提供的内部存储器带宽为 14.4 Gbit·s-1。

图3 接口控制FPGA电路示意图

ADSP-TS101的JTAG接口采用直接连接方式,未经过驱动,JTAG接口的TRST信号采用4.7 kΩ的电阻下拉,按照器件手册要求,TRST信号在上电后必须保持低电平以确保JTAG接口工作正常,该信号在DSP内部具有100 kΩ的上拉电阻,外部4.7 kΩ下拉电阻可以保证信号电平保持约150 mV,能够满足0.8 V的低电平阈值,保证JTAG接口能够正常访问[6]。

1.3 存储电路设计

信号处理板存储器包括一片Flash存储器和两片SRAM存储器。Flash存储器采用 AM29LV160BT,设计采用512×8 kbit的配置。Flash存储器挂在DSP外部总线上,存储DSP引导程序、DSP应用程序和USB固件。系统上电时,DSP通过DMA搬运Flash前1 kB的引导程序到DSP内部存储器,通过引导程序再搬运其它应用程序。

SRAM存储器采用ACT-S512K32V,存储容量为512×32 kbit。两片SRAM均与FPGA1连接,SRAM用于存储经过预处理后的A/D采样数据,DSP和FPGA以乒乓操作模式分别访问两片SRAM。

1.4 A/D采样电路设计

信号处理板上有3路ADC转换电路,输入信号为单端2Vp-p信号,由同轴电缆输入后经运放驱动转换为差分信号后进入ADC芯片进行采样,采样数据输出到FPGA。

信号处理板采用高速差分低失真放大器SX8138MF和14位高速ADC芯片SAD9245MC/K,差分输入可减小ADC的失真,设计中差分放大电路的增益为1。SX8138MF的差分输出正负端和ADC的差分输入正负端分别串接1个49.9Ω的电阻,这样可减小ADC前端开关电容造成的影响。差分放大器输入负端增加的523Ω电阻用于平衡信号源阻抗和50Ω端接电阻。

1.5 其他电路设计

信号处理板上USB接口电路由一片USB接口芯片CY7C68013、一片复位芯片LC706T和一片电源供电芯片LT1763组成,USB接口芯片挂在FPGA0上,完成与上位机的通信和调试加载等功能。信号处理板USB接口工作在从设备模式,USB接口电路由主设备通过USB电源供电,当USB接口连接主设备时才能加电工作。

2 测试和分析结果

结合系统环境对某雷达信号处理板进行测试,精度是雷达的主要考核指标之一,包括角跟踪精度和距离跟踪精度。因此,文中用信号源仿真目标对该信号处理板进行测试,测试框图如4所示。

图4 测试原理框图

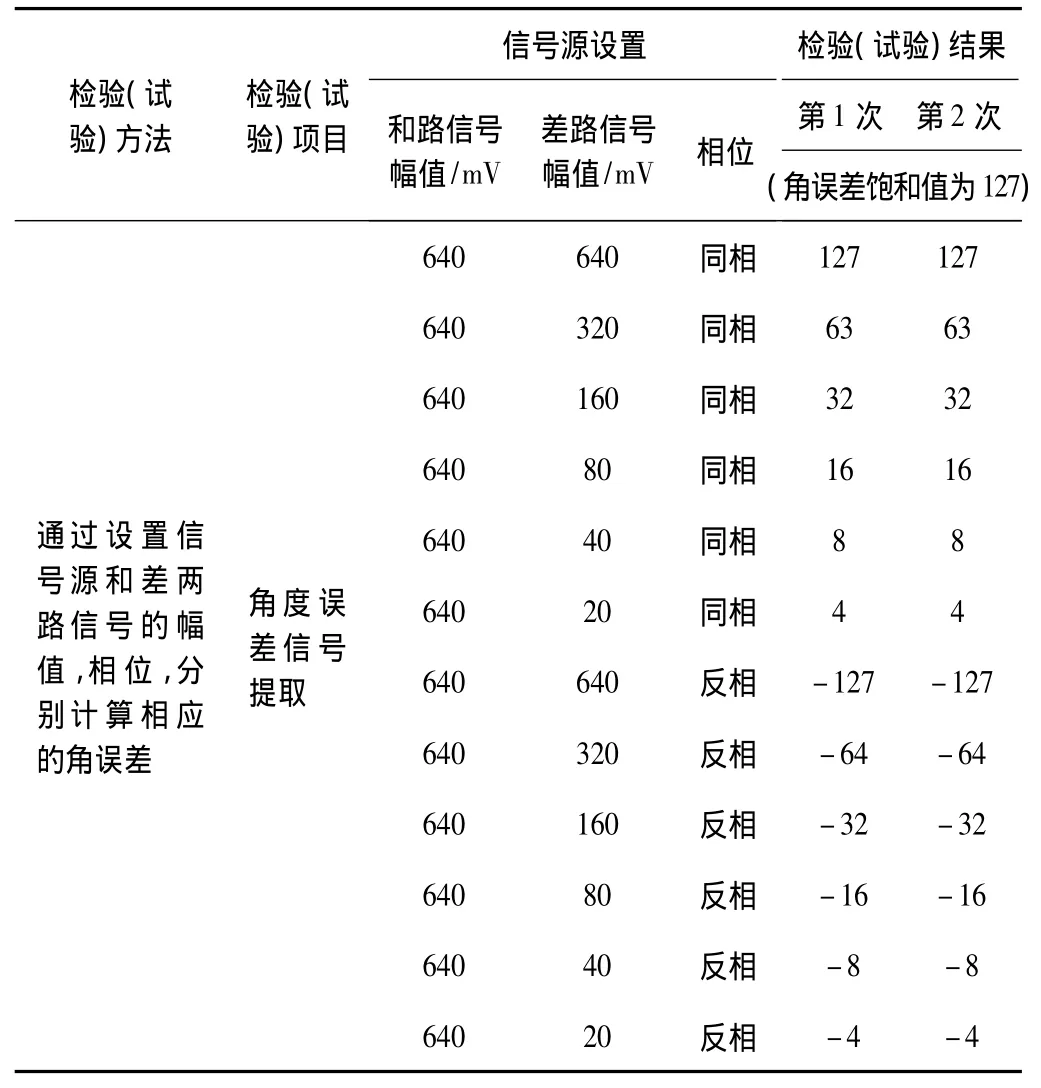

表1 角误差测试数据

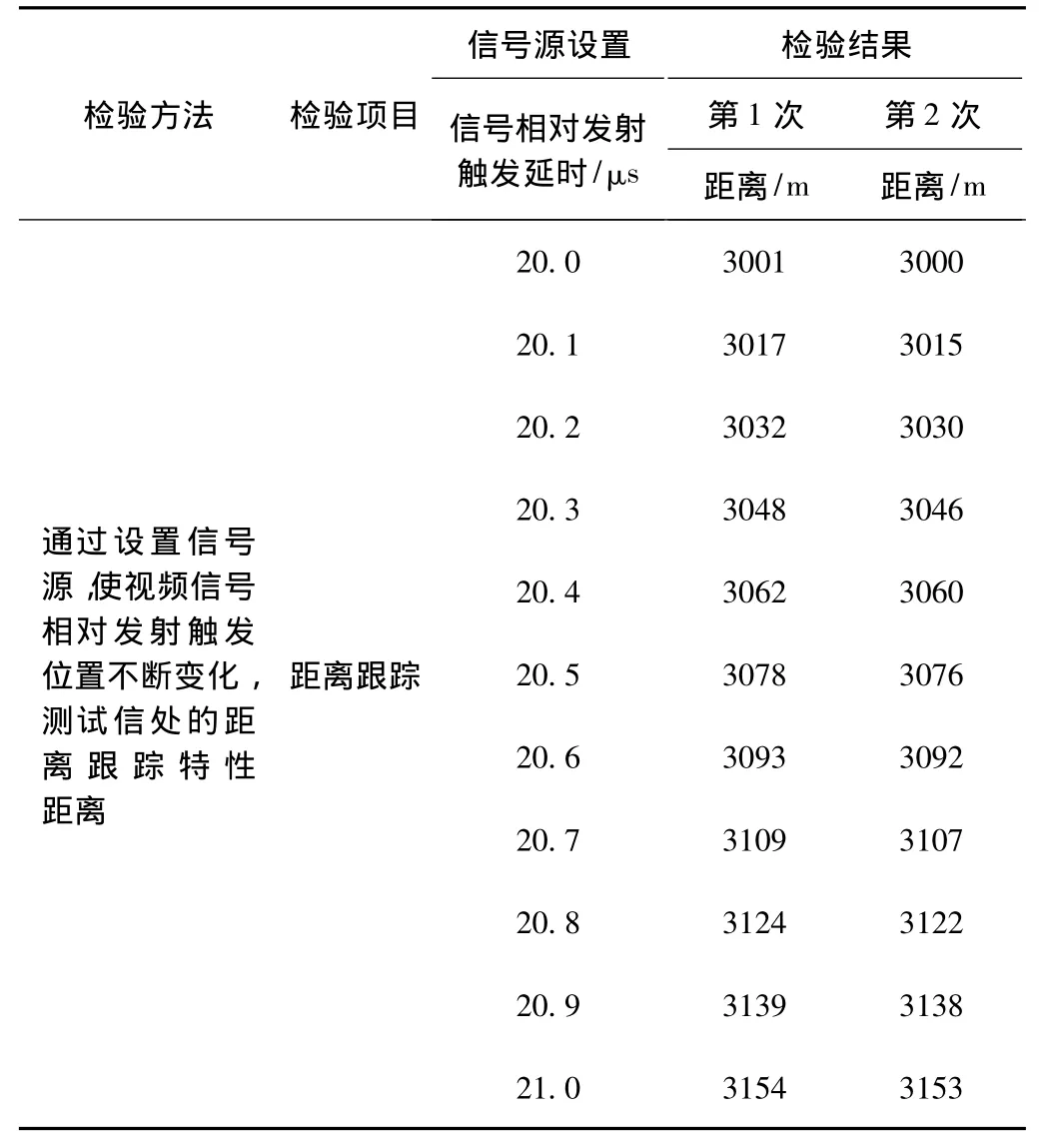

表2 距离跟踪测试数据

从测试结果看,该雷达信号处理板满足了运算能力强,精度高和稳定性好的要求。

3 结束语

DSP+FPGA是目前实时信号处理系统中应用广泛的系统组成形式,提出了一种基于FPGA和DSP的高速数据采集处理系统设计方案,本系统处理电路快速、紧凑,还可以随时对FPGA编程,以便及时修改设计或运行中的软硬件问题。该设计具有一定的通用性和可扩展性,适合模块化设计,同时开发周期短,系统易于维护和扩展。

[1]杨建,邓志清,高峰.基于FPGA的多功能雷达信号处理板硬件系统设计[J].舰船电子对抗,2011,34(6):52-55.

[2]张静,李自田,段晓峰.采用DSP+FPGA为核心实现DSP的高速并行处理系统[J].科学技术与工程,2007,7(23):6214-6217.

[3]吕宇,吴嗣亮.DSP+FPGA实时信号处理系统中FPGA设计的关键问题[J].微计算机信息,2005,21(5):80-81.

[4]高立宁,龙腾.基于TS201与FPGA的信号处理系统[J].微计算机信息,2008(32):260-261.

[5]郭裕兰,欧建平.基于Link口和 USB的数据传输设计[J].信息与电子工程,2009,7(3):169 -172.

[6]邓轲,范俊锋,吝莹.基于DSP+FPGA多通道单端/差分信号采集系统[J].电子科技,2013,26(3):33 -34.