基于模型设计的数字下变频系统的实现

2015-12-20卢文涛黄嵩人

卢文涛,黄嵩人

(1.湘潭大学 物理与光电工程学院,湖南 湘潭411105;2.湖南进芯电子科技有限公司,湖南 长沙410205)

0 引 言

采用专用的数字下变频 (DDC)器件完成下变频[1,2],虽然具有性能稳定,抽取比大等优点,但是灵活性差、价格昂贵,不能充分体现软件无线电的优势。FPGA 可以很好地解决这些问题,其在软件无线电的研发中具有重要的作用。

基于Matlab的Simulink工具结合DSP Builder高级模块库进行系统设计的方法已经得到广泛的应用,这是因为DSP Builder的高级模块库使用时分复用技术来优化逻辑利用率,同时自动插入流水线和寄存器来满足设计约束和提高电路的最大频率。由此得出的模型代码可获得与手工优化的HDL代码相近的性能,采用DSP Builder高级模块库设计系统,注重系统设计建模,进行代码的RTL 级验证与Quartus II工程的生成;设计支持更高效的开发过程,降低系统风险;在几天或者几周内便可完成系统设计任务,压缩了开发周期与大幅降低了开发成本,让产品极具竞争优势。

1 基于模型设计系统的方法对比

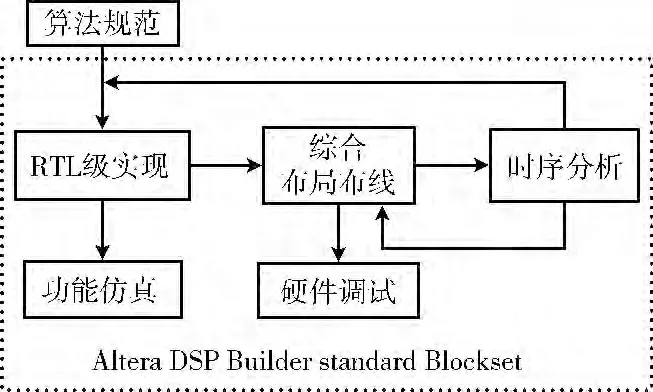

1.1 基于DSP Builder的标准模块库设计

基于Matlab的Simulink工具结合DSP Builder标准模块库[3](Altera DSP Builder standard Blockset)进行系统设计的方法面世已久,主要的设计特点如图1所示。

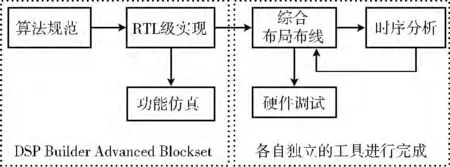

1.2 基于DSP Builder的高级模块库设计

图1 标准模块库设计特点

基于Matlab的Simulink工具结合DSP Builder高级模块库进行系统设计的方法已被广泛的采用,近几年,Altera公司把优化与拓展DSP Builder高级模块库的功能放到了首位。主要的设计特点如图2所示。

图2 高级模块库设计特点

1.3 两种模块库设计对比

通过DSP Builder的标准模块库与高级模块库的设计特点对比可知,利用DSP Builder标准模块库设计时,除了算法研究之外,RTL 级实现、功能仿真、综合与布局布线、时序分析、硬件调试等都在DSP Builder标准模块库中进行,操作简单且不需要太多的传统开发FPGA 的技巧,但设计的好坏主要依靠DSP Builder工具的性能,灵活性很差;而采用DSP Builder高级模块库设计系统时,除了算法验证、RTL级实现与功能仿真在高级模块中实现外,其余部分均可采用传统的FPGA 开发模式,不但给用户带来了更大的灵活性,而且可以更好地满足系统的Fmax、延时控制、矢量和多通道设计、高级数学函数,以及支持定点和单精度、双精度浮点数据通路进行优化设计。因此本系统采用的是DSP Builder高级库进行设计。

2 数字下变频 (DDC)模块介绍

2.1 数控振荡器 (NCO)

NCO 的作用其实就是产生一个理想的正弦数字信号与余弦数字信号,即

式中:n的取值范围为所有的自然数,fL0——本地振荡频率,fs——DDC输入信号的采样频率。

产 生NCO 信 号 的 方 法 有:分 布 式 算 法[4,5]、Walsh 变换[6]、查表法和坐标旋转数值计算法[7](CORDIC)。

其中,查表法是根据有限的相位,先将相应的正弦和余弦值计算好,并以相位为地址信息,将计算好的正弦值和余弦值存储在相应的位置上。使用时,则通过相位信息来读取相应的正弦值和余弦值。这种方法工作效率高、电路设计简单,但是精度很有限。

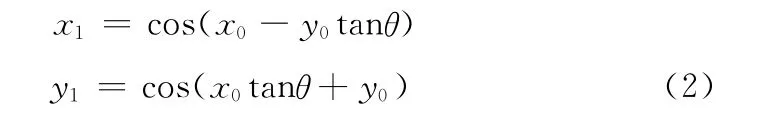

CORDIC坐标旋转数值计算法则是以实时计算的方法来获取每一个相位角的正弦值和余弦值。CORDIC 算法是通过矢量旋转来实现的,基本原理:

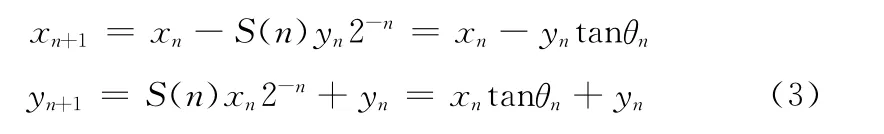

设初始矢量为r0(x0,y0),旋转一个角度得到一个新的矢量r1(x1,y1),可以得到

式中:假设将旋转角度θ细化为n 个更小的角度,初始矢量经过n次旋转,得到一个新矢量rn(xn,yn)=r1,且每次旋转的角度θn满足tanθn=S(n)(2-n),则可推出

式中:S(n)——符号函数,决定了旋转的方向,其取值只能为±1。而S(n)究竟取1还是取-1,则需要根据Zn→0为选择标准。而Zn表示每次旋转后的剩余角度,当旋转一定次数后Zn趋于0,而当Zn<0时,表示旋转的角度超过了θ,则S(n+1)=-1,当Zn>0时,则表明旋转角度没达到θ,则S(n+1)=1。

在ModeIP库中有实现NCO 算法的模块,当模块中valid信号有效时,channel中的data信号才能进入NCO 模块进行处理,最后输出data,valid和channel信号。

2.2 CIC积分梳状滤波器

为使不同的系统兼容,需要使上级系统提供的信号能满足下级系统的性能要求,这时需要一定的采样速率转换。

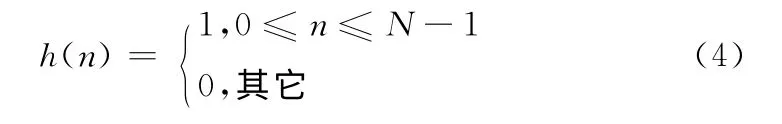

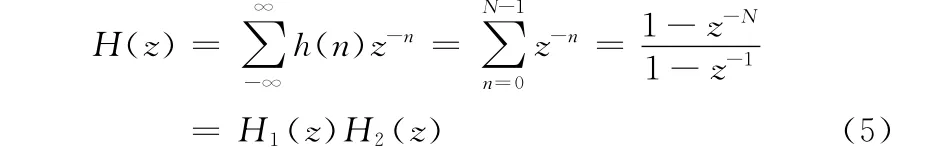

CIC积分梳状滤波器[8,9]在这方面有很重要的应用。所谓积分梳状滤波器,是指滤波器冲击响应满足

式中:N——滤波器的阶数。CIC滤波器的Z变换为

其中

在ModeIP库中有实现CIC算法的模块,当模块中valid信号有效时,channel中的data信号才能进入CIC 模型进行滤波,最后输出data、valid、channel信号。

2.3 HB半带宽滤波器

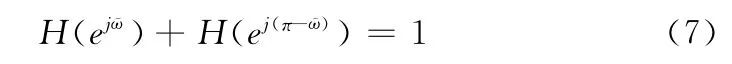

半带宽滤波器[10]是一种特殊的FIR 滤波器,其阻带宽度和通带宽度相等,且通带、阻带纹波也相等。

HB滤波器的频率响应为

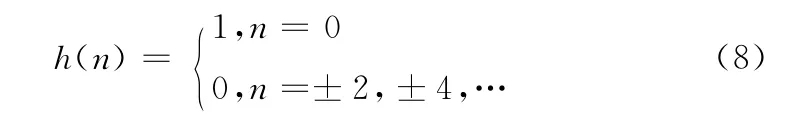

半带宽的冲击响应为

由于在非零的偶数点上,半带宽滤波器的冲击响应为零,因此使用半带宽滤波器实现的采样率变换时,只需要一半的计算量。

在ModeIP库中有实现FIR 算法的模块,当模块中valid信号有效时,channel中的data信号才能进入FIR 模块进行滤波,输出data、valid和channel信号。

3 DDC在DSP Builder高级库中的实现

3.1 DDC子系统的实现

用DSP Builder 高级库中的模块mixer、NCO、CIC、FIR 模块分别替代对应图3 中的部分,在此基础上添加上Mux模块、Scope模块、Constant模块、Register Field 模块、Inport 模 块、Terminator 模 块、Register Bit 模 块、ChanView 模块、Device模块、Outport模块等得到DDC 子系统,即为DDCChip系统,如图3所示。

图3 DDCChip子系统的设计

3.2 16通道DDC系统的设计

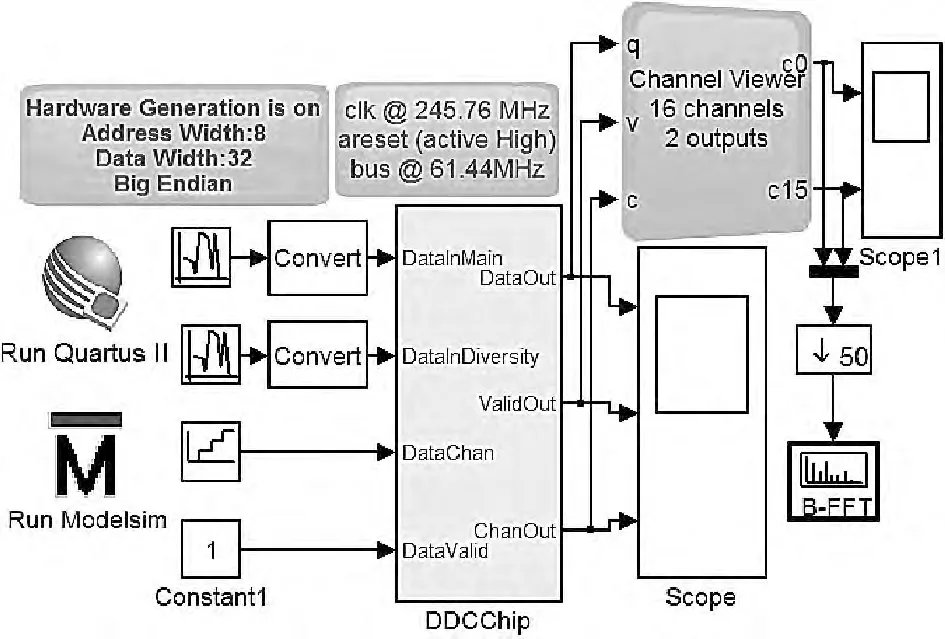

添加Run Modelsim 模块、Run Quartus II模块、Edit Params模块、Signals 模块、Control模块、Channel View模块、Down sample模块、Spectrum Scope模块、Random Number模块、Repeating Sequence Stair模块、Convert模块、Manual Switch 模 块、Constant 模 块、Mux 模 块、Scope模块等到图3到所示的DDCChip子系统中,将DDCChip子系统打包成一个子系统,完成整个16通道DDC 系统设计如图4所示。

图4 整个16通道DDC系统顶层设计

4 仿真结果与验证分析

4.1 设计参数设置

本次设计系统的时钟频率为采样频率的4 倍,即为245.76 MHz。NCO 运行一次的时间为5.59个时钟,也就是说模型产生正弦波与余弦波的波长为5.59个时钟,设定的采样频率为61.44 MHz,则NCO 产生的本振频率为10.326 MHz。而TestBench中的输入频率每6个时钟旋转一次,采样频率也61.44 MHz,则输入信号的频率为10.24 MHz,可得低频信号的频率为86KHz;下变频通道数为16个,CIC 滤波器采用五级串联,执行16 因子的抽取;第一个FIR 滤波器采用了4抽头21阶奇对称滤波器,第二个滤波器采用了4抽头63阶奇对称滤波器。

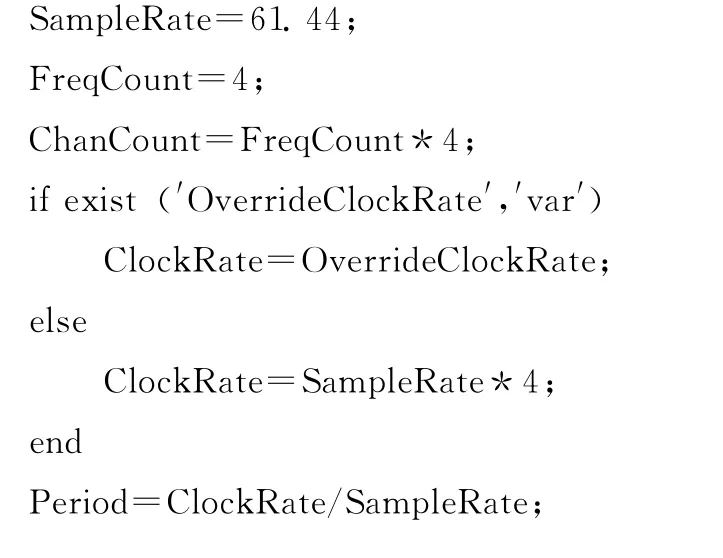

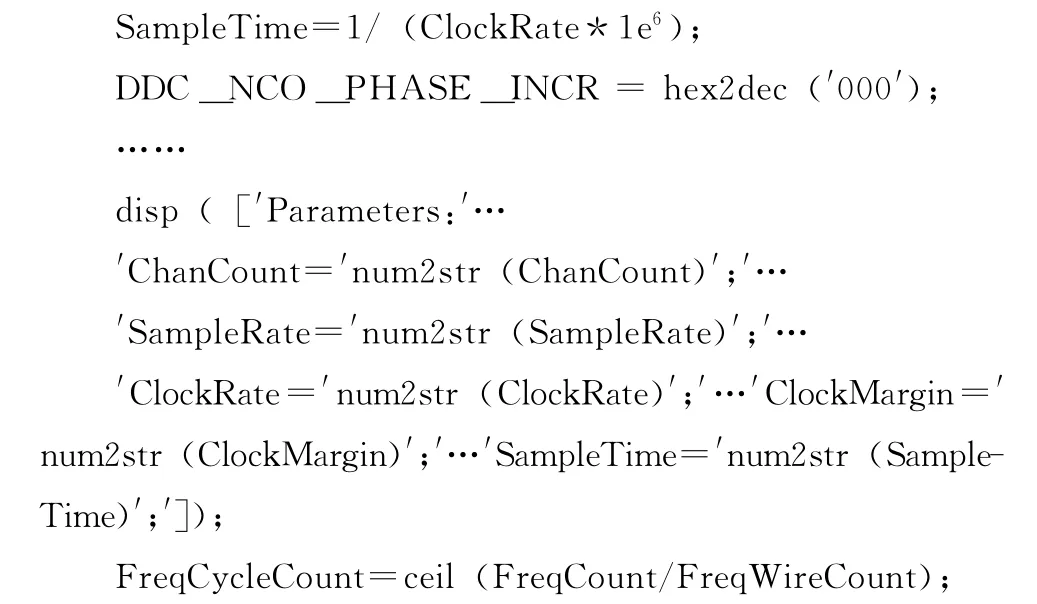

相关顶层参数设置脚本 (*.m)内容如下:

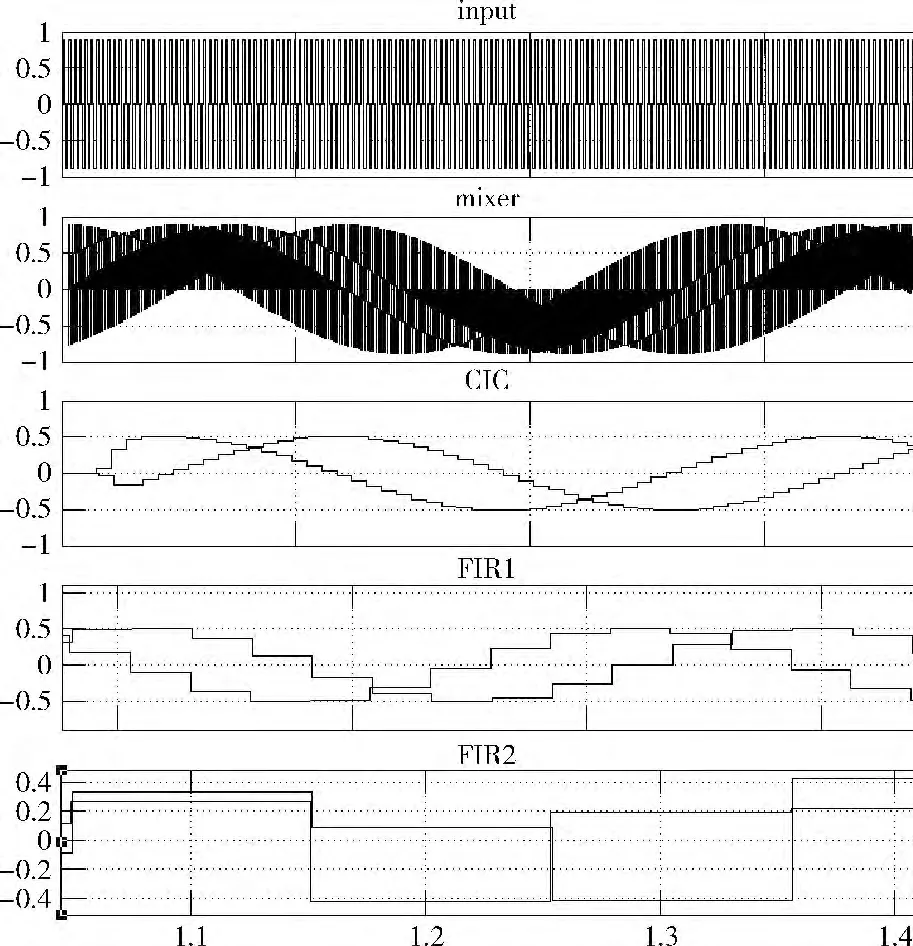

4.2 Simulink仿真波形

将仿真时间设置为550000*SampleTime,启动模型功能仿真,可以得到仿真波形。第一组信号为Testbench 的高频输入信号。第二组信号为混频器的输出结果。这组信号中包含需要提取的信息,以及很多高频杂波。第3个信号为CIC滤波器抽取之后的调整信号,第4个信号为FIR1滤波器滤波和抽取之后的调整信号,第5个信号为FIR2滤波器抽取之后的调整信号,即低频低速信号。从图5可以看出,设计的DDC系统已经实现了数字下变频的功能。

图5 各个模块仿真输出波形

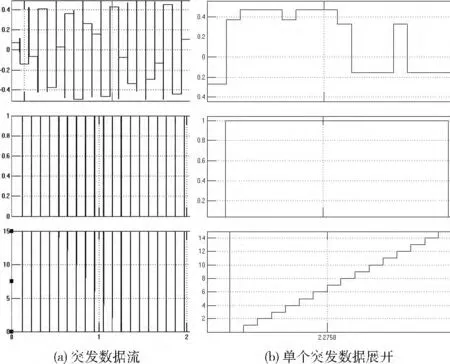

通过在Simulink中的仿真得到DDC系统的输出波形如图6所示。其中图6 (a)为突发数据流,图6 (b)为单个突发数据展开,该设计将Decimating CIC 分成4个不同的CIC,每个都以4通道进行操作,降低了输出端口的数据速率,所有16 路数据采样都可以适配到一根线上,DSP Builder将数据打包到单个TDM 线上,由于整体采样速率为61.44 MSPS×16 通道/16 抽取=61.44 MSPS,并且系统的时钟频率为245.76 MHz,所以25%的周期中数据是有效的。16路通道的顺序为0,1,…,15。

图6 DDC系统仿真结果

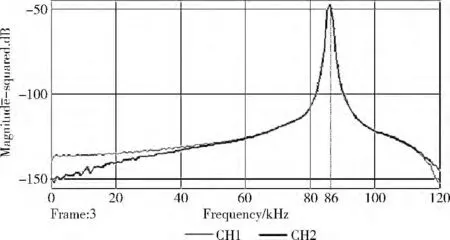

DDC系统模型仿真输出为正交I/Q 两路信号,该两路信号均为零中频数字信号,仿真输出频谱如图7所示。从图中可以看出这两路低频信号的中心频率为86KHz,满足设计参数要求。

图7 DDC仿真输出频谱

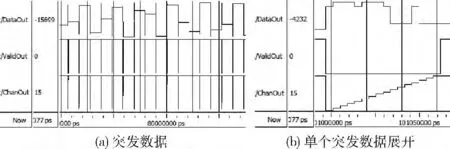

4.3 Modelsim 仿真波形

Run Modelsim 模块使用硬件生成过程中产生的脚本,启动Modelsim,通过自动生成的TestBench对设计进行仿真。这个过程将编译所有的VHDL 文件,将信号添加到Modelsim Wave窗口,并在Simulink设计实例运行的同时进行Modelsim 仿真,仿真结果如图8所示。其中图8 (a)为突发数据流,图8 (b)为单个突发数据展开,从仿真图可以得到Modelsim 仿真结果与DSP Builder功能仿真的结果是一致的,再次验证该设计达到设计参数要求。

4.4 占用资源对比

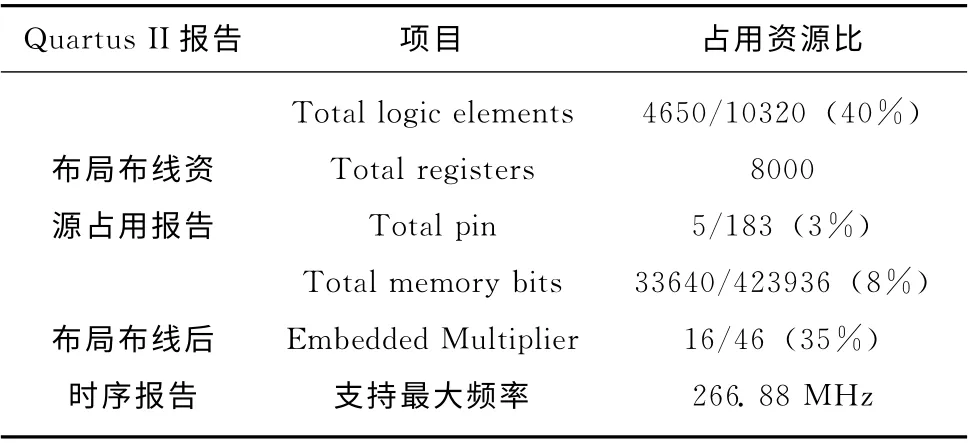

通过Run Quartus II模块启动Quartus II将用户的设计自动添加到工程中,通过编译、综合、布局布线,得到占用的资源。占用资源对比[10,11]情况见表1。通过对比可得该系统所占用的资源比文献 [10,11]占用的资源少,而且工作的最高频率也提高了,说明整体系统设计进行了优化。

图8 Modelsim 仿真结果

表1 Quartus II布局布线后占用资源与时序分析

5 结束语

本文提出一种基于Simulink的DSP Builder高级模块库设计方法设计出数字下变频系统,并且仿真与验证了设计的有效性与正确性。从模型的建立到FPGA 的实现都是在可视化的设计环境下进行,使设计者可以避开HDL 的复杂编程,将更多的时间和精力用在对系统的设计和优化上,不但优化设计资源,而且极大地提高设计效率,缩短了产品开发面市的时间。

[1]XU Xiaoming,CAI Canhui.Design of digital down conversion based on FPGA [J].Communication Technology,2011,44(10):19-21 (in Chinese).[徐小明,蔡灿辉.基于FPGA 的数字下变频 (DDC)设计 [J].通信技术,2011,44 (10):19-21.]

[2]ZHANG Lei,CHEN Yaning,LIU Chengyu,et al.Design of digital down conversion ASIC circuit[J].Application of Electronic Technique,2013,39 (11):37-40 (in Chinese). [张磊,陈亚宁,刘成玉,等.DDC 数字下变频ASIC 电路设计[J].电子技术用,2013,39 (11):37-40.]

[3]WANG Dongjian,ZHANG Xiaohua,LIU Xin,et al.Design of digital down conversion based on FPGA [J].Automation&Instrumentation,2010 (1):52-53 (in Chinese).[王东剑,张小华,刘鑫,等.一种基于FPGA 的数字下变频设计 [J].自动化与仪器表,2010 (1):52-53.]

[4]LIN Zhidian,ZHANG Fangpei,YUAN Guoshun.Design and implementation of a high speed FIR filter based on FPGA [J].Microelectronics,2013,43 (4):537-540 (in Chinese). [林志典,张方佩,袁国顺.基于FPGA 的高速FIR 滤波器的设计与实现 [J].微电子学,2013,43 (4):537-540.]

[5]WANG Fadong,LIU Yu.Comparison between distributed arithmetic architectures of high-order digital filter[J].Technical Acoustics,2009,28 (3):307-311 (in Chinese). [王法栋,刘宇.高阶数字滤波器分布式算法结构比较 [J].声学技术,2009,28 (3):307-311.]

[6]HU Hui,YE Xinhua.Discrete Walsh transformation parallelism analysis and achievement[J].Computer Engineering and Application,2009,45 (2):82-84 (in Chinese). [胡辉,叶鑫华.离散Walsh变换并行性分析与实现 [J].计算机工程与应用,2009,45 (2):82-84.]

[7]SHI Lei,LI Jing,ZHANG Huaiwu.CORDIC algorithmbased digital down conversion [J].Information and Electronic Engineering,2009,7 (3):227-234 (in Chinese).[史磊,李婧,张怀武.基于CORDIC算法的数字下变频 [J].信息与电子工程,2009,7 (3):227-234.]

[8]XIAO Ruichuan,LIU Yanping,PENG Chenggong,et al.Design and implementation of CIC filter for DDC based on FPGA [J].Electronic Design Engineering,2013,21 (5):160-162 (in Chinese).[肖瑞川,刘艳萍,彭成功,等.基于FPGA 的DDC中CIC滤波器的设计[J].电子设计程,2013,21 (5):160-162.]

[9]LAN Jinbao,WANG Na,ZHANG Ruitao,et al.A decimation fliter for digital down-conversion [J].Microelectronics,2011,41 (1):1-5 (in Chinese). [兰金保,王娜,张瑞涛,等.一种数字下变频抽取滤波器的设计 [J].微电子学,2011,41 (1):1-5.]

[10]LIU Yunlong,ZHANG Weixia.Design of digital down conversion based on FPGA [J].Microcomputer &Its Application,2013 (17):53-55 (in Chinese). [刘云龙,张伟霞.基于FPGA 的数字下变频器的设计 [J].微型机与应用,2013 (17):53-55.]

[11]HUANG Minghui,WANG Haijuan.A new method of buil-ding digital down conversion[J].Electronic Sci &Tech,2010 (11):51-54(in Chinese).[黄明慧,王海娟.数字下变频的一种新型设计方法[J].电子科技,2010 (11):51-54.]