基于DM 368的视频捕获与编解码系统设计

2015-12-15酆祥龙魏本杰姜秀杰

酆祥龙,魏本杰,姜秀杰

(1.中国科学院 空间科学与应用研究中心,北京100190;2.中国科学院大学 北京100049)

基于DM 368的视频捕获与编解码系统设计

酆祥龙1,2,魏本杰1,姜秀杰1

(1.中国科学院 空间科学与应用研究中心,北京100190;2.中国科学院大学 北京100049)

为了实现对视频进行捕获后压缩,文中提出一种基于DM368的视频捕获压缩方案,并设计完成相应的硬件与软件。该系统主要使用TI达芬奇DM368片上系统作为主控芯片,采用TVP5158作为视频采集前端。采用1G容量的DDR2内存作为易失性存储器。采用1GFlash作为系统内核与文件系统的存储介质。软件部分在Linux平台中使用达芬奇DVSDK进行编程。压缩规格上使用目前较为流行的MPEG4算法。从而实现视频的捕获与压缩。经实际测试显示,使用该平台进行视频捕获压缩开发较以往DSP和FPGA方案更加成熟稳定,并可以通过TI的开发工具和现有软件库大大减少开发周期。

DM368;MPEG4;视频;TI达芬奇

随着人类社会的进步,视频技术越来越发挥着重要的作用。视频的传输也经历了由模拟到数字的转变。数字视频的分辨率也随着感光元器件的革新而不断增加,在给人们提供越来越清晰额视觉享受的同时产生了更大的视频数据。针对海量的视频数据,人们通过改进压缩算法使得视频数据所需的存储空间大大减小。时至今日,ITU-T已经公布了H.264压缩标准,并且在推进H.265压缩标准。在MPEG会议的努力下,MPEG-4压缩标准也开始应用于数字视频领域。这些标准都使得高分辨率的视频数据以非常高的压缩率压缩。最明显的成果便是以网络为媒体的实时视频传输技术。而在硬件方面随着微电子技术的进步,微处理器体积变得越来越小但是处理能力如摩尔定律那样快速增长。这些技术的进步使得嵌入式设备实现数字视频的捕获压缩成为可能。目前常用的设计方案常用DSP+FPGA或者DSP+ARM组合实现。鉴于嵌入式设备对数字视频压缩的要求,诞生了许多现成的压缩芯片,只需要发送指令和数据就可以完成原始视频数据的压缩[1-2]。

多处理器组合,虽然可以既利用DSP芯片的数字信号处理能力,又利用协处理器的逻辑处理能力,但是这种组合属于板级连接设计者在设计过程中难免会引入连接错误,给项目开发带来许多不稳定因素,大大延长开发周期。同时两种不同公司的芯片在设计过程中,接口逻辑会有或多或少的不同,也会给设计者带来意想不到的问题。近年来许多芯片公司将核心处理器如ARM、DSP和其他外围硬件内核集成到一块芯片中,这种System On Chip(SOC)技术大大增强了新的嵌入式视频处理器的稳定性。在其中TI公司开发出达芬奇系列视频处理SOC,并提供了相应的开发环境与成熟的视频处理算法。2010年4月TI推出DM368视频处理芯片。与之前DM365视频库软件兼容,但提供了更为丰富的接口。

文中介绍一种使用达芬奇DM368SOC实现数字视频的捕获并按照MPEG4标准进行压缩的设计。本设计将对模拟视频信号进行采样量化,将原始的视频数据按照MPEG4压缩标准进行编码。最后将编码后的压缩视频解码输出,从而验证视频的编解码及视频输出功能。

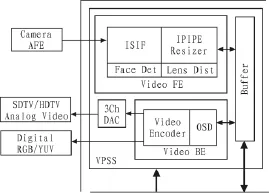

1 总体设计

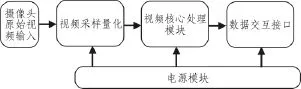

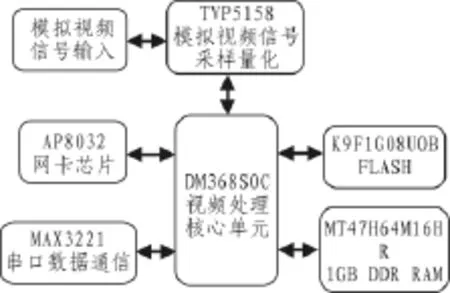

该嵌入式视频处理设备整体结构如图1所示,模拟摄像头采集的视频信号经过视频处理前端,进行按照一定视频格式进行采样量化,将模拟视频信号转换为数字信号。这些视频原始数据被传输到视频处理模块。然后通过该模块将原始视频数据进行相关的视频压缩处理。本设计预留网口和模拟视频输出端口,可以将压缩的视频解压输出,并通过模拟视频输出端显示在微计算机终端或者嵌入式显示设备。

图1 系统总体结构图Fig.1 Structure diagram of the video process system

2 系统硬件设计

嵌入式视频处理的硬件设计由视频前端、视频处理模块、电源部分和外部接口四个部分组成。电源部分是一个嵌入式设备的最基础模块,是一个设备能够稳定运行的基础。该设备由于使用了多个芯片,每个芯片需要的供电电压不同,这就需要使用多个电源芯片进行电压转换产生对应的供电电压。本次设计中将输入的12 V电源经第一次电平转换产生5 V电源。5 V电源经两个芯片转换产生1.1 V、1.2 V、1.8 V和3.3 V电源。最后产生的3.3 V电源经转换产生1.24 V电源。如图2所示。

图2 电源模块设计Fig.2 Design of power

模拟视频接入端连接至TVP5158进行初步处理。TI公司的TVP5158是四路NTSC/PAL视频译码器,具有单独的定标器,降噪,自动对比度调整,以及灵活的输出格式编制器。TVP5158提供和DaVinc处理器的音频和视频连接接口,视频输出端支持8位ITU-R BT.656和16位4:2:2 YCbCr。输出端连接DM368视频处理器。

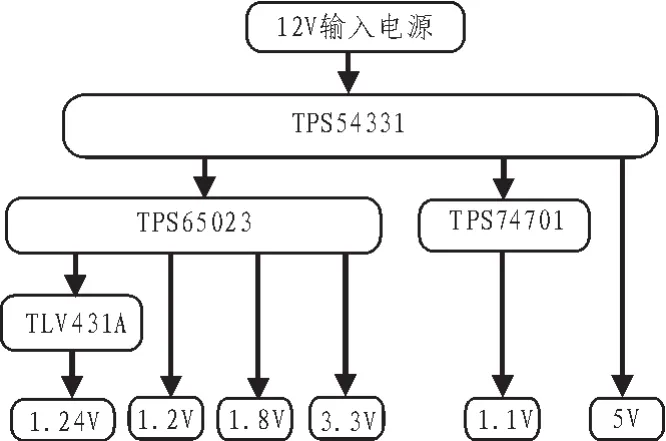

在DM368的片上系统中有许多硬件设备。对于视频处理来说最重要的是其中的VPSS,即视频子系统(结构如图3所示)。该系统有若干硬件组件支持对视频的处理,可以实现从YUV422到YUV420的格式转换等具体处理操作。其中的VPFE(视频处理前端)和VPBE(视频处理后端)可以实现视频数据的预处理和解码输出功能。除此之外,该系统中还有一个缓冲器和一个DMA控制器,可以充分使用外部DDR2存储器[3]。本次设计采用一片1G容量DDR2存储器,该RAM与DM368的内存引脚相连,为该芯片处理大数据视频提供了足够的运行空间。使用三星公司的1G容量FLASH作为Linux系统内核、文件系统和视频应用程序的存储区域。

图3 VPSS框图Fig.3 Block diagram of VPSS

在视频输出部分,DM368自带了模拟视频输出接口,另外考虑到嵌入式Linux的开发调试需求和目前常用的视频传输方法,本次设计还添加了网络和串口。网卡主控芯片采用AR8032,串口部分采用MAX3221实现通信电平转换。整个视频处理模块硬件设计如图4所示。

图4 视频处理模块设计Fig.4 Design of video process

3 系统软件设计

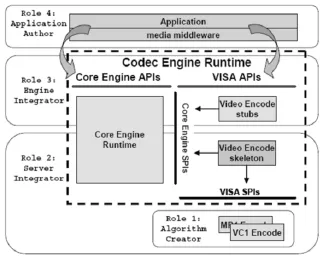

TI公司为达芬奇系列视频处理器设计了软件开发构架,方便开发者在这个构架上开发自己的视频处理程序。该软件开发构架核心为CODE ENGINE编程框架,它能够自动地请求和实现符合eXpress DSP的Codec算法。在code engine中为开发人员提供3种开发方向。作为算法开发人员,可以将设计好的视频处理算法通过Codec部分,按照TI通用的视频处理算法标准生成算法库,并进行打包。视频应用程序开发人员可以在APP部分调用已经打包好的算法库,开发自己的视频处理应用程序。在应用程序与算法库之间是sever部分,该部分可以实现Codec算法库被APP调用。Server为Codec提供APP调用过程中所必须的组件 (例如BIOS、Framework Component、DSPLink等),并生成可执行文件[dv]。系统软件设计的结构图如图5所示。

图5 CODE ENGINE结构图Fig.5 The structure of CODE ENGINE

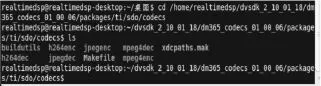

在本次视频编解码软件设计中,DM368自带了MPEG4和H.264视频编解码算法。在安装好的开发环境中,进入算法库文件夹,查找MPEG4视频压缩算法与解压算法。图中显示的库文件提供的是可以直接被APP端使用的,下一步就是编写相应的应用程序。

图6 DM368自带视频算法库Fig.6 The algorithm of video process for DM368

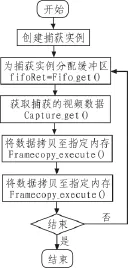

设计视频处理应用程序,主要需要编写 Capture、encodedecode和display3个部分的代码。在Capture中主要使用前缀为“Capture_”的函数,这些函数直接使用了V4L2的相应函数接口,从而帮助软件从底层获取与视频处理相关的数据[5-6]。其主要执行流程如图所示[7]。

图7 捕获软件的流程图Fig.7 Flow chart of the software of capture

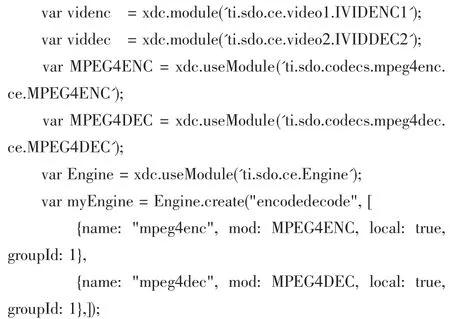

在视频编解码软件部分中,主要使用了DM368自带的视频编解码算法,在编程之前需要首先配置encodedecode.cfg文件。配置参数如下:

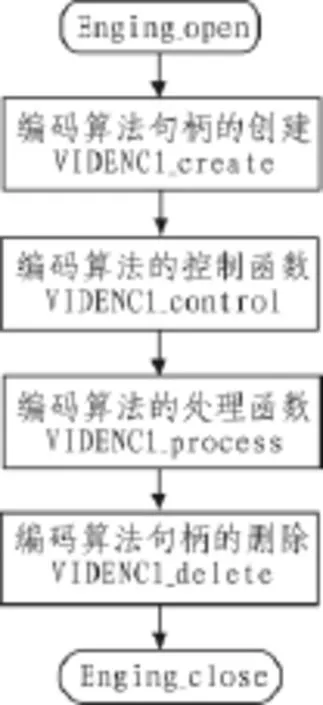

配置完成后,在应用程序中便可以创建编码算法句柄调用算法库。编码与解码都需要首先打开engine,然后创建算法句柄,接着操作算法控制函数与算法处理函数。最后执行完毕删除编码算法句柄,并关闭engine。以编码为例,流程图如图所示。

图8 编码软件的流程图Fig.8 Flow chart of the software of encoding

在 Linux下实现视频输出程序 display,是通过操作framebuffer实现的。该帧缓存提供了个多种操作方法。开发者想要在显示屏中显示视频其实就是将解压后的视频数据写入framebuffer中来完成的。至此视频处理应用程序编写完毕。

4 系统测试

在Linux开发环境中打开终端,更改路径进入源代码文件 夹 :cd /dvsdk_2_10_01_18/dvsdk_demos_2_10_00_17/dm365/encodedecode。输入make,Makefile文件会自动编译整个工程。将编译好的整个文件夹复制到nfs共享路径下。使用串口与网线,将电路板与开发主机相连。最后连接显示器与模拟视频输出端口。上电之后更改当前路径到测试目录,首先加载该视频测试程序所需的驱动模块:./loadmodules_sd.sh。加载完成后打开运行测试程序./video可以看到编解码视频的输出情况,移动摄像头可以看到视频有明显延时。显示情况如图所示。

Design of video capture and codec based on DM 368

FENG Xiang-long1,2,WEI Ben-jie1,JIANG Xiu-jie1

(1.Center for Space Science and Applied Research,Chinese Academy of Sciences,Beijing 100190,China;2.University of Chinese Academy of Sciences,Beijing 100049,China)

In order to achieve the capture and codec of video,a design based on DM368 is described with its both hardware and software.In this design,DM368 from TI Davinci is the main control and process unit.TVP5158 is added to capture the analog video signal.A DDR2 with volume of 1GB is used as RAM of this system.Besides a Flash from SAMSUNG with volume of 1GB is worked as the memory to store the kernel and file system of Linux.The software is developed on Linux with DVSDK from Davinci.MPEG-4 is chosen as the standard of video compression.By real test,this platform can perform MPEG-4 much better than the platform with DSP and FPGA.This design is much mature and reliable.With the help from the tools of TI and all the algorithm library people could develop the software much faster.

DM368;MPEG4;video;Davinci TI

TN919.82

A

1674-6236(2015)10-0166-03

2014-10-24 稿件编号:201410176

863国家支持项目(Y28021A220)

酆祥龙(1989—),男,山东淄博人,硕士研究生。研究方向:嵌入式,视频编解码。