倒计数器测频电路的设计与实现

2015-12-15杜晓宇徐联祥

杜晓宇,徐联祥,2,石 雄

(1.武汉轻工大学 电气与电子工程学院,湖北 武汉 430023;2.盐城工学院 江苏省新型环保重点实验室,江苏 盐城224000)

倒计数器测频电路的设计与实现

杜晓宇1,徐联祥1,2,石 雄1

(1.武汉轻工大学 电气与电子工程学院,湖北 武汉 430023;2.盐城工学院 江苏省新型环保重点实验室,江苏 盐城224000)

将雷达发射脉冲信号下变频并整形形成中频TTL(晶体管-晶体管逻辑电路)方波信号,根据倒计数器测频的原理,选择二进制同步计数器74LS161三片级联后对该信号进行计数,取信号的300个脉冲形成计数区间,在此区间内用三片级联的74F161对100 MHz的标准方波进行计数,随后将计数结果送入单片机,由单片机计算出当前的中频频率,在控制DDS本振频率合成器对本振输出进行调整,保证中频信号频率稳定在规定范围内,由此构成数字式的雷达自动频率控制系统。

倒计数法;频率测量;同步计数器;单稳态触发器

TTL集成电路是国内外生产时间最长、产量最大的一种集成电路,其固有的结构特点、优良的电性能、自身不断地结构改进及性能提升使“古老”的TTL集成电路几经变迁却依然能够维持其盛况不衰[1]。

TTL集成电路具有高的可靠性、宽的工作速度范围、较低的功耗和良好的抗干扰能力,本文应用TTL系列集成电路结合51单片机[2]设计实现了基于倒计数器[3]的频率测量电路,辅以DDS(直接数字频率合成器)[4]构成雷达自动频率控制系统[5],已经成功应用于国产某型警戒雷达。

1 倒计数器频率测量及其组成的雷达自动频率控制系统

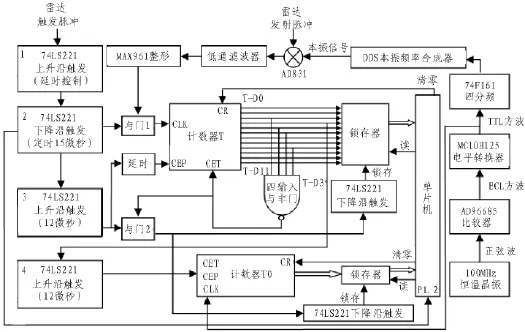

雷达发射机强大的射频输出功率对雷达的AFC(自动频率控制)系统的干扰是AFC系统电路设计时必须重视的问题。考虑到TTL集成电路的噪声容限大、且IC中的晶体管工作于饱和区,电路工作稳定,另外TTL集成电路的输入、输出阻抗都比较低,不易受周围杂散电磁场的干扰[1],所以在某型雷达的AFC系统设计中选用了TTL集成电路实现倒计数器频率测量,图1是系统的组成框图。

根据倒计数器频率测量的原理[3]和直接数字频率合成器的工作模式,系统选择ATMEL的51系列单片机作为控制核心,TTL集成电路完成计数、缓存、时序控制功能;由AD831将雷达发射机耦合来的发射脉冲和本振混频后取下变频,再通过MAX961对30 MHz左右的中频信号整形得到中频方波信号;时间基准选用100 MHz、正弦波输出的恒温晶体振荡器,频率稳定度达到5X10-9,经AD96685将100 MHz时钟信号的整形为ECL电平的方波再经MC10H125电平转换器转换成TTL电平的方波,一路直接作为计数基准,另一路经F161分频为25 MHz后作为DDS芯片的时钟信号。

图1 雷达自动频率控制系统框图Fig.1 Block diagram of radar automatic frequency control system

2 倒计数器频率测量电路的设计与实现

1)74F161 同步计数器的级联

161 是TTL系列电路中典型的4位二进制同步计数器,内部采用4个主-从J-K触发器作为记忆单元,可以多片级联构成多位计数器[1]。

在倒计数法测频电路中需要两个计数器,一个对被测脉冲信号计数,到规定的计数值即停止,形成一个时间长短未知但是脉冲个数已知的计数区间,在该区间内另一个计数器对已知的标准脉冲进行计数,根据计数结果即能计算出计数区间的时间长短,进一步求出未知信号的频率。

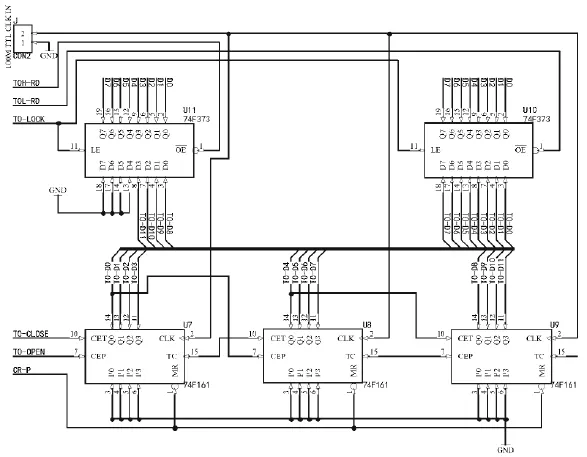

某型雷达发射脉冲持续时间仅13 μs,考虑到发射机振荡起始和结束时存在短时间的振荡不稳定,在发射脉冲持续时间内取中间的10 μs作为测量区间,对于雷达稳定工作时变频后的30 MHz第一中频脉冲信号而言正好是300个脉冲形成计数区间,所以需要3片161级联计数构成图1中的计数器T,同时该电路必须选用片间快速进位的快速计数级联电路[1],如图2所示。

图2 计数器T及其锁存电路Fig.2 Circuit of counter T and its latch

将图2中的计数器级联电路用于计数器T0时,计数时钟高达100 MHz,必须使用F系列的高速TTL芯片,即使如此,还是发现计数器出现时序竞争,导致计数不稳,经过仔细分析其电路连接和时序,对级联电路中的进位信号与第二片、第三片161的控制端的连接进行了更改,保证了100 MHz时钟条件下的稳定工作,图3是计数器T0实际使用的电路。

图3 计数器T0及其锁存电路Fig.3 Circuit of counter T0 and its latch

计数器T、T0虽然选用不同工作速度的161同步计数器,且级联电路有所改动,但其控制信号相同,有开、关、清零等操作,其中计数器的开、关由时序控制电路产生的控制信号控制,清零信号由CPU根据工作循环进程在适当的时候发出。

TTL系列的161计数器有两个控制端CEP和CET,只有当两个控制端同时为高电平时计数器工作,因此可以通过时序设计使用两个不同信号接到两个控制端,一个信号的上升沿控制开启,另一个信号的下降沿控制关闭。需要注意的是,从逻辑上看来个控制端功能一样,但是芯片内部的电路是有区别的,一般情况下建议使用CET作关闭信号,CEP作开启信号[1]。

2)时序控制

雷达的触发脉冲来自雷达的定时器,与单片机的晶振不相关,无法保持同步,所以倒计数器频率测量的时序控制全部用TTL电路实现并与雷达的触发脉冲保持严格的同步。图4是部分控制时序电路图,图5是控制时序图。

图5 控制时序图Fig.5 Diagram of sequence control

同型号的每一部雷达由于调制器和振荡器电路的细微差别会导致触发脉冲和发射脉冲之间的延时不同,因此由雷达的触发脉冲触发74LS221构成的单稳态触发器U23B(1号74LS221)对工作时序进行延时,对某一部雷达而言该延时一旦调整好一般不会再有变化,也可以通过适当延长延时时间切去振荡起始时的一段不稳定脉冲,但时间也不亦太长,要保证计数器的计数时间不少于10 μs。

U21A(2号74LS221)的单稳态触发器在U21B输出的下降沿触发,并延时形成15 μs宽的脉冲,该脉冲一方面通过U22A的与门打开中频方波脉冲将其送至计数器T的时钟引脚;另一方面送至CPU的P1.2引脚,CPU通过检测P1.2引脚的电平变化判断是否完成了一个雷达重复周期的测量过程;同时该信号还触发U21B(3号74LS221)的单稳态触发器形成一个宽度12 μs的脉冲用于打开计数器T的控制端CEP。

定时器T的另一控制端CET由四输入与非门的输出控制。单片机在复位后及每个重复周期中读取计数器数据后会对计数器清零,清零后计数器T的输出端将全部为零,即四输入与非门的输入端全为零,将使其输出为高电平,也就是计数器T的CET端为高电平,计数器T已经准备好,待CEP端变高电平即开始计数。

计数器T在其两个控制端均为高电平时开始对下变频后的方波中频信号计数,计到第8个脉冲时,计数器T的TD3引脚跳变为高电平,触发4号74LS221输出宽度为12微秒的高电平,此高电平打开计数器T0;计数器T计到第308个脉冲时,四输入与非门的4个输入端均为高电平,其输出变低电平,立即关闭了计数器T和T0。

为防止雷达发射机工作不稳时中频方波脉冲数量达不到308个而造成计数器T无法计数、四输入与非门无法产生低电平输出关闭T和T0,T和T0的CEP端均由74LS221定时12 μs,满12 μs将强制关闭计数器,保证整个工作时序能够周而复始地循环进行。

计数的结果分别通过4个锁存器锁存,锁存信号由计满308个脉冲的正常关闭信号和定时12 μs的强制关闭信号通过触发74LS221产生,先到者为准。4个锁存器通过单片机的数据总线将结果送入单片机,单片机通过地址总线上的3-8译码器为每个锁存器指定一个地址,依次分别读入计数结果。

3 单片机程序设计

雷达发射机的发射频率通常可以在一定范围内调整,其本机振荡器的输出频率也相应地有一个调整范围。单片机在上电复位以后首先对各计数器清零,再控制DDS在本振工作频率范围输出最低工作频率,等待雷达触发脉冲到来后通过倒计数测频电路进行一次测量,读入计数器计数结果后,判断中频信号频率是否为30 MHz。不是则在当前DDS输出频率值上增加一个步进值重复上述过程;是则维持该本振频率不变并继续在每个雷达脉冲重复周期进行测量,并根据测量结果适时调整本振频率。

单片机主要完成读取计数结果、计算发射频率并控制DDS频率合成器的输出频率和计数器复位的工作,测频电路的时序控制由雷达的触发脉冲同步,各计数器的启动、停止由单稳态触发器的输出脉冲宽度协调控制。单片机程序框图如图6所示。

图6 单片机的程序框图Fig.6 Block diagram of CPU program

4 结束语

倒计数测频电路中的计数器T对频率(周期)未知的脉冲序列进行计数,取其中300个脉冲的持续时间作为计数器T0的计数区间,此区间内计数器T0对100 MHz的时间基准脉冲进行计数。对某型雷达的稳定工作时30 MHz的第一中频而言,T0的计数结果应该为1 000个100 MHz脉冲,对应的计数区间为10 μs。当T0计数结果增加(或减少)一个脉冲时,意味着计数区间增加(或减少)10 ns,而这一变化是未知频率的中频信号的300个周期累加的变化,也就是中频信号的平均周期增加 (或减少)1/30 ns,对应的频率变化约30 kHz,此即为该测频电路的频率分辨能力,相对于雷达接收机约几百千赫兹的带宽而言,足够保证第一中频信号得到最有效的放大。

该倒计数器测频电路发挥了TTL集成电路的优点,用极低的成本实现了强电磁干扰下稳定的频率测量,达到了预期效果,对某型雷达战术技术指标的提升起到了良好作用。

[1]赵保经.中国集成电路大全TTL集成电路[M].北京:国防工业出版,1985.

[2]郭天祥.51单片机C语言教程—入门、提高、开发、拓展全攻略[M].北京:电子工业出版社,2010.

[3]曲卫振.时间频率的高精度测量方法[M].北京:系统工程与电子技术.1998.

[4]CMOS 300 MSPS Quadrature Complete-DDS AD9854.[R].Analog Device Inc.,2002

[5]丁鹭飞,耿富录.雷达原理[M].西安:西安电子科技大学出版社,2011.

[6]秦实宏.单片机原理与应用技术[M].北京:中国水利水电出版社,2005.

Design and implementation of frequency measuring circuit based on countdown counter

DU Xiao-yu1,XU Lian-xiang1,2,SHI Xiong1

(1.School of Electrical and Electronic Engineering,Wuhan Polytechnic University,Wuhan 430023,China;2.Key Laboratory for Advanced Technology in Environmental Protection of Jiangsu Province,Yancheng Institute of Technology,Yancheng 224000,China)

After down-conversion and shaping,the transmission pulse signal of radar turns to intermediate frequency TTL (Transistor-Transistor-Logic)square signal.This signal,on the basis of the frequency measuring principle of countdown counter,is counted by three pieces cascading of binary synchronous counter 74LS161.Three hundred pulses of the signal are chosen to form the counting section,in which the 100MHz standard square wave is counted by 74F161 with three pieces cascading.Then the result is loaded into MCU.The MCU works out current IF-RE and controls the DDS local frequency synthesizer to adjust the local output,in order that the frequency of IF signal is stabilized in the specified scope.The digital automatic frequency control system of radar is constituted.

countdown method;frequency measuring;synchronous counter;monostable trigger

TN952

A

1674-6236(2015)10-0109-05

2014-08-10 稿件编号:201408042

杜晓宇(1995—),女,湖北襄阳人。研究方向:电子信息。