基于FPGA的航空总线错误编码发生器设计

2015-12-13牛茜

牛茜

(山西机电职业技术学院,山西长治 046011)

基于FPGA的航空总线错误编码发生器设计

牛茜

(山西机电职业技术学院,山西长治 046011)

本文介绍了一款基于FPGA技术,针对于自主研发航空总线设备测试的曼彻斯特II型码错误编码发生器的设计。该编码发生器具备特定的终端号,以终端形式存在于总线系统中,它可以产生三种不同类型的错误编码,按总线控制器的要求向总线系统上的特定终端发送相应错误编码,以测试由不同设计者设计制作的终端设备在发送信息有误时的反应;便于整个航空总线系统功能的统一,具有很强的实践价值。

曼彻斯特II型码 1553B总线 FPGA

1553B总线是一种非常成熟且应用广泛的航空总线,随着电子技术的飞速发展,越来越多的设计者已经可以依托更新的科学技术,比如FPGA技术,挣脱少数国家的技术垄断,以航空总线协议为标准,自行设计功能多样的终端设备,以满足更多更高的要求[1]。但是更多的设计者的参与也意味着对总线系统测试的更高要求。本文介绍一款错误编码发生器的设计方法,该发生器可以生成完全符合1553B总线通信协议的三种不同类型的错误编码,应用于总线系统中,以测试自行研发的航空总线终端的标准性与实用性。

1 航空总线协议简介

1553B总线上数据的传输主要是依靠曼彻斯特II型码,每二十个比特位组成一个字,有命令、数据、状态三种不同类型。根据协议要求若干数量和种类的字组成不同类型的消息,消息发送至总线上,相应终端执行命令或是控制器得到终端回信,完成数据交流。该总线上数据传输速率是1Mbit/s,曼II型码用“01”表示逻辑0,用“10”表示逻辑1,如图1所示为曼II型码表示的“1000”。三种不同类型的的字虽然都是20个比特位的曼II型码,但是又各有不同,在这里不多加详述,详情可参照1553B总线通信协议[2]。

2 错误编码发生器FPGA设计

图1 Manchester II编码方式图

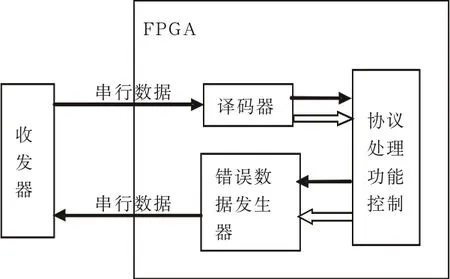

图2 错误编码发生器FPGA设计

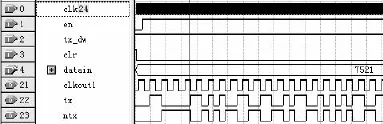

图3 同步头错误数据仿真图

图4 奇偶位错误数据示波器图

该设计在FPGA中的实现主要通过以下三部分,如图2所示:译码器、错误数据发生器和协议处理功能控制部分。当该设计以一终端形式接入待测试总线网络时,我们来分析一下数据的流向及处理情况[3]:该错误编码发生器以远程终端的形式存在于数据总线中,并且其具备特定的终端号码。当总线控制器发出命令,要求该终端发出某种类型的错误编码时,命令通过收发器进入FPGA中的译码器模块进行译码,并将命令字中的有效信息送至协议处理功能控制模块,在这一模块里分析命令字的有效数据,明了总线控制器要求终端发送一个什么类型的错误编码,我们把将要发送的错误编码的信息送入错误数据发生器,生成符合要求的曼彻斯特II型码,再经过收发器,最终发送至数据总线上。

3 实验仿真结果

设计者采用VHDL语言完成了FPGA中的逻辑设计,在相关软件中,对错误数据发生器模块进行了仿真,如图3所示,为产生同步头错误编码的仿真结果图。

在仿真之后,设计者使用Altium Designer6.0软件绘制了系统PCB板图,制作了该设计的电路板,进行了实验验证,示波器观测了发送至总线上的错误编码,如图4、图5所示。

4 结语

本设计采用FPGA技术,首次制作了可以产生错误曼彻斯特II型码的编码器,设计灵活,同时也有许多不足,如产生的错误编码类型少,不能产生错误的消息等。随着1553B总线的更广泛应用,更多的自主研发产品的出现,该款编码器将会得到广泛的应用,其功能也将会越来越完善。

[1]廖文彬.MIL-STD-1553B多功能总线测试卡的实现[D].成都:电子科技大学,2006.

[2]陕西恒立电子有限责任公司.美国军用1553B协议中文翻译资料.2000.

[3]牛茜.基于FPGA的1553B总线监测系统设计[D].太原:中北大学, 2011.

[4]夏宇闻.Verilog数字系统设计教程[第二版][M].北京:北京航空航天大学出版社,2008.

[5]DDC.Inc.ACE/Mini-ACE Series BC/RT/MT Inegrated 1553 Terminal User’s Guide.2005.

图5 数据位错误数据示波器图

牛茜(1986—),女,山西长治人,硕士,助讲,主要从事电子电气教学与研究。