基于FPGA的DDS信号源研究

2015-12-12郑丽娟

王 宁,王 梅,郑丽娟

(河北科技大学 信息科学与工程学院,河北 石家庄 050000)

基于FPGA的DDS信号源研究

王宁,王梅,郑丽娟

(河北科技大学 信息科学与工程学院,河北 石家庄 050000)

摘要:文中详细阐述了基于FPGA利用Quartus II实现DDS(直接数字频率合成器)模块的方法。根据DDS原理对其进行系统建模,采用verilog HDL语言实现各个模块的功能,并且在开发环境下进行了仿真。该信号源可以输出方波、三角波以及正弦波三种波形,其与传统的信号源相比较,具有波形质量好、精度高、设计方案简洁、易于实现、便于扩展与维护的特点。

关键词:直接数字频率合成器;信号源;现场可编程门阵列

0 引 言

频率合成技术是将一个或者多个基准频率转换成另一个或多个合乎质量要求的所需频率的技术。近几年随着FPGA等技术的发展使得DDS这种独特的结构得到了飞速的发展,并且在通信、雷达、导航等众多领域都有了广泛的应用[1]。DDS是以一个固定的频率精度的时钟作为参考时钟源通过数字信号处理技术产生一个频率和相位可调的输出信号,具有频率切换时间短、频率分辨率高、易于调整和实现等优点[2]。随着微电子技术和数字集成电路的飞速发展,以及电子工程领域的实际需要使得DDS逐步成为现代频率合成技术的佼佼者,具有广阔的应用前景。本文所使用的Verilog HDL是其中一种标准化的硬件描述语言。

1 DDS原理

1.1 DDS的基本原理

假设一个纯净的单频信号可以表示为:

(1)

只要它的幅度U和初始相位θ0不变,它的频谱就是位于f0的一条谱线。为了简化表示可令U=1,θ0=0,当然这也不会影响对频率的研究。即:

(2)

如果对此信号进行采样,采样周期为Tc,则可以得到离散的波形序列:

(3)

相应的离散相位序列为:

(4)

(5)

相应的模拟信号为:

(6)

1.2 DDS原理图

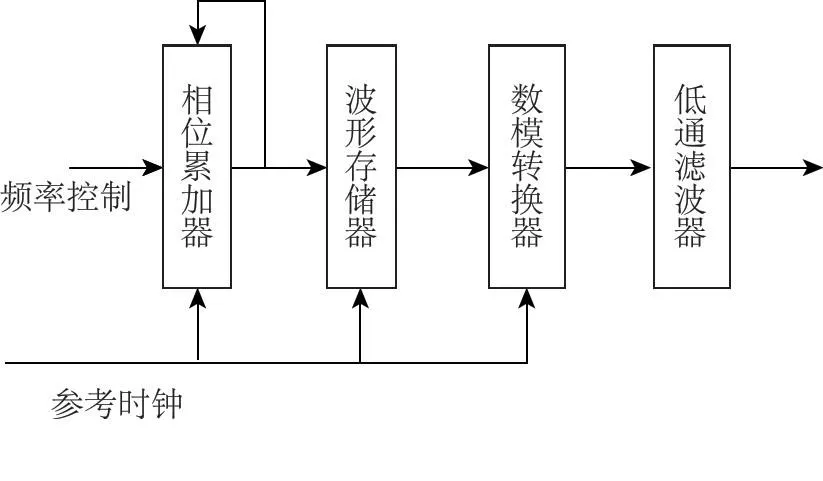

DDS实现频率合成主要是通过查找表方式进行的[3],如图1所示为DDS的原理图。DDS系统核心包括相位累加器和存储器,其中相位累加器由1个加法器和1个32位的相位寄存器组成,主要是用来实现线性数字信号的逐级累加;波形存储器中存储的主要是输出波形的幅度值,通过寻址读出数据进行波形的相位与幅度值的转换,从而完成信号的相位序列到幅度序列的转化。

图1 DDS原理框图

当频率合成器正常工作时,在标准频率参考源控制下,相位累加器则以步长K进行线性累加,输出的N位二进制码作为波形存储器的地址,对波形进行寻址,波形存储器输出的幅码经过数模转换器变成阶梯波形,在经过低通滤波器后得到平滑的波形。实际应用中,相位累加器的所有输出位并没有全部送到波形存储器中,一般只是截取了高几位,这样减少了查找表的规模又不影响系统的频率分辨率,但是会带来一定的杂散干扰。

2 用FPGA实现DDS

本文采用Altera公司的Quartus II软件进行设计,该软件根据设计者需要提供了一个完整的多平台开发环境并且支持多种设计方式。Quartus II支持的输入方式包括:原理图输入方式、网表文件输入方式以及文本输入方式。其中文本输入方式支持AHDL、VHDL和Verilog HDL 3种硬件描述语言,本文所用Verilog HDL语言具有行为描述的特点。

相位累加器主要是用来实现线性数字信号的逐级累加,如图2所示为相位累加器的模块符号。为了获得较高的频率分辨率,相位累加器的字长一般都比较大,而所采用的波形存储器的数据宽度一般为8位到16位,本文采用的是10位的数据宽度,因此波形存储器内存大小设置为1 024×10 bit,存储器模块如图3所示。波形存储器采用的是Altera公司提供的IP核(或称库函数),ROM的数据经过mif文件导入存储。存储好的数据通过程序中的相位累加器的累加、寻址读出。如图4为得到DDS的模块符号。

3 仿真实现

本文设置的时钟脉冲是500 ns,显示出的方波、正弦波和三角波等三种波形如图5。

图2 相位累加器的模块符号

图3 ROM存储器

图4 DDS的模块符号

图5 时钟脉冲为500ns的仿真波形

从图5可以看出通过读取ROM中的数据生成的波形中有很多毛刺,不平滑,这都是DDS杂散带来的影响,所以消除杂散也是研究的重要问题。

4 噪声和杂散分析

DDS的一个缺点就是较高的杂散电平。由于DDS采用的是全数字结构,不可避免地引入了杂散[4,5],其来源主要有:

(1)相位累加器相位舍位误差造成的杂散。如果将相位累加器的输出直接作为波形存储器的查找地址,那么存储器容量将非常大,在硬件上实现就会比较困难,所以采用了取高位输出低位舍去的方法,因此必然会造成误差。

(2)幅度量化误差造成的杂散。在实际设计中一个模拟量不可能用一串二进制代码来精确表示,而只能用N位二进制来表示近似值,这样就会产生幅度量化误差。

(3)DAC非理想特性造成的杂散。在实现过程中DAC存在非线性特性,输出信号就会产生谐波分量,导致频谱杂散的产生。

5 结 论

基于FPGA实现的DDS易于维护,实现方便,可以简单地完成几种波形的输出,通过改变频率控制字可以改变输出波形的频率,得到所需要的各种不同频率的波形。

参考文献:

[1]戎强.基于DDS/FPGA的多波形信号源的研究[D].哈尔滨:哈尔滨工程大学,2008.

[2]高琴,姜寿山,魏忠义.基于FPGA的DDS信号源设计与实现[J].西安工程科技学院学报,2006,(2):210-214.

[3]钟蔚杰,蒋垒,刘耀应.基于VHDL编程的DDS设计[J].舰船电子对抗,2007,(30):102-105.

[4]汤汗屏.直接数字频率合成杂散抑制方法的研究[J].电线技术,2008,(5):10-14.

[5]王晓音,聂裕平,庞伟正.输出频谱杂散的抑制[J].电子对抗技术,2008,(11):25-28.

王梅(1962-),河北科技大学副教授,研究方向为数字交换与传输;

郑丽娟(1988-),硕士研究生,研究方向为数字交换与传输。

研制开发

Study of DDS Signal Source Based on FPGA

WANG Ning,WANG Mei ,ZHENG Li-juan

(College of Information Science and Engineering, Hebei University of Science and Technology, Shijiazhuang 050000, China)

Abstract:This paper expounds the method of implementing DDS (direct digital frequency synthesizer) module by use of Quartus II based on FPGA. System modeling is firstly conducted according to the principle of DDS. The function of each module is then realized using verilog HDL language. And simulation under development environment is also done. The signal source can output square wave, triangle wave and sine wave, and have features of better wave quality, higher precision, more simple scheme, easier implementation, more convenient expansibility and maintenance when compared with traditional signal sources.

Key words:direct digital frequency synthesizer (DDS); signal source; Field-Programmable Gate Array(FPGA)

中图分类号:TN74

文献标识码:A

文章编号:1009-3664(2015)02-0038-02

作者简介:王宁(1989-),硕士研究生,研究方向为数字交换与传输;