基于SystemVerilog可重用测试平台的实现*

2015-12-07刘万和

王 鹏,刘万和,刘 锐,田 毅

(1.中国民航大学 民用航空器适航审定技术与管理研究中心,天津市民用航空器适航与维修重点实验室,天津300300;2.中国民航大学 安全科学与工程学院,天津300300)

基于SystemVerilog可重用测试平台的实现*

王鹏1,刘万和2,刘锐2,田毅1

(1.中国民航大学 民用航空器适航审定技术与管理研究中心,天津市民用航空器适航与维修重点实验室,天津300300;2.中国民航大学 安全科学与工程学院,天津300300)

对于中小型设计,传统的验证效率低、可重用性差,而基于方法学的高级验证测试平台搭建较繁琐,验证流程不太灵活。以ARINC429收发器IP核为验证对象,采用SystemVerilog语言,通过层次化设计,改善工程组织架构,运用虚接口与回调等关键技术,实现了一种可重用测试平台。将不同的测试案例在测试平台上运行,结合断言与覆盖率驱动等验证技术完成了对ARINC429收发器IP核的功能验证,代码覆盖率和功能覆盖率均达到100%。实践表明,该测试平台具有良好的可重用性、易操作性,验证效率较高。

验证;SystemVerilog;测试平台;可重用

0 引言

随着集成电路设计复杂性的增加,验证的难度也日益加大。传统的基于 Verilog的验证效率低、可重用性差,为此,工业界推出了具有面向对象特性、支持约束随机与断言等功能的标准化硬件描述与验证语言SystemVerilog[1]。

对SoC等大型设计的验证多采用基于方法学的验证进行,文献[2]基于 UVM建立测试平台对 RISC CPU进行验证,充分体现了基于方法学的验证对于大型设计的高效性。对中小型设计的验证,相对于基于方法学搭建的测试平台,基于SystemVerilog搭建的测试平台更具灵活性、易操作性[3]。文献[4]基于 SystemVerilog开发高级验证环境,实现了测试平台在定向测试和随机测试的重用,但对验证环境的配置实现介绍较少;文献[5]着重介绍了可重用测试平台的层次化结构及相应的验证组件,但缺乏对实现可重用性的关键技术的讨论。本文以层次化思想为指导,采用 SystemVerilog语言实现可重用测试平台。

1 可重用测试平台实现

1.1ARINC429收发器IP核简介

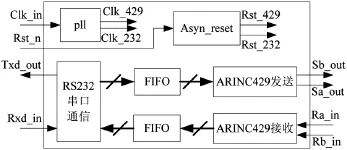

在现代飞机上,多采用ARINC429总线进行通信。根据 ARINC429总线规范[6],设计 ARINC429收发器,实现上位机与机载设备的通信,并将其IP化,便于复用。ARINC429收发器采用自顶向下的模块化设计,设计框图如图1所示。

图1 ARINC429收发器设计框图

ARINC429收发器的功能具体包括:(1)实现全局异步复位;(2)不同的速率模式通信;(3)异步FIFO的缓存;(4)发送器发送立即、循环数据;(5)发送器对接收的RS232数据正确处理;(6)发送器将RS232正确转换成ARINC429数据发出;(7)接收器正确处理接收的 ARINC429数据;(8)接收器将ARINC429数据转换成RS232数据发出等。

1.2可重用测试平台实现

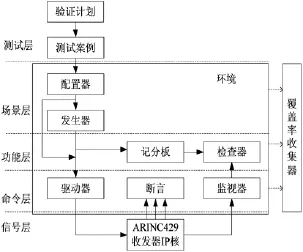

1.2.1测试平台层次化[7]

传统的采用Verilog实现的测试平台,设计者难以对测试环境进行分层设计,往往将大部分测试组件放在一个大的文件中,这使得测试代码难以维护、复用和扩展。所以 ARINC429收发器IP核的测试平台引入验证方法学中层次化的思想,结合设计规范与验证计划,采用SystemVerilog语言搭建层次化测试平台,如图2所示。

图2 收发器IP核层次化测试平台

ARINC429收发器 IP核测试平台结构自底向上为信号层、命令层、功能层、场景层和测试层等5个层次。测试平台的重用指的是验证环境的重用,即不同的测试案例能够重用同一验证环境。验证环境由包含配置器和发生器的场景层、包含记分板与检查器的功能层以及包含驱动器、断言和监视器的命令层组成。覆盖率收集器通过收集统计代码与功能点的覆盖信息可以衡量测试在满足验证计划要求方面的进展。

测试平台的顶层是测试层,根据验证计划开发不同的测试案例,通过信箱(mailbox)将信息传递到场景层;场景层中配置器为测试环境配置参数,通过将参数传递给发生器和驱动器实现环境参数的配置,发生器则根据收到的配置信息生成测试激励;功能层包含记分板和检查器,其中记分板主要包含参考模型,参考模型的输入为发生器生成的激励,输出传递到检查器,检查器通过对比记分板与监视器的输出信息来判断待测设计正确与否;命令层中驱动器接收发生器生成的测试激励与配置器的配置信息,并将激励驱动到待测设计ARINC429收发器IP核,断言和监视器用于监视DUT的相应输出;最底层信号层中待测设计 ARINC429收发器 IP核接收驱动器驱动的测试激励,并将输出传送到监视器。

层次化是测试平台实现可重用的基本结构,通过层次划分,将各验证组件按功能编成不同的类(class),便于重用、修改与扩展。

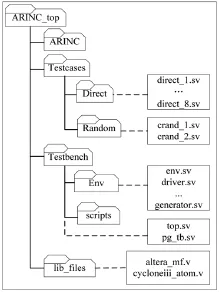

1.2.2工程组织架构

本验证工程采用层次化的组织架构,工程组织架构如图3所示。

图3 收发器IP核验证工程组织架构图

本验证实例中验证工程名为 “ARINC_top”,包含 4个主要的一级结构,即待测设计(ARINC)、测试案例(Test cases)、测试平台(Testbench)和待测设计的编译库文件(lib_ files)。测试平台(Testbench)包含测试环境(Env)与测试平台执行脚本(scripts)2个二级结构。测试案例(Testcases)包含2个二级结构:直接测试(Direct)和随机测试(Random),测试案例均以类的形式设计,在测试平台的顶层。测试平台执行脚本是以 TCL语言编写的扩展名为.do的文件,用于测试工程的文件组织与仿真进度的自动控制。

相对于标准的层次化工程组织架构,本架构做了改进。标准的层次化工程组织架构中,顶层模块中例化了环境类,环境类中包含了测试用例,这限制了添加和修改测试用例的灵活性,不利于测试平台的重用。本架构将测试用例从测试平台的结构中分离出来,用测试用例类代替验证环境类作为顶层的对象[8]。

这种层次化的组织架构为用户提供了一个开发直接测试、随机测试案例的可编程方法,有利于在整个测试平台结构上开发测试案例,实现测试平台最大的可重用。

1.2.3关键技术

在采用SystemVerilog语言实现 ARINC429收发器 IP核的可重用验证平台时,使用了以下关键技术:

(1)接口及虚接口

接口(Interface)简化了对端口信号的处理,封装了测试平台各组件间通信所需的信号,提高了设计可重用性。

在本验证实例的驱动类(Driver)中使用了虚接口,虚接口类型定义代码如下:

Typedef virtual if_arinc429.OUTP vif_429rx; Typedef virtual if_arinc429.INP vif_429tx;

通过使用虚接口,不必对每个通道都编写一个 Driver,而只需编写一个驱动类再将其例化多次即可,这极大地简化了工作,提高了验证组件的可重用性。

(2)回调

本测试平台运用了回调技术[9],回调流程如图4所示。

图4 回调流程图

验证实例在 Driver类中运用前回调技术[9]来为待测设计 ARINC429收发器IP核注入故障(100个数据随意丢弃1个),实现ARINC429接收错误的定向测试,不修改其他测试代码,实现了测试平台的最大可重用。

2 测试运行及结果

2.1测试运行

整个设计的测试激励主要由两部分组成:由计算机通过串口发出的数据,以及向ARINC429接收通道发送的数据。两部分激励是并行的,所以整个验证计划也是并行的。先进行定向测试,以保证验证过程具有一定的可复现性;然后进行随机测试,对待设计进行充分验证。通过对设计需求的深入分析后,得到如图5所示的验证计划。

图5 验证计划

使用Mentor Graphics的QuestaSim10.0c对ARINC429收发器IP核进行仿真测试。根据验证计划,编写了10个测试案例:(1)通道速率为高速的直接测试;(2)通道速率为低速的直接测试;(3)发送循环数据的直接测试;(4)发送立即数据的直接测试;(5)发送速率错误直接测试;(6)接收校验位错误的数据直接测试;(7)接收速率错误的直接测试,(8)最大速率下的流量测试;(9)发送随机测试;(10)接收随机测试。当测试不同的测试案例时,执行相应的脚本,实现自动化测试。

2.2测试结果

按照验证计划,先进行定向测试,在测试平台运行了8个直接测试案例,然后进行随机测试,在可重用测试平台上运行了2个随机测试案例。随机测试中ARINC429接收随机测试结果如图6所示。

图6 ARINC429接收随机测试结果

图6(a)为测试仿真波形图,图中三角形指示断言失败,因为这次接收随机测试中,发生器生成了校验位错误的数据,在ARINC429接收模块中该数据字被舍弃,断言检查器检测到两路输入数据不一致,即断言失败。这证明ARINC429收发器能按照设计要求舍弃错误数据,正确处理数据。图6(b)为代码覆盖率报告,rec429模块与afifo模块因为完备状态机下的default语句无法覆盖,故代码覆盖率没有达到100%,其他模块代码覆盖率均达到100%,功能覆盖率达到100%,符合测试要求。测试结果说明了在完成定向测试后,在该测试平台上能正常运行随机测试,完全实现了测试平台验证组件、验证环境的可重用。

为了提高验证效率,本测试平台还运用约束随机自动产生测试集,采用SVA断言实现错误的查找与快速定位,结合覆盖率驱动验证明确验证指标。10个测试案例的测试结果说明本测试平台完成了对ARINC429收发器IP核功能的高效验证。

3 结束语

本文以对ARINC429收发器IP核的验证为例,介绍了基于SystemVerilog的可重用测试平台实现。在简要介绍ARINC429收发器的功能与设计之后,详细介绍了采用 SystemVerilog实现收发器 IP核的可重用测试平台的层次化结构、工程组织架构以及技术方法;然后在验证计划的指导下,在该测试平台上运行定向测试和随机测试共10个测试案例,代码覆盖率与功能覆盖率均达到100%。结合断言、覆盖率驱动验证等技术完成了对ARINC429收发器IP核高效的、有效的功能验证。

在实际项目应用中,本测试平台不仅完成了对ARINC429收发器的功能验证,在修改少许代码后,还完成了对协议相似的ARINC629总线的验证。实践表明,本测试平台具有良好的可重用性。

[1]IEEE.IEEE standard for SystemVerilog-unified hardware design,specification,and verification language-IEEE 1800-2009[S].IEEE,2009.

[2]谢峥,王腾,雍珊珊,等.一种基于UVM面向RISC CPU的可重用功能验证平台[J].北京大学学报(自然科学版),2014,50(2):221-227.

[3]刘芳,谢峥,连志斌,等.一种可重构的通用总线接口验证平台的研究及实现[J].电子器件,2011,34(3):350-354.

[4]KEAVENEY M,MCMAHON A,O’KEEFFE N,et al.The development of advanced verification environments using System-Verilog[C].The 16th Signals and Systems Conference. ISSC 2008.Galway,Ireland,2008.

[5]山蕊,蒋林,李涛.基于SystemVerilog的可重用验证平台[J].电子技术应用,2013,39(5):128-131.

[6]Aeronautical Radio.ARINC specification 429[S].Aeronautical Radio Inc,2012.

[7]王鹏,邵伟,姜承翔,等.基于 ARINC629的层次化验证平台设计[J].计算机测量与控制,2014,22(6):1827-1829.

[8]钟文枫.SystemVerilog与功能验证[M].北京:机械工业出版社,2010.

[9]SPEAR C,TUMBUSH G.SystemVerilog for verification(3rd ed)[M].Springer,2012.

The implementation of a reusable testbench based on SystemVerilog

Wang Peng1,Liu Wanhe2,Liu Rui2,Tian Yi1

(1.Tianjin Key Laboratory for Civil Aircraft Airworthiness and Maintenance,Civil Aircraft Airworthiness Certification Technology and Management Research Center,Civil Aviation University of China,Tianjin 300300,China;2.Safety Science and Engineering College,Civil Aviation University of China,Tianjin 300300,China)

For small and medium-sized design,the traditional verification has low efficiency and poor reusability,while the advanced methodology-based verification is a bit complicated to build testbench,and the verification flow is not very flexible.The implementation of a reusable testbench is presented in this paper.The testbench is used to verify the IP core of ARINC429 transceiver,and it is implemented by employing the SystemVerilog language,designing the hierarchical structure,improving the architecture of project,and adopting key technology such as virtual interface and callback.With the assertions and coverage-driven verification technology,the functional verification is completed by running different testcases on this testbench,both code coverage and functional coverage are 100%.The practice shows that the testbench is reusable,easy to operate,and efficient.

verification;SystemVerilog;testbench;reusable

TN402

A

0258-7998(2015)02-0061-04

10.16157/j.issn.0258-7998.2015.02.013

国家自然科学基金(U1333120);中央高校基本科研基金(3122014D046)

2014-10-23)

王鹏(1982-),男,硕士,副研究员,主要研究方向:民机系统安全性设计与评估、机载电子硬件适航技术。

刘万和(1991-),男,在读硕士,主要研究方向:机载复杂电子硬件验证。

刘锐(1990-),男,在读硕士,主要研究方向:民机系统安全性设计与评估。