基于Xilinx FPGA lP核的浮点频域脉冲压缩算法的设计与实现

2015-12-05邢冠培孟凡利

邢冠培,孟凡利

(上海航天电子技术研究所,上海,201109)

基于Xilinx FPGA lP核的浮点频域脉冲压缩算法的设计与实现

邢冠培,孟凡利

(上海航天电子技术研究所,上海,201109)

脉冲压缩体制雷达的发射信号通常包括多种线性调频信号,这就要求对回波信号的脉冲压缩处理适应性要强,如果采用定点脉压,不同信噪比的回波信号脉冲压缩结果的截位各不相同,需要分别进行仿真测试,以确定截位的位置,而本文提出一种浮点频域脉压的算法及实现,基于Xilinx FPGA IP核,无需考虑截位,对各种信号适应性强,方便易用。

IP核;脉冲压缩;浮点;频域

0 引言

随着应对各种飞行器的性能提高,雷达也要求作用距离、分辨精度等指标得到相应的提高。雷达的作用距离取决于信号的时宽,即要求信号要有大的时宽,而雷达的分辨精度取决于信号的带宽,即要求信号要有大的带宽。但是对于单载频脉冲信号,时宽和带宽的乘积近似等于1,所以同时得到大时宽和大带宽是矛盾的。为了解决这一矛盾,必须采取同时具有大时宽和大带宽的复杂信号形式,最常用的就是线性调频信号(LFM),这种信号是在宽脉冲内附加载波线性调频,从而在大时宽的条件下扩展了带宽,通过脉冲压缩技术使宽脉冲变成窄脉冲,以获得高的距离分辨能力。

FPGA脉冲压缩处理可采用定点和浮点两种数据格式。采用定点数据格式,输入的动态范围较小,脉压结果精度不高,不能满足某些高性能雷达系统的需要。脉冲压缩包括时域脉压和频域脉压。频域脉压处理系统基于高效快速傅立叶变换,在处理大时宽信号时其设备量增加不大,对于带宽比较大的信号具有明显的优势。本文基于Xilinx FPGA IP核,实现了在频域内的浮点脉冲压缩的算法处理。

1 脉冲压缩技术原理

脉冲压缩实际上就是对接收信号进行匹配滤波处理。由于有多种发射脉冲形式,根据发射波形的不同,脉冲压缩时选择不同的匹配滤波器系数。数字脉压可用时域匹配滤波法或频域相关法实现。

时域数字脉压处理系统采用FIR滤波,通过对两个有限长度序列进行线性卷积而实现脉压处理,即将回波数据与匹配滤波器进行复卷积。滤波器复相关运算量随着信号时宽的增加而显著增加,完成运算所需的芯片量级也随之增加,因此,时域脉冲压缩处理较短时宽信号时在实现性及设备量上都具有良好的特点,但随着信号时宽增加,其设备量将增加。

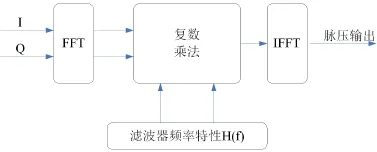

频域脉压处理是基于高效快速傅立叶变换,通过H(f)与线性卷积有限长度序列的FFT相乘,并将其乘积反变换至时域而获得脉压输出,即对回波数据进行FFT后,与匹配滤波器的系数进行复数乘法运算,然后再经过IFFT得到脉压输出后的数据。

本文脉冲压缩采用频域脉压方式,为抑制距离旁瓣,采用加窗的方式。假设输入信号为,则输出信号为

图1 频域脉压原理框图

图2 Floating-point IP核配置图

2 硬件实现

通过上述分析,频域脉冲压缩具体的工程实现大体分三个步骤:第一步是对输入脉冲信号进行傅里叶变换得到输入信号的频域信号;第二步是输入信号的频域值与预先存储的权系数进行复数相乘;第三步是将复数乘积做傅里叶逆变换得到时域上的输出信号。

通常脉冲压缩前的输入信号多为AD采样后经过数字下变频的定点值,如果以定点值经过上述步骤处理会带来一个问题,定点的位数会不断增加,以10位定点值,单个脉冲为1024点的输入信号为例,经过第一级FFT的输出值为21位,假设权系数为10位定点值,则经过第二级复数相乘的输出值为32位,再经过第三级FFT逆变换,最终输出值将达到43位。这样处理一方面消耗很多硬件资源,另一方面传输的带宽也可能不满足要求。因此,作定点脉压必须在每一级处理后进行截位处理,但是截位有可能会造成信号的损失,而且不同的信号可能截取得位置不同,这需要对具体的信号进行仿真验证,适应性比较差。而采用浮点脉冲压缩就不存在这个问题,所有的值都是32位,无论怎样处理都不会增加位数,也无需考虑是何种信号。

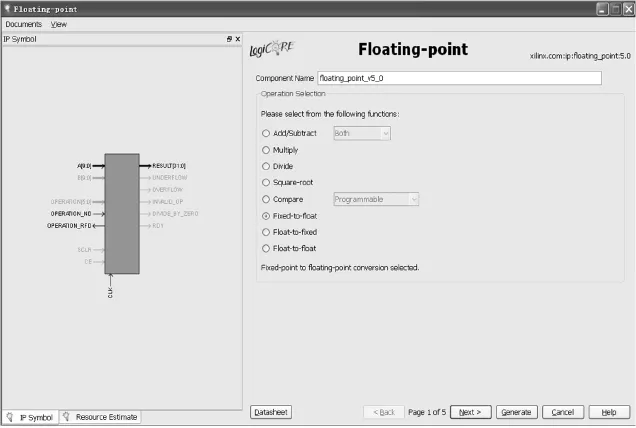

采用浮点脉冲压缩则需先将定点值转换为浮点值,再进行傅里叶变换和复数相乘等处理。因此,在FPGA实现中主要用到两个IP核:Floating-point IP核和FFT IP核。

Floating-point IP核可以实现定点转浮点,浮点运算等多种功能,如图2

通过选择“Fixed-to-float”可以实现定点转浮点的功能。通过选择“Add/Subtract”以及“Multiply”可以实现浮点数的加减法和与乘法,这个功能在第二级复数相乘中需要用到。

Floating-point IP核主要用到两个控制信号OPERATION_ND和 OPERATION_RFD,其中输入控制信号 OPERATION_ND置高表示当前输入数据有效。输出控制信号OPERATION_RFD置高表示当前输出数据有效。

FFT IP核主要实现傅里叶变换和傅里叶逆变换的功能。如图3

FFT IP核提供了四种不同的数据处理方式:(1)流(Streaming);(2)可变流(Variable Streaming);(3)缓冲突发(Buffered Burst);(4)突发(Burst);可采用基 4 算法或者基2 或者混合基算法;数据包括定点、块浮点和浮点等表示方法。

频域脉压选择“Pipelined, Streaming I/O”,即流模式,允许持续的数据进行流水处理。选择“Run Time Configurable Transform length”可是实现变长度脉冲压缩的功能。该IP 核主要用到的控制信号有如下几个

表 1 FFT IP核主要控制信号及功能描述

通过Floating-point IP核和FFT IP核,配合FIFO和 ROM,可以完全实现浮点频域脉压的处理,具体过程如下图

图3 FFT IP核配置图

图4 浮点频域脉压的处理流程

首先,AD采样后数字下变频得到的输入信号I、Q两路输入到定点转浮点的模块,通过“OPERATION_RFD”信号控制FFT模块的“START”信号启动傅里叶变换,当FFT模块的“EDONE”信号置高时表明下一个周期将输出FFT的有效值,这时应将权值的ROM地址置0,则在下一个周期第一个有效数据读出,第一个权值同时读出,两者相乘,并且在“EDONE”为低时,ROM地址是循环加1的,这样复数相乘就实现了流水运算。同样通过复数相乘模块的“OPERATION_RFD”信号控制IFFT模块的“START”信号启动傅里叶逆变换,当“DV”置高时表示,脉冲压缩的有效数据输出,该数据可以送到MTI、MTD、恒虚警或者成像等后续模块中继续处理了。

3 工程测试与验证

脉冲压缩模块采用Xilinx V5系列 FPGA芯片,将带宽为5M,时宽为133us的线性调频信号输入到系统中,通过Chipscope采集脉压后的数据并导入到Matlab进行分析,所得结果如图5所示。

Design and implementation of a floating-point frequency domain pulse compression algorithm based on FPGA IP Xilinx kernel

Xing Guanpei,Meng Fanli

(Shanghai Institute of aerospace electronics technology,Shanghai,201109)

Pulse compression radar transmitting signal usually includes a variety of linear FM signal, which requires the echo pulse compression processing adaptability stronger,if the point pulse pressure and different signal to noise ratio of the echo signal pulse compression results truncate each are not identical,necessary to simulation test,to determine the truncation of the position,and in this paper,a floating-point pulse compression in frequency domain algorithm and implementation, based on Xilinx FPGA IP core,without considering the truncation and adaptability to various signal is strong,easy to use.

IP kernel;pulse compression;floating point;frequency domain