放射性α气溶胶监测仪数据采集系统的设计

2015-12-02夏晓彬张志宏陈明明涂传火

陈 峰 夏晓彬 张志宏 蔡 军 陈明明 涂传火

放射性α气溶胶监测仪数据采集系统的设计

陈 峰1,2夏晓彬1张志宏1,2蔡 军1陈明明1涂传火1

1(中国科学院上海应用物理研究所 嘉定园区 上海 201800)

2(中国科学院大学 北京 100049)

在核设施的工作场所中要求对放射性α气溶胶进行快速、连续的监测,以保护工作人员的辐射安全。针对放射性α气溶胶的监测需求,介绍一种放射性α气溶胶监测仪多通道数据采集系统的设计。该系统采用现场可编程门阵列(Field Programmable Gate Array, FPGA)为控制核心,完成对A/D转换器、数据存储器、数据通信等模块的控制。将采集的数据放入到存储器中,实现了对探测系统产生的电压脉冲信号的连续采样,并进行模拟仿真和采样实验的验证。实验结果表明,该数据采集系统能实时、快速、高精度地完成对信号幅度的获取,满足了放射性α气溶胶监测仪的要求。

α气溶胶,现场可编程门阵列,数据采集,A/D转换,高精度

在反应堆等核设施的工作场所中,由长寿命的α放射性核素及其衰变子体所形成的放射性气溶胶是造成工作人员内照射的主要来源,严重威胁人员的职业健康安全。因此,对核设施工作场所进行放射性α气溶胶的快速、实时监测,可以有效地监控工作场所的放射性污染程度,保护工作人员的辐射安全。

放射性α气溶胶监测仪主要由采样系统、测量系统、报警系统和数据采集系统组成[1],其中高速数据采集系统能够获取测量系统中探测器所产生的电子学信号,是放射性α气溶胶监测仪的一个重要组成部分,对整个监测仪功能的实现具有至关重要的作用。

目前常用的数据采集系统主要是以单片机或者数字信号处理器(Digital Signal Processor, DSP)为控制器,控制模数转换器(Analog to Digital Converter, ADC)、存储器和其他外围电路的工作。

其中,以单片机为控制核心的数据采集系统根据用户的需求对采集到的信号进行高精度A/D转换处理。但是由于单片机自身工作频率较低和实行的指令周期较长,从而影响数据处理的速度,并且随着程序量的增加,很难满足数据采集的快速和实时性要求。

而以DSP为控制核心的数据采集系统具有较快的运算速度而且擅长处理密集的乘加运算,在数字信号处理方面运用广泛。但是DSP器件的管脚配置不够灵活,很难完成对外围复杂器件进行的逻辑控制,其开发成本也相对较高[2]。

相对于单片机和DSP而言,现场可编程门阵列(Field Programmable Gate Array, FPGA)具有时钟频率高、内部延时小、扩展方便、I/O资源丰富等优点[3],能够实现电子学信号的高速数据采集与处理。

本文以FPGA为数据采集系统的控制核心,采用“FPGA+ADC+SDRAM (Synchronous Dynamic Random Access Memory)”的实现方案,并采用RS485通信协议,设计放射性α气溶胶监测仪数据采集系统,以实现对探测信号的高精度、实时性采集与处理,同时保证数据采集具有长期稳定性、较高的可靠性和较快的响应速度。

1 设计要求

根据放射性α气溶胶监测仪的设计,放射性α气溶胶的测量选用有效面积900 mm2的离子注入型钝化平面硅(Passivated Implanted Planar Silicon, PIPS)探测器。探测器的耗尽层厚度不小于250 μm,对能量为3−8 MeV的α粒子的本底计数率为0.05count·h−1·cm−2,匹配高压模块和电荷灵敏前置放大器,进而组成放射性α气溶胶测量系统,其输出电压脉冲幅度极值120 mV,上升沿小于2 μs,因此放射性α气溶胶监测仪的数据采集系统需要满足以下功能要求:

(1) 信号采集与处理:能够实时、准确采集探测系统的输出电压脉冲信号幅值,并能将采集到信号进行数据转换处理;

(2) 数据储存:对处理之后的数据能够进行长时间存储,确保储存的数据不能丢失;

(3) 数据传输:快速、及时将数据传输到上位机进行终端显示。

2 系统组成

放射性α气溶胶监测仪的数据采集系统由FPGA控制模块、A/D转换模块、数据存储器模块和数据通信模块组成。其中,FPGA是系统的控制逻辑,控制ADC进行数据采样,并将采样数据经过缓存后送到大容量SDRAM中存储,A/D转换器的作用是将采集到的采样模拟信号经量化和编码后转换为计算机可识别的数字信号并输出,数据存储器对A/D转换后的数据进行存储和读取。数据通信模块主要实现数据采集系统与上位机进行通信,将采集的数据存储在上位机文件中,便于数据的查询与分析。

各模块与FPGA芯片相连实现数据采集(Data Acquisition, DAQ)功能,如图1所示。由图1,当系统上电开始工作时,将程序存储器中的固化数字逻辑电路加载映射到FPGA芯片中,使得FPGA成为控制核心。探测系统产生的电压脉冲信号传输至A/D转换模块,将FPGA内部的时钟信号进行分频,使得采样频率满足A/D转换的要求,这样A/D转换芯片能够正常工作,A/D转换结束后,将采集到的数据经过缓存后传送到SDRAM中,当采集完成后,上位机通过通信接口发送数据传输命令给FPGA,FPGA停止对数据的采集,开始将SDRAM中缓存数据通过通信接口传输给上位机,当传输完毕后,上位机再通过通信接口停止发送数据采集命令。

图1 数据采集系统结构框图Fig.1 Diagram of the DAQ system.

2.1 系统硬件设计

2.1.1 FPGA控制模块

FPGA是一个含有可编辑元件的半导体器件,通过编程并加载到其中的逻辑程序进而控制外部电路[4]。FPGA芯片的选择需要根据实际系统中的模块所用的逻辑资源、系统的最高时钟频率、连接的外围器件所需要的IO管脚数来确定[5]。本设计要求有较高的时钟频率和强大的数据处理能力,选用美国Altera公司的Cyclonell系列芯片EP2C8Q208C8作为核心处理器进行设计。EP2C8Q208C8是面向逻辑密集型设计的FPGA芯片,具有丰富的逻辑资源,有8256个宏单元,最高工作频率达155.5 MHz,从内部资源和时钟频率上完全符合系统的设计要求。

FPGA控制模块主要功能:(1) 通过内部PLL时钟产生模块,对外部时钟做分频处理后供内部的逻辑使用;(2) 对通过ADC678模数转换芯片产生的12位数字信号进行采集输入至FPGA中,经内部FIFO缓冲的数据再存储到SDRAM;(3) 为ADC678提供数据的采样时钟和同步信号,又对SDRAM进行读写控制;(4) 提供SDRAM芯片到RS485接口的数据通道,将数据通过RS485传输到上位机。FPGA内部逻辑结构如图2所示。

图2 EP2C8Q208C8内部逻辑结构Fig.2 Internal logical structure of EP2C8Q208C8.

2.1.2 A/D转换模块

由于FPGA本身不具备模数转换模块,必须使用外加的A/D转换电路才能使模拟信号转换为数字信号,本文根据系统的采集精度和速度,综合考虑采用AD678作为A/D转换芯片。AD678是一个高档、多功能的A/D转换器,内部含有采样/保持器、高精度基准电源、内部时钟和三态缓冲数据输出等部件。因此,它只需很少的外部原件就可以构成完整的数据采集系统,一次A/D转换仅需要5 µs,提供了相当强的功能[6]。

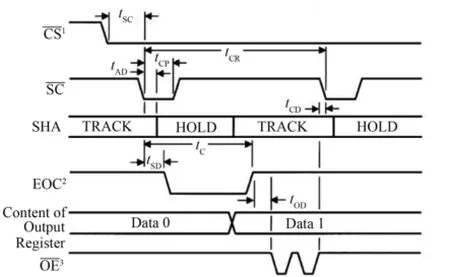

AD678采用先进的设计技术,是一款12位高精度、高速、低功耗的带采样保持功能的ADC,采用TTL输出电平,模拟信号输入电压0−120 mV,其动态范围为72.25 dB,满足探测器测量系统的输出信号动态范围和精度要求,转换误差1 LSB。AD678的转换时序如图3所示,两次A/D转换的时间间隔TCR=5 µs。

图3 AD678转换时序图Fig.3 Conversion timing of AD678.

A/D转换开始后,EOC下降为低电平,故在A/D转换过程中,EOC保持低电平,A/D转换完成后,EOC变成高电平,故EOC可以作为标志位,通知FPGA转换结束。其时序如图4所示。

图4 EOC时序图Fig.4 EOC timing.

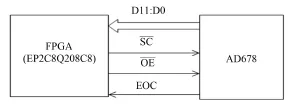

AD678与FPGA采用ADC接口进行通信,在异步工作模式下,FPGA给一个负脉冲信号即可启动AD678,模拟信号被采样,此时EOC输出为低电平,标志着模数转换正在进行。当其输出变成高电平时,数据转换结束,转换数据在OE控制下并行输出DB[11:0]。AD678与FPGA接口见图5。

图5 FPGA与AD678接口图Fig.5 Interface of FPGA and AD678.

2.1.3 数据存储器模块

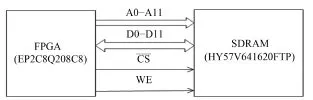

数据存储器用来对AD678采集后的数据进行存储和读取,本系统用一片外部SDRAM芯片,其容量为64 Mbit,具有高容量、快速、高数据吞吐率等优点。SDRAM与FPGA的接口原理如图6所示。A0−A11为地址信号,与FPGA端口SA0−SA11相连,D0−D11为数据总线,CS为片选信号,低电平有效,WE为存储器的读写信号,低电平有效。

图6 FPGA与SDRAM的接口图Fig.6 Interface of FPGA and SDRAM.

2.1.4 数据通信模块

通信模块采用串口通信,主要负责将SDRAM中存储的数据读取出来传送给上位机,由上位机对接收的数据进行存储、处理、分析、显示等,串口通信是计算机主机与外设之间数据的串行发送,是一种通用的设备通信协议[7]。

数据采集系统在数据通信时通过光耦合器隔离器件与上位机进行通信,光耦合器的主要优点是单向传输信号,输入端与输出端完全实现了电气隔离,抗干扰能力强,使用寿命长,传输效率高。串口通信标准选用RS485协议[8]。

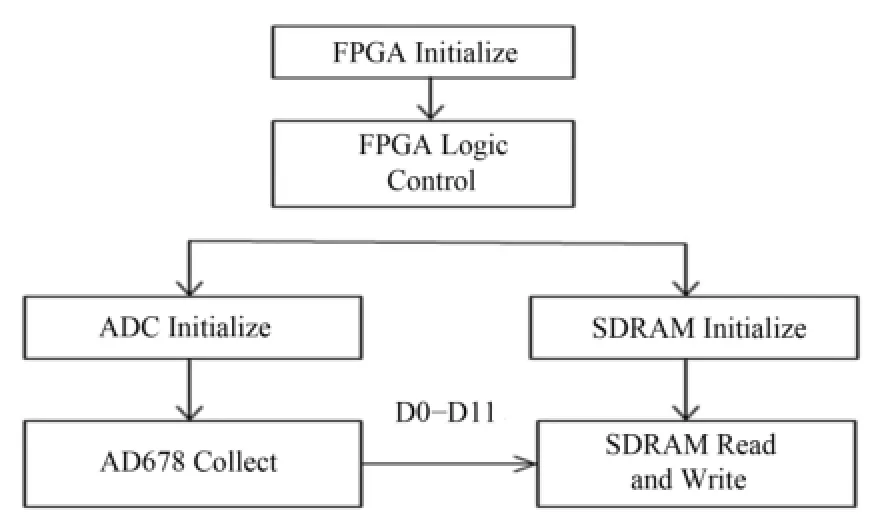

2.2 系统软件设计

利用硬件描述语言来完成数据采集、存储、传输数据至PC机是本设计重要的环节,采用合理的时序逻辑协调各模块间的工作才能保证数据采集系统的正常工作。各模块全部由时序逻辑产生控制操作,其流程图见图7。首先对FPGA进行初始化,通过FPGA逻辑控制ADC芯片和SDRAM将采集、存储的数据通过通信接口传输数据,上位机发出传输数据的命令,将数据发送至上位机,整个时序逻辑控制采用硬件描述语言Verilog语言编写实现。

图7 系统逻辑流程图Fig.7 Logic chart of the system.

3 系统测试

在核辐射探测器中,带电粒子和物质相互作用使物质中的原子电离和激发都是随机的,存在统计涨落[9],在放射性气溶胶α粒子进入PIPS探测器的灵敏体积时,电子空穴对数目的统计涨落规律使PIPS探测器的输出信号幅度、形状、前后脉冲间隔不均匀,满足不同的随机分布,并且使得实际测量得到的脉冲谱和理论上存在差异。

根据这一系列特点,本文对数据采集系统前端探测系统产生的信号进行数学模拟,分析输出仿真信号,通过建立数学模型仿真并与实验结果进行比较,验证探测系统测量结果准确性。为验证设计的数据采集系统是可靠稳定的,通过数据采集系统对探测器信号进行A/D转换得出脉冲信号,最终得到放射性α气溶胶能谱。

3.1 数据采集测试

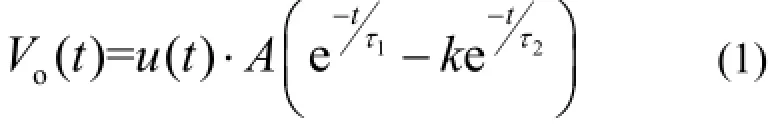

放射性气溶胶监测仪探测系统PIPS探测器输出信号为微弱的电压脉冲信号,经过前置放大器进行核信号放大。其输出信号可用双指数模型进行近似描述为:

式中,u(t)表示阶跃函数;k为比例系数;τ1、τ2分别是双指数信号慢时间常数和快时间常数,前置放大电路的输出信号上升时间和衰减时间由τ1、τ2共同决定。为更好地描述探测系统的输出信号,对此信号进行数学模拟仿真。取不同的τ1、τ2,k取1,运用MATLAB仿真工具得到输出波形如图8所示。

图8 探测系统输出信号仿真图Fig.8 Output signal simulation map of the detection system.

通过测量得到探测系统信号波形如图9所示。由图9可见,前置放大器最终输出信号幅值极值约为120 mV,在4 µs内信号衰减为0,与图8仿真结果类似,可以得出与信号数学模拟相一致,符合实际情况,能够满足数据采集系统采集要求。

图9 实测信号波形图Fig.9 Measured signal waveform.

由于探测系统产生的信号周期恒定,将采集到的信号经过ADC通道,在FPGA控制下将信号调节适当的采样频率,使得ADC进行A/D转换,得到一系列脉冲信号,最终得到在一定测量时间内放射性净计数,实现了对探测器电子学信号的实时数据采集。

3.2 实验测试

在实验室本底条件下,放射性α气溶胶监测仪通过气泵以一定速率从样品气体中抽取部分,经过滤膜后将空气中的一定粒径的放射性气溶胶沉积在滤纸上,通过对其测量得到人工放射性核素与天然本底核素的α能谱,如图10所示。

图10 人工放射性核素与天然本底核素的α能谱Fig.10 α spectrum of radionuclides and natural background radionuclides.

气溶胶中人工α放射性的测量采用能量甄别修正法,需要监测的人工α放射性气溶胶能量与天然本底氡、钍子体的α射线能量是不同的。采用具有能量分辨本领的半导体探测器进行甄别就可以通过能量甄别的方法将他们加以区分。测量能谱中有三个天然本底的α能峰,依次为212Bi(220Rn的衰变链)6.05 MeV的α粒子和218Po(222Rn的衰变链)6.00 MeV的α粒子的叠加能峰;214Po(222Rn的衰变链)7.68 MeV的α粒子能峰;212Po(220Rn的衰变链)8.78 MeV的α粒子能峰。可见,数据采集系统可以有效分辨出天然本底的α能峰,实现了放射性α气溶胶的实时监测。

4 结语

本文根据放射性α气溶胶监测仪的设计要求,以FPGA为数据采集系统的控制核心,采用

FPGA+ADC+SDRAM的方法,开展了放射性α气溶胶监测仪数据采集系统的设计。通过对探测系统产生的电压脉冲信号进行高速ADC采集实验和在环境本底下开展的实验室测试,可以看出数据采集系统能够对采集到的信号进行A/D转换和数据采集,实现对探测器电子学信号的实时采集,并且在环境本底下可以有效分辨出天然本底的α能峰,实现放射性α气溶胶的实时监测。在今后的工作中,将继续优化放射性α气溶胶监测仪数据采集系统的设计。

1 孙发力. 放射性β气溶胶探测器的数值模拟与探测系统设计[D]. 北京: 中国科学院研究生院, 2011

SUN Fali. Simulation and electronic circuit design of detector for beta radioactivity in aerosol[D]. Beijing: Graduate School of Chinese Academy of Sciences, 2011

2 肖积涛, 马幼鸣. 基于FPGA的高速数据采集系统的设计与实现[J]. 计算机技术与发展, 2012, 22(6): 217−220

XIAO Jitao, MA Youming. Design of high-speed data acquirsition system based on FPGA[J]. Computer Technology and Development, 2012, 22(6): 217−220

3 翟伟, 纪元法. 基于FPGA的高速数据串口采集系统设计[J]. 桂林电子科技大学学报, 2013, 33(4): 275−278

ZHAI Wei, JI Yuanfa. Design of a high-speed serial data acquisition system based on FPGA[J]. Journal of Guilin University of Electronic Technology, 2013, 33(4): 275−278

4 杜慧敏, 赵全良. 基于Verilog的FPGA设计基础[M].西安: 西安电子科技大学出版社, 2006: 1

DU Huimin, ZHAO Quanliang. Based on the FPGA design basis of Verilog[M]. Xi'an: Xi'an University of Electronic Science and Technology Press, 2006: 1

5 韦存刚, 金星. 基于FPGA的多路数据采集和控制模块设计[J]. 微计算机信息, 2008, 24(17): 231−232

WEI Cungang, JIN Xing. The design of a multichannel data acquisition and control module based on FPGA[J]. Microcomputer Information, 2008, 24(17): 231−232

6 马明建. 数据采集与处理技术[M]. 第二版. 西安: 西安交通大学出版社, 2011: 94−96

MA Mingjian. Data acquisition and processing technology[M]. 2ndEd. Xi'an: Xi'an Jiaotong University Press, 2011: 94−96

7 郭树涛, 靖永志. 基于FPGA的串口通讯设计[J]. 北京电子科技学院学报, 2006, 14(4): 74−78

GUO Shutao, JING Yongzhi. Serial communication based on FPGA[J]. Journal of Beijing Electronic Science and Technology Institute, 2006, 14(4): 74−78

8 周韧研, 商斌. Visual C++串口通信开发入门与编程实践[M]. 北京: 电子工业出版社, 2009: 47

ZHOU Renyan, SHANG Bin. Introduction to Visual C++ serial communication development and programming practice[M]. Beijing: The Electronics Industry Press, 2009: 47

9 汪晓莲. 粒子探测技术[M]. 合肥: 中国科学技术大学出版社, 2009: 67

WANG Xiaolian. Particle detection technology[M]. Hefei: University of Science and Technology of China Press, 2009: 67

CLC TL816+.2

Design of data acquisition system for radioactive α aerosols monitor

CHEN Feng1,2XIA Xiaobin1ZHANG Zhihong1,2CAI Jun1

CHEN Mingming1TU Chuanhuo1

1(Shanghai Institute of Applied Physics, Chinese Academy of Sciences, Jiading Campus, Shanghai 201800, China)

2(University of Chinese Academy of Sciences, Beijing 100049, China)

Background: In the workplace of the nuclear facilities, radioactive α aerosols monitoring in a fast, continuous way is required for protecting workers against radiation exposure. Purpose: Based on concentrations level of α aerosols in the workplace, α aerosol monitor was designed. The overall design scheme of the data acquisition system of the radioactive α aerosol monitor was introduced. Methods: A Cyclonell series FPGA (Field Programmable Gate Array) chip EP2C8Q208C8 from Altera corporation was applied as the control core to complete the A/D converter of AD678, data storage, and data communication with remote computer via RS485 interface. The sample data was stored in the data memory of 64 Mbit SDRAM (Synchronous Dynamic Random Access Memory) for continuous and fast sampling. Both the numerical simulation and experimental measurements were carried out to verify the reliability of the data acquisition system. Results and Conclusion: Results show that the data acquisition system can acquire and control the detector signal for the radioactive α aerosols monitor in real-time, high-precision and fast-speed.

α aerosols, FPGA, Data acquisition, A/D conversion, High precision

TL816+.2

10.11889/j.0253-3219.2015.hjs.38.060401

中国科学院战略性先导科技专项(No.XDA02005002)资助

陈峰,男,1988年出生,2011年毕业于安徽大学,现为硕士研究生,辐射探测系统开发

夏晓彬,E-mail: xiaxiaobin@sinap.ac.cn

2015-01-28,

2015-03-06