一种减小VDMOS反向传输电容的新结构

2015-11-30陈利

摘 要:利用高能离子注入与JFET注入结合的技术,设计了一款可以减小反向传输电容的P阱深结新型结构VDMOS器件。深结扩散提高了器件的击穿电压和稳定性,更短的栅极减小了形成反向传输电容的有效多晶硅栅长度,电容面积的减小从而降低了VDMOS的反向传输电容,同时优化JFET注入来解决由深结导致导通电阻增加的矛盾,采用 A T H EN A和 A T LA S工具对器件参数仿真优化。芯片流片测试结果表明这种新型结构能有效减小VDMOS的反向传输电容、提高开关速度和动态性能。

关键词:VDMOS;深结;高能离子注入;反向传输电容

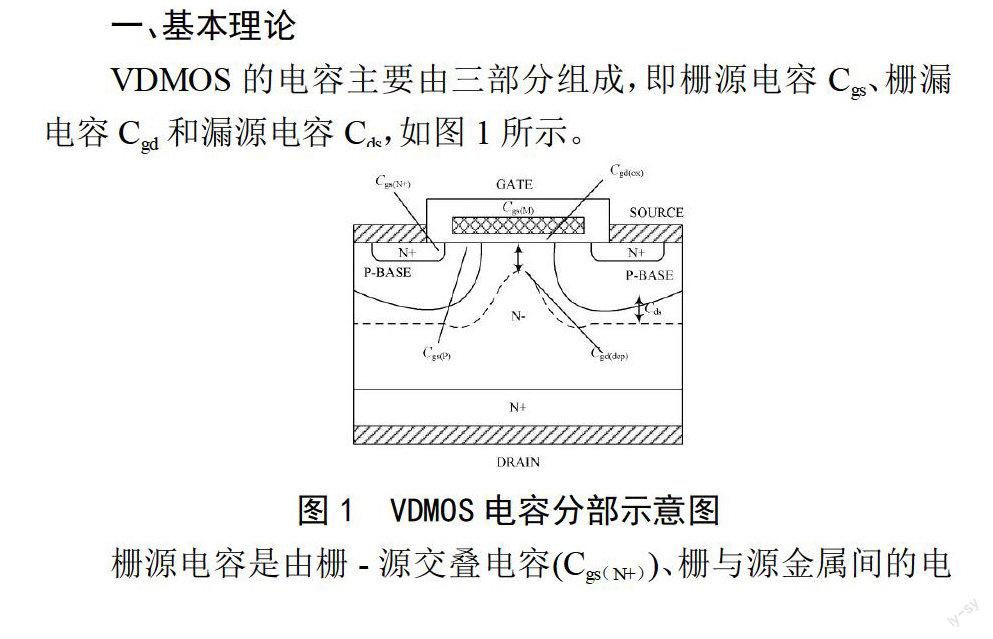

引言:功率垂直双扩散金属氧化物场效应晶体管(VDMOS)比双极型功率器件开关速度高、输入电阻高、驱动电流小、频率特性好,已广泛应用于高频功率电子技术领域[1]。VDMOS的主要作用之一是在开关电源中作为开关器件提高系统工作频率,开关电源的工作频率的提高可以有效较少电源体积和重量,同时降低开关损耗。但提高开关工作频率则要求VDMOS有快的开关速度,而VDMOS的开关速度主要是由它的本征电容和寄生电容决定[2][3]。电容的充放电过程是限制其开关速度的主要因素,尤其是反向传输电容,它的米勒效应对器件的开关特性有着重要的影响,对开关速度起支配作用。因此在VDMOS设计中减少反向传输电容就显得格外重要。

为减小反向转换电容,研究学者提出了一些VDMOS结构。文献提出在VDMOS中间区域断开多晶硅,同时在断开处注入P型区,改变VDMOS栅极下耗尽区的形状,然而这种做法需要增加工序和精确严格的工艺控制,比较复杂也提高了芯片成本。文献报道用二氧化硅将栅极多晶硅从中分成两部分然后在氧化层正下方的外延中注入一层与外延相同的高浓度杂质,这种做法降低了栅电荷,然而增加了导通电阻。因而对于高压高频VDMOS解决寄生电容、导通电阻和器件耐压三者的矛盾,目前还是设计上的一个难点。

本文提出一个新的VDMOS结构,降低了反向传输电容,优化导通电阻,同时提高耐压稳定性。首先介绍了反向传输电容减少原理;其次设计了新结构VDMOS,并对参数优化仿真;最后对流片制造出的新器件进行相关电特性测试。

二、器件设计与仿真

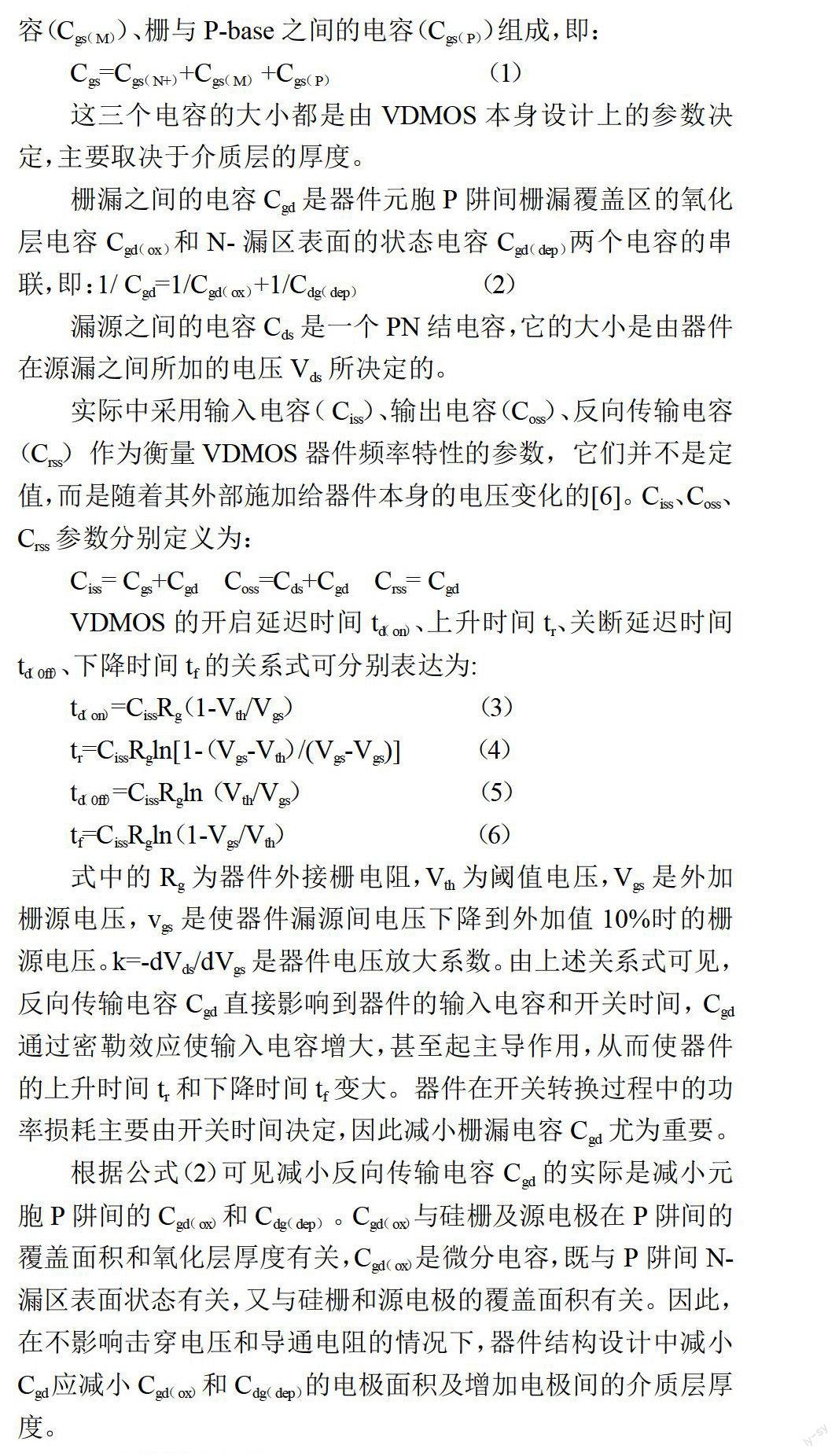

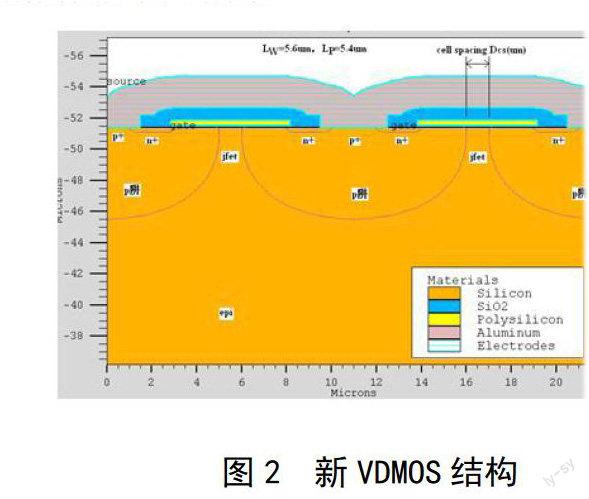

基于上述理论分析,本文采用高能量离子注入的方法,将P阱扩散为深结,获得短栅结构,减小了多晶硅栅长度,那么对形成反向传输电容起作用的有效多晶硅栅的长度也会减小,在相等栅极宽度(W)下Cgd (ox) 和Cdg (dep )的电容面积减小,则Cgd (ox) 和Cdg (dep )都减小,因此,反向传输电容Cdg大大降低。本文选用耐压为600V级别的传统VDMOS结构器件基础上设计新器件,其结构剖面图如图2所示。

图2 新VDMOS结构

(一)P阱结深的影响。P阱结的深度对器件耐压、导通电阻、元胞间距都会有影响。高能离子注入的横向扩散比普通离子注入明显,因此在获得同等有效沟道长度(即有效栅极)的情况下,可以将多晶硅长度做的更小,这样元胞面积也可以减小,芯片利用率提高,从而降低器件制造成本。为了防止横向扩散过大,导致元胞重叠JFET区域消失,需要选择适当的P阱注入窗口和退火条件,在不改变其他参数的基础上,本文P阱注入窗口选为2um,通过改变P阱注入的时间长短来获得不同深度的P阱结深,注入时间则越长P阱越深,采用ATHENA (工艺模拟)和ATLAS(器件模拟)工具进行仿真,仿真得到结果如表1所示。

表1 P阱结深的影响仿真结果

从理论上分析,P阱结越深,元胞间距(cell spacing)则越小,当漏极加偏压后,P阱/N-外延耗尽区将迅速连起来类似于平面结,使得器件耐压比较理想而且稳定,表1的仿真结果也很好的验证了这点。但是单元间距减小会使的JFET效应增强[8],导致JFET区的电阻急剧增大,影响了器件的驱动能力,即表1中显示导通电阻偏大,所以需要对cell spacing进行优化仿真。

(二)优化JFET离子注入。通过JFET的离子注入可以改善导通电阻的特性,根据表1选取P阱离子注入浓度为5E14cm-2 ,退火为1200℃ 100min N2/LwO2的条件下。选用不同浓度的JEFT离子注入,仿真结果如表2所示。从表2中也可以看出,JFET离子注入越大,可以更有效的降低导通电阻,但一定程度也会影响到器件耐压值,综合考虑最终选取JFET注入时的浓度为2E12cm-2。

表2 JFET离子注入的影响仿真结果

(三)有源区注入窗口( LW)、栅极长度(LP)的优化。当元胞(cell)长度、面积、各掺杂浓度相同的情况下,影响耐压的参数主要是有源区的注入窗口[9][10](LW)、栅长(LP),对LW、LP的不同参数优化组合仿真结果如表3所示。从结果中分析,由于P阱的注入窗口宽度2um不变,其横向扩散也不变,所以cell

spacing没变,导通电阻也没变。选取LW =5.8um, LP = 5.2um时器件耐压最大。

表3 LW、LP优化结果

(四)工艺流程与模拟仿真。主要工艺流程设计如下:

图3 VDMOS主要工艺

模拟 VDMOS基本工艺和器件结构参数设计如下:N+衬底为电阻率0.01欧姆,N-外延层掺杂浓度为2.19E14cm-2,厚度为52um;JFET注入离子浓度为3E12 cm-2,P阱离子注入浓度为5E14cm-2,在500keV能量下注入,且退火条件为退火条件1200℃ 100min N2/LwO2,P阱深结扩散为结深6um;LW =

5.8um、LP = 5.2um,N+有源区或N+漏区的离子注入浓度

5E16 cm-2,N+有源区或N+漏区的结深为0.5um。

图4 击穿电压仿真对比结果 图5 栅电荷仿真曲线

通过TCAD Silvaco软件进行仿真,并与传统模拟结果进行对比,击穿电压仿真对比结果如图4所示,其中红色为新结构曲线,绿色为传统结构曲线,新器件的BVDSS=708V,而传统

BVDSS=686,说明新器件耐压更理想。栅极电荷仿真结果对比如图5所示,曲线中间水平线段的长度表示QGD的大小,从图中可以清楚地看出新结构器件的密勒电容远小于传统器件的密勒电容。

三、实验流片测试与分析

基于上述VDMOS器件的结构以及工艺参数,该芯片在福顺微电子公司进行初次流片与测试,版图设计如图所示。

图6 新VDMOS版图

对器件进行显微拍照得到SEM图,如图所示,从SEM图可以看出新器件的cell pitch为11um,其中有源区注入窗口宽度LW≈5.86um,栅长LP≈5.14um;P阱结深约5.77um,为深结扩散,在栅下的横向扩散仅为2.6um左右。

图7 新器件SEM图

对新VDMOS器件的击穿电压特性进行测试,结果如图8所示,击穿电压达到700左右,符合理论设计。导通电阻测试结果如图9所示,VGS=10V,ID=6.5时候,导通电阻只有0.33欧姆,是非常小的了。反向输出电容测试如图10所示,在VDS=

25 V, VGS= 0V, f = 1MHz测得反向输出电容(Crss)为8PF,比改进前的传统器件(反向传输电容为13PF)降低了33.3%。目前市场上主流耐压600V级别的VDMOS传输电容普遍在11PF-25PF,可见本文提出的方法可以很好的降低VDMOS的方向传输电容,同时不影响耐压和导通电阻的特性。

图8 导通电阻测试结果 图9电容测试结果

四、结论

本文提出一种高能离子注入形成深结P阱的VDMOS器件新结构,获得短栅从而减小了反向传输电容,同时采用JFET注入的方法来解决导通电阻增加的矛盾,用TCAD软件对元胞间距、LW、LP参数进行优化仿真。流片测试验证了理论分析的正确性,测试结果表明反向传输电容只有8PF,与传统VDMOS结构(13PF)相比大大降低了,提高VDMOS器件的开关速度。从测试图形中可以看出,在参数优化的条件下,器件结构不仅具有较为理想的高击穿电压,而且其导通电阻比较低,可见该器件具有广阔的应用前景。

参考文献:

[1] 郭丽莎,夏洋. 一种减少VDMOS寄生电容的新结构.现代电子技术[J].2009,20(4):200-202

[2] 肖志强,向军利,衡草飞. 减小VDMOS密勒电容和反向恢复电荷的研究.微电子学,2005,35(3):305-307.

[3] 张鹤鸣,李跃进,戴显英. 减小VDMOSFET反向传输电容的研究[J].电子学报,1998,26(8):69-71.

[4] 陈利,李开航,郭东辉. 一种适用于高低压电路单片集成的LDMOS器件. 微电子学.2006,6(36):837-842.

[5] 周杰,陈利,郭东辉. 基于STI工艺的高压LDMOS器件设计与优化.中国集成电路,2010,12:46-52.

[6] 戴显英,张鹤鸣,李跃进,李伟. 功率VDMOS开关特性与结构关系[J].电子学报,1988,25(1):98-101.

[7] 刘侠,孙伟锋,王钦,杨东林. 高压VDMOS电容的研究.电子器件,2007,30(3):783-786.

[8] 魏麟. 一种提高Power VDMOSFET栅电荷性能的新结构. 微电子学与计算机,2005,22(8):141-143.