采用负反馈结构设计的高性能MOS 开关

2015-11-28程亮

程 亮

(山西经济管理干部学院,山西 太原 030024)

近年来,随着超大规模集成电路的发展,片上系统(SOC)已成为芯片技术发展的一个主流方向。片上系统中的重要模块,模/数转换器(ADC)在结构设计、制做工艺、性能指标上都有了巨大的进步,正在朝着低压、低功耗、高速和高精度的方向发展。而ADC 电路中的一个重要组成部分是采样保持电路,在采样保持电路结构中使用了大量的MOS开关,MOS 开关的线性度、稳定性、速度都将直接影响到ADC 系统的各项指标。

MOS 开关的信号采样过程对信号的信噪比(SNR)和信号噪声及失真比(SNDR)有至关重要的影响。传统结构的MOS 开关存在导通电阻非线性、限制输入信号幅度、芯片占用面积大等问题。

本设计采用负反馈电路结构,用来稳定采样周期内MOS 开关的栅源电压,以保证开关导通电阻和输入信号无关,同时还采用了电容充放电技术以提高采样周期内MOS开关栅极电压,实现MOS 开关栅压的自举。通过对MOS 开关结构及性能的一系列改进,很大程度上减小了开关在采样过程中对信号的影响。

1 现有技术分析

MOS 器件在作为开关的使用过程中,常工作于截止(关断)以及三极管区域(开启),在信号的采样过程中,因MOS管导通电阻随输入信号变化而产生的非线性因素是导致采样信号具有较大失真度的主要原因。MOS 开关管导通电阻阻值为:ron=1/gds,其中。所以,从此式子中可以得到MOS 开关的导通电阻和输入信号有关。

通常情况下,如果对MOS 开关的线性度要求不高,可以采用单个的NMOS 或单个的PMOS 来作为MOS 开关,但这种开关具有较为严重的电阻非线性问题,其导通电阻随输入信号的变化而变化;此外,MOS 阈值的大小也限制了输入信号的幅度。为降低导通电阻的非线性,有时也采用CMOS 结构,这种结构在一定程度上有效降低了MOS 开关导通电阻随输入信号变化的非线性,如图1 所示,但是在高线性度要求开关电容电路结构中,这种开关依然无法满足要求。

图1 NMOS,PMOS,CMOS 结构及导通电阻随栅源电压的变化特性

在如今的深亚微米低压(如1.8 V 及以下电源电压)工艺条件下,出于对电源电压波动的考虑(而MOS 管阈值电压随特征尺寸的减小变化不大),同时为得到较高保真的信号,所以在采样系统中,常采用栅压自举及时钟倍增技术来实现MOS 开关[1]。图2 中即为这种开关结构的简单示意图。

图2 栅压自举及时钟倍增技术以提高MOS 开关导通电阻的线性度

在上图2 中,晶体管M10,M11,电容C2,C3 以及反相器I0 共同构成电荷泵结构,产生对晶体管M3 的栅极时钟控制信号;电容C1 通过开关M4 和主开关管MS 栅极连接,并通过开关M1 和开关MS 源极相接,使得输入信号在被采样的过程中主开关MS 栅源电压保持不变,从而保证了开关MS的导通电阻和输入信号无关;而M7,M8 构成反相器结构。该电路在保持(hold)及采样(sample)两时钟周期内的电路结构以及相应的时钟控制信号如下图3 所示。

从图3 中可以看出,在保持时钟周期内,晶体管M3,M2,M5 以及M6 开启,电源电压对电容C1 充电,使其上极板电位达到VDD,而开关管MS 栅极通过M5,M6 连接到地,对其栅极复位;而在采样时钟周期内,因电容C1 两端无直流通路,其上极板电位将在电源电压VDD上叠加一输入信号Vin。从而在无交叠的时钟控制信号控制下,开关管MS 在采样周期内,其栅源电压将维持不变,从而维持了导通电阻的稳定性。

图3 MOS 开关采样及保持时钟周期工作电路结构以及时钟控制信号

现有高性能MOS 开关采用栅压自举以及时钟倍增(或电荷泵)技术,在很大程度上抑制了MOS 开关导通电阻随输入信号变化而产生的非线性因素,并因此而提高了输出端采样信号的信号噪声及失真比。但同时该电路结构因多个电容的引入而占据了较大的面积;并且,电荷泵技术的引入,使得时钟电压倍增到2 倍的电源电压,这有可能会引起可靠性问题的产生。

2 电路设计

图4 即为本设计中所采用的负反馈结构且具有较高性能的MOS 开关结构图,主要包括以下几个部分:主MOS 开关管,负反馈结构,开关电容电路网络以及时钟馈通抑制结构。100 为整个开关电路结构,结构中包含四部分,分别为主MOS 开关管101,负反馈结构102,开关电容电路网络103以及时钟馈通抑制结构104。负反馈结构102 提供一个随输入信号变化的MOS 开关栅极电压;而开关电容电路网络103实现电平转移(level shift)功能,对栅极电压提供一个采样周期内的直流偏置;时钟馈通抑制结构104 采用一个和主开关管成一定尺寸比例的MOS 晶体管以消除时钟馈通对输出信号的影响。

图4 负反馈高性能MOS 开关结构示意图

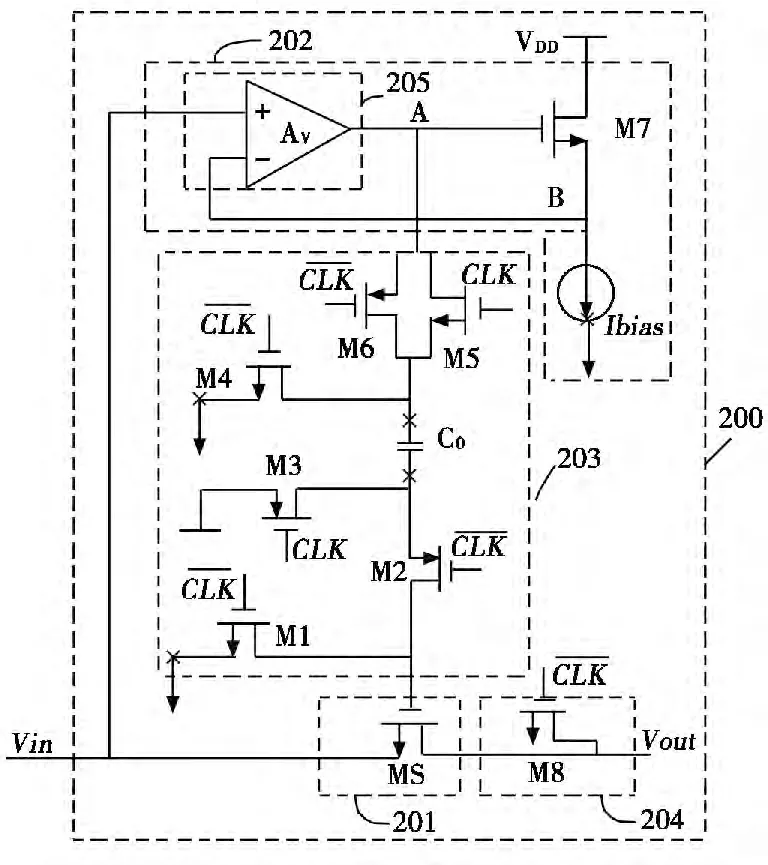

下图5 所示电路结构即为本设计所采用的一种实现方式,200 为带有负反馈,开关电容以及抑制时钟馈通结构的高性能MOS 开关结构。

图5 带负反馈结构高性能MOS 开关的电路实现

上图5 中201 为普通MOS 开关管,也是该电路中核心结构;202 结构中,运算放大器205 结构以及偏置在Ibias 直流电流下的晶体管M7 共同构成负反馈结构。其中运算放大器205 正输入端接MOS 开关201 信号输入端,而运算放大器205 结构负输入端和晶体管M7 源极连接。故而在晶体管M7 固定地偏置在电流Ibias 以及在运放负反馈机制作用下,205 结构运算放大器输出端A 点和负输入端B 点之间的压差将不随输入信号的变化而变化,也即是A 点电压和MOS 开关201 源端电压差将不随输入信号的变化而发生变化,从而实现了较为线性的导通电阻。

上图中203 结构即为带有开关电容结构的电平转移(level shift)结构,在保持时钟周期内实现对电容C0的充电,使其下极板电位为电源电压;而在采样时钟周期内,因无直流通路,电容下极板,也即是开关管结构201 栅极电压达到VDD+VDS2+Vin,从而可以保证晶体管MS 栅源电压和输入信号无关;另外在结构203 中,采用CMOS 结构M5,M6 以便更好的传递运放结构205 输出端信号。

上图中204 为消除时钟馈通效应二极管连接方式MOS管,其尺寸和主开关201 结构成一定比例关系,以消除时钟下降沿晶体管MS 沟道中电荷馈入输出端,引起信号的失真。

3 结论

在对信噪比要求高的信号处理系统中,本文所采用的一种负反馈的方式来维持主开关管在采样时钟周期内的性能稳定。相较于传统的栅压自举及时钟倍增MOS 开关,本发明具有更小的芯片面积;同时电路中也不存在较高的时钟倍增电压,从而也较大地增强了电路的可靠性。

[1]Wang Lei,Yin Wen jing,Xu Jun.A Bootstrapped Sampling Circuit for High-Resolution and High-Speed A/D Converter[J].Microelectronics,2007,37(1):80-84.