某飞控数据检测设备通信接口设计

2015-11-16白仲斐

白仲斐

某飞控数据检测设备通信接口设计

白仲斐

白仲斐 孙 科

中国飞行试验研究院

本文基于飞机试飞中所使用的地面飞控数据检测设备,介绍如何将检测设备与机上飞控系统通过通用I/O接口进行通信,文中给出了硬件连接框图、电路原理图、时序图、程序代码和性能评价,本设计在机务地面维护中的成功应用,可以为包括A/D转换数据的记录或任何其他涉及大量数据存储设备的工程测量应用提供一定的参考依据,是一项较为实用的基础设计。

引言

随着新一代战斗机、大型客机、运输机等军民用飞机的试飞科目的日益复杂,数字飞控作为新型飞机不可或缺的控制系统,对飞行安全中起着至关重要的作用,所以在地面准备过程中,对飞机飞控数据进行有效的检测显得尤为重要。

随着技术的发展,检测装置也在发生着日新月异的变革,结合目前在某试飞领域最新引进的一种且在试验机上应用较为广泛的检测装置,它的关键环节就是如何实现该检测设备与机上飞控系统进行稳定可靠的通信,考虑到实际应用的可靠性、稳定性和经济性,该通信装置的核心部件选用应用较成熟的C8051芯片,这就使得机上飞控系统的SRAM与检测装置的C8051之间通信连接接口的实现就成为迫在眉睫需要解决的问题,本文就是基于此背景,解决了SRAM与C8051通过地址锁存器实现了可靠的连接,进而实现了两者之间的数据和控制指令的通信。

飞控通信检测装置

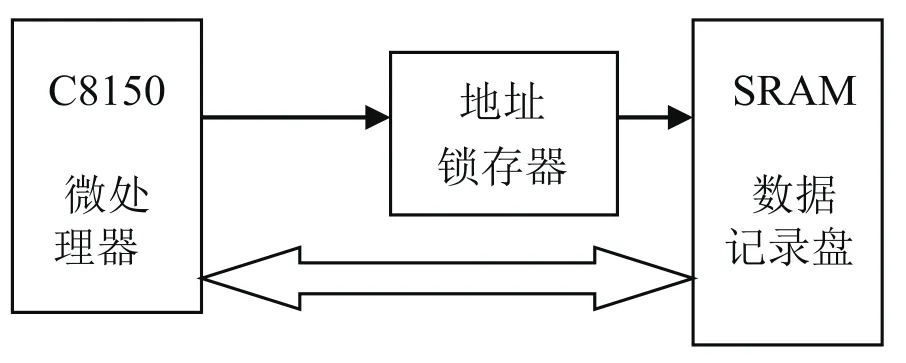

本文以C8051F000微处理器和TC74VHC537FW为控制处理核心,其他还包括一些供电等外围电路,实现了对机上飞控核心部件SRAM的读写控制,原理框图如图1所示。

图1 记录盘配置系统原理框图

这里的微处理器和控制处理芯片是基于一个支持实时通信和嵌入式跟踪的32位ARM7TDMI-S CPU,并带有128KB嵌入式的高速Flash存储器。较小的封装和很低的功耗,以及8位ADC和10位DAC,使其特别适用于工业控制以及航空测试系统。

该方案设计中使用的是LY6164JL-121型高速静态存储器,假定对其访问时间为10ns。如果所用SRAM的访问时间大于45ns,则需要加入NOP指令以延长地址建立时间及读/写选通时间。需要的引脚数取决于所支持的地址空间。对于本设计的128K字节地址空间,需要21个引脚。

另外,本文对外部SRAM接口电路的设计方案,对任何一个通用SRAM器件都可以在类似的方式下工作。

检测装置接口电路的硬件环境

C8051F000、SRAM、地址锁存器之间的硬件连接框图如图2所示。

图2 外部SRAM接口框图

微处理器C8051的地址线和SRAM的地址次线分别对应相连,进行地址的选通;“CS”、“WR”、“RD”等控制指令分别相连,进行读、写的控制,AD[7:0]为地址、数据复用总线,分别与锁存器和SRAM的输入输出接口相连,进行相应的地址与数据的通信。

检测装置C8051F000、(128k× 8)SRAM和地址锁存器硬件电路

接口部分采用地址和数据总线复用的方式以减少所需要的端口引脚数。当传输数据时低位地址保持在一个锁存器中。图3给出了该实现方案经过验证的电源电路图和C8051F000、SRAM、地址锁存器之间详细的电路配置图。

图3 经过测试的C8051F000、(128k×8 )SRAM和地址锁存器配置

双向端口操作

接口部分采用地址和数据总线复用的方式以减少所需要的端口引脚数。当传输数据时低位地址保持在一个锁存器中,“Data1”用作数据输入总线输出总线和部分地址总线,对总线的复用需要对端口的配置进行动态改变使端口按需要设置为输入或输出。

为了将一个端口引脚配置为输入,必须将其相应的端口配置寄存器位(PRTnCF.x)设置为“0”使其输出方式为“漏极开路”,寄存器锁存位(Pn.x)必须设置为“1”,使其输出状态为高阻态。例如下面的代码将端口0的所有引脚配置为输入:

mov PRT0CF,#00h;漏极开路输出方式

mov P0,#0ffh;高阻抗

下面的代码将端口0的所有引脚配置为推挽输出方式 :

mov PRT0CF, #0ffh ;推挽输出方式

SRAM_Read子程序(见程序代码部分)给出改变端口方向的一个例子,在程序执行的前一阶段“DATA1”口被配置为输出,将低字节地址输出到端口锁存器,在程序执行的第二阶段“DATA1”口被配置为输入,从外部SRAM读取数据。

接口电路程序控制实现

该程序控制系统由初始化SRAM接口逻辑程序、读外部SRAM程序、 写外部SRAM程序等组成,功能是通过该接口电路程序实现硬件间的有效连接,实现稳定的通信,从而实现对记录盘的各种配置以及对记录数据进行精确管理。

软件操作

“SRAM_Init”、“SRAM_Read”和“SRAM_ Write”是用于访问外部SRAM的三个子程序。

“SRAM_Init”程序初始化SRAM接口逻辑和端口配置。该程序只在器件的初始化过程中被调用。该程序假定交叉开关已经被允许(XBR2.6=1)例如:

mov XBR@, #40h ; 允许交叉开关

acall SRAM_Init ; 初始化SRAM

“SRAM_Read”程序从外部SRAM读一个字节,调用该程序之前,先将DPTR装入16位的待读地址,然后调用”SRAM_Read”,该程序将从DPTR所指向的地址读到的数据返回到ACC。

例如:

mov DPH, #00h ; 装入高字节地址

mov DPL, #00h ; 装入低字节地址

acall SRAM_Read ; 进行读操作,数据返回到ACC

“SRAM_Write”程序将ACC中的一个字节写入到外部SRAM,地址由DPTR指定,调用该程序之前,将待写数据装入ACC,将DPTR装入16位的待写地址,然后调用 “SRAM_Write”

例如:

mov DPH, #00h ; 装入高字节地址

mov DPL, #00h ; 装入低字节地址

mov a, #55h ; 装入待写数据

acall SRAM_Write ; 进行写操作

程序代码中的主程序概述了如何对该外部128KB SRAM的每一个字节进行读写,该程序向外部SRAM写入一个字节,再从写入的地址读回,然后比较回读的值与写入的值是否一致,程序接着处理下一个地址,直到整个64K的存储块写完,一旦低存储块写完,程序将 “A16位”置1(见示例代码中“常数和声明”一节),切换到高存储块。程序将接着对高存储块的每个字节进行同样的读、写和校验操作。

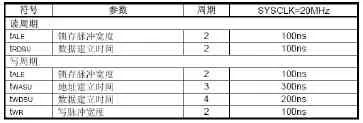

时序说明

图4和图5分别给出按示例代码实现的读和写时序波形。表1给出这些图形中的时间值。

图4 读周期时序波形

图5 写周期时序波形

表1 读和写周期时序

读时序说明

“tRDSU”(表1)是指从读选通信号有效到输出数据有效的时间。与这一时序相对应的代码为:

clr RD ;使读选通有效

;NOP ;加入NOP指令延长tRDSU

mov a, DATA ;读数据

如上所示,为了满足SRAM的建立时间,需要在“clr RD”之后加入NOP指令。

写时序说明

如表1所示“tWR”是指“/WR”脉冲的宽度,下面的代码段用于产生这一脉冲。

clr WR ;使写选通有效

;NOP ;加入NOP指令延长tWRSU

setb WR ;使写选通无效

如上所示,为了满足SRAM的建立时间,需要在“clr WR ”之后加入NOP指令。

结语

本系统以较为成熟的C8051F000和TC74VHC537FW为控制处理核心,采用多路复用的并行接口方案,使用通用I/O端口,实现了与飞控核心部件SRMA的通信,从读或写过程的进入到返回,一个字节读或字节写占用34个SYSCLK周期,对于20MHz的SYSCLK,相当于1.7µs。这就是说可以达到的最大传输率为588K字节/s,达到了较高的数据传输率。为类似的工程应用提供了可行的参考途径。

10.3969/j.issn.1001-8972.2015.02.037