高速深流水线浮点加法单元的设计

2015-10-21郑莉平余宁梅西安理工大学自动化与信息工程学院陕西西安70048中国航天科技集团公司第九研究院第七七一研究所陕西西安709

张 明,郑莉平,余宁梅(.西安理工大学 自动化与信息工程学院,陕西 西安 70048;2.中国航天科技集团公司第九研究院第七七一研究所,陕西 西安 709)

高速深流水线浮点加法单元的设计

张 明1,2,郑莉平1,余宁梅1

(1.西安理工大学 自动化与信息工程学院,陕西 西安 710048;2.中国航天科技集团公司第九研究院第七七一研究所,陕西 西安 710119)

在X87执行环境下,采用基于Two-Path算法的并行深度流水线优化算法,设计了一种能够实现符合IEEE-754标准的单精度、双精度和扩展双精度及整型数据且舍入模式可控的高速浮点加法器。采用并行深度流水设计,经验证,功能满足设计要求,使用TSMC65nm工艺库进行综合,其工作频率可达900MHz。

浮点加法器;IEEE-754;Two-Path算法;并行流水线

0 引言

浮点运算单元(FPU)是微处理器(CPU)的重要组成部分,是进行大规模数据运算处理的关键技术[1]。在通用处理器中,浮点加法指令、浮点减法指令及浮点反转减法指令最终都是使用浮点加法单元来实现的[2]。浮点加法运算过程是由指数差计算、尾数对阶移位、有效数相加、前导零计算、规格化操作、例外处理等单独操作组成。通过提高各个操作步骤的并行化,减少运算过程的关键路径,可以提高浮点加法运算单元的性能[3]。根据设计要求,对浮点加法单元的结构进行并行优化,采用基于Two-Path算法的深度流水设计,在X87执行环境下进行仿真验证,兼容X87指令集中的浮点加法指令,包括对控制状态寄存器、状态寄存器和标记寄存器的处理过程。

1 数据格式

本设计兼容IEEE-754浮点标准,IEEE-754标准浮点数据具体格式[4]如表1所示。

表1 浮点数据类型格式

实数Y=(-1)S×F×2E-Bias,其中:S(sign)为符号位,F(significand)是有效数字位,E(exponent)为指数位,Bias为偏移值[5]。目前主流计算机系统中运算数据的表现形式均是通过上述表达式转换而来的。

2 浮点加法单元的算法

2.1 浮点加法单元Two-Path算法

由于传统浮点加法算法每个步骤之间都是串行执行的,限制了FPU的执行效率,FARMWARL M P提出的Two-Path算法[6]主要在以下方面进行了改进:

(1)通过判断指数差的符号,对操作数进行交换,使其总是较大的操作数在前。除指数相等的情况外,数据转换这一步骤可以省略。在指数相等的情况下,则不需要进行对阶移位,有效减法的运算结果是一个精确值,不必进行舍入操作。数据转换步骤中的加法与舍入步骤中的加法互斥,可以将传统算法中三个全长加法延时减少一个。

(2)在有效数加法的运算过程中,指数差绝对值△E≦1的情况下,运算结果一般不会出现多位数据有多个零的情况,故不需要对结果进行全长的规格化移位操作。当指数差绝对值△E>1时,有效数的加法过程只需一个全长的对阶移位器。对于有效数减法,可以分两种情况:①如果指数差绝对值△E≦1,只需要一个全长的规格化移位。这种情况下,一位的对阶移位和尾数交换条件能够通过指数差绝对值的最低位和指数比较与尾数比较的结果来进行预测。②指数差绝对值△E>1,则需要一个全长的对阶移位器,但却不需要超过一位的规格化移位。因此,全长的规格化移位与全长的对阶移位是互斥的,并且在关键路径上两种移位器只会出现一个。上述情况可以表示为:当△E≦1且是有效减法运算时为近端(CLOSE)路径;当△E>1时为远端(FAR)路径。

(3)在近端CLOSE路径中,将有效数相加和前导零计算并行处理,采用前导零预测直接从两个源操作数中预测出有效加法运算后结果中前导一的位置,得到规格化移位量[7]。

2.2 Two-Path并行深度流水优化算法

为进一步提高浮点加法运算单元的性能,引入了合并舍入的Two-Path算法。由于舍入计算的实现一般要等到运算结果产生后根据舍入模式才可以执行,并且只是对结果进行小数量的修改。合并舍入的Two-Path算法需要通路上每一个有效数的加法器同时计算出有效数相加结果(sum)和有效数相加结果加一(sum+1)两个运算结果。为此,浮点运算单元的主加法器采用混合加法器来同时计算sum和sum+1两个结果,混合加法器是一个专用加法器,通过共用内部硬件单元的方法以减少运算规模。在得到了可能的运算结果之后,通过分析浮点运算结果的末尾的多位有效数据包括最低位(LSB)、警戒位(guard bit)、舍入位(round bit)和粘贴位(sticky bit),最终选择需要的结果。由于舍入方式的不同,还需要产生一个有效数相加结果加 2(sum+2)的运算结果,并且需要一个舍入矫正操作。在旁路通道上,需要在执行主通路时同时处理符号位的结果以及特殊数据的运算过程,保证整个设计的并行化。

本文基于合并舍入的Two-Path算法提出了一种高速深流水线浮点加法单元设计,共6级流水线。第1级完成分离操作场(符号场、指数场、尾数场),指数差的计算以及尾数大小的比较;第2级实现尾数交换、有效加减法的判断、结果符号预判、通路选择等操作;第3级完成尾数对阶移位,其中FAR通路是全长对阶移位,CLOSE通路是最多一位的移位;第4级进行有效数相加和前导零预测;第5级完成舍入选择和指数尾数规格化;第6级完成最终结果的选择、特殊数据处理、对例外的标记。其算法结构如图1所示,通过Verilog HDL硬件描述语言对算法进行实现。

图1 浮点加法单元结构图

3 浮点加法单元的实现与验证

3.1 指数差计算

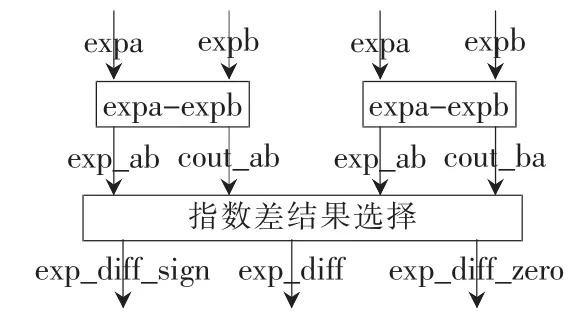

该模块通过分别计算|expa-expb|和|expb-expa|,其中expa为操作数0的指数,expb为操作数1指数。通过16bit超前进位加法器,分别得出操作数0指数减操作数1的结果(exp_ab)及进位(cout_ab)和操作数1指数减操作数0的结果(exp_ba)及进位(cout_ba),从而得到两个源操作数的指数大小关系:不等于(exp_diff_sign)和等于(exp_diff_zero),以及指数差的绝对值(exp_diff),如图2所示。

图2 指数差计算数据通路图

3.2 移位器

设计中共有两个全长移位器,其中一个移位器为67bit数据尾数对阶移位器,用来对较小的尾数进行逻辑右移。通过指数差判断移位量,从而得到较小尾数对阶移位后的结果。另一个移位器为65bit数据规格化移位器,用来对CLOSE通路有效数相加计算后的结果进行规格化左移位。通过前导零预测得出移位量,然后对运算结果进行移位,完成规格化操作。

3.3 加法器设计

加法器是浮点加法单元最主要的模块电路。本设计在不同阶段的操作过程中运用了多种加法器。实现16bit超前进位加法器,需要使用4个超前进位加法器模块(CLA)进行级联[8]。CLOSE通路指数规格化同样采用的是16bit超前进位加法器,如图3所示。

有效数相加模块采用64bit的混合加法器,即采取4个16bit混合加法器并行计算,每个16bit的混合加法器计算出16bit的计算结果(out0_0、out1_0、out2_0、out3_0)及其进位(cout0_0、cout1_0、cout2_0、cout3_0)和计算结果加一(out0_1、out1_1、out2_1、out3_1)及其进位(cout0_1、cout1_1、cout2_1、cout3_1),再通过每一级的进位来选择最终结果(sum_0)及其进位(cout_0)和最终结果加一(sum_1)及其进位(cout_1),如图4所示。

图4 64bit主加法器数据通路图

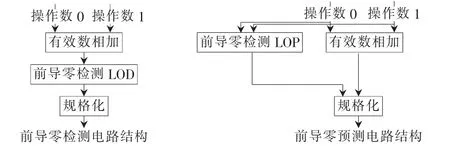

3.4 前导零计算

前导零预测逻辑电路是提高浮点加法器性能的关键。前导零计算一般有两种方式:前导零检测和前导零预测[9]。前导零检测处理的是浮点加法运算中有效数相加的结果,而预测处理的是需要进行浮点加法运算中有效数相加的两个有效数,即前导零预测不需要等待浮点数加法运算有效数相加的计算结果就可以得到前导零的个数。两者均可以完成有效数相加后结果的前导零的计算,但前导零预测可以与有效数相加运算并行进行,很大程度地提高浮点加法运算的性能,图5为前导零检测电路结构与前导预测电路结构框图。

图5 前导零检测与前导零预测电路结构框图

3.5 浮点加法运算单元的验证

本设计功能验证采用VMM测试方法学,通过System verilog系统硬件描述语言搭建对比测试平台,产生定向测试激励和受约束随机测试激励[10],对本设计的运算结果与C模型运算结果进行比对,比对结果一致,覆盖率达到100%,功能上满足设计要求。图6为完成一次FADD指令的结果波形图。

图6 浮点加法单元仿真波形图

4 结论

本文从浮点加法单元的算法结构入手,提出了高速深流水线浮点加法单元设计。使用TSMC65nm工艺库进行综合,其工作频率可达900MHz,兼容X87指令集,可用于高通量CISC微处理器中。

[1]张予器.超高精度浮点运算的关键技术研究[D].长沙:国防科学技术大学,2005.

[2]陈弦,张伟功,于伦正.并行浮点加法器架构与核心算法的研究[J].计算机工程与应用,2006,17(3):53-55.

[3]夏杰,宣志斌,薛忠杰.基于流水线结构的浮点加法器IP核设计[J].微计算机信息,2008,24(9):192-193.

[4]朱亚超.基于IEEE754的浮点数存储格式分析研究[J].计算机与信息技术,2006(9):50-52.

[5]Intel Corporation.Intel 64and IA-32Architectures Software Developer′s Manual[Z].U.S:Intel Corporation,2011.

[6]王颖,林正浩.快速浮点加法器的优化设计[J].电子工程师,2004,30(11):24-26.

[7]靳战鹏.高速浮点加法运算单元的研究与实现[D].西安:西北工业大学,2006.

[8]夏有为,林正浩,杨晓峰.一款32位嵌入式CPU的定点加法器设计[J].电子技术应用,2005,31(10):76-78.

[9]李星,胡春媚,李勇,等.前导1预测算法的设计与实现[J].计算机科学.2013,40(4):31-35.

[10][美]克里斯·斯皮尔.SystemVerilog验证测试平台编写指南[M].张春,赵益新,麦宋平,译.北京:科学出版社,2009.

The design of high-speed deep pipeline floating-point adder unit

Zhang Ming1,2,Zheng Liping1,Yu Ningmei1

(1.School of Automation and Information Engineering,Xi′an University of Technology,Xi′an 710048,China;2.The 771th Institute of the 9th Academy of CASC,Xi′an 710119,China)

The paper describes a high-speed floating point adder design,which achieves compliance with IEEE-754 standard single-precision,double-precision,extended-double-precision and integer data with rounding mode controlled,working under X87 execution environment.The design is based on Two-Path algorithm with parallel pipeline depth optimization algorithm.The paper puts forward a deep parallel pipeline design.After verification the function meets the design requirements,using TSMC 65 nm technology library,whose operating frequency is up to 900 MHz.

floating point adder;IEEE-754;Two-Path algorithm;parallel pipeline

TP332.1

A

1674-7720(2015)20-0015-03

张明,郑莉平,余宁梅.高速深流水线浮点加法单元的设计[J].微型机与应用,2015,34(20):15-17.

2015-05-16)

张明(1987-),通信作者,男,硕士,助理工程师,主要研究方向:数字集成电路设计与验证。E-mail:zhangm_work@163.com。

郑莉平(1963-),女,硕士,副教授,主要研究方向:电路与系统。

余宁梅(1963-),女,博士,教授,主要研究方向:专用集成电路设计技术及工艺。