H.265解码器去块滤波并行化设计与性能优化

2015-10-20周建政刘华平

周建政,刘华平

(1.天格科技(杭州)有限公司,浙江 杭州 310011;2.上海格谱信息科技有限公司,上海 200072)

1 H.265标准

H.265同H.264/AVC一样采用的变换算法是基于宏块的DCT算法,因此,当压缩率很高时,就会导致严重的块效应。为了提高主观和客观视觉效果,H.265中同样引入去块效应滤波系统,可以很好地消除块效应的影响,并且滤波后的帧可用于后续帧的运动补偿预测,从而避免了由于虚假边界积累误差而导致的图像质量进一步降低,但同时,去块效应滤波系统也带来了大量的复杂运算[1-2],特别是大分辨率视频,去块效应相关参数都是跨越多行,这样导致对数据读写内存Cache Miss,对于1 080p视频去块效应滤波计算量占据H.265解码器25%~30%,因此去块效应滤波系统成为H.265在实时应用中的主要瓶颈之一。

近一年,移动终端设备CPU技术朝高主频,多核和低功耗方向发展,这就为大视频在移动设备上的流畅播放提供硬件资源基础。H.265是最新一代视频编解码器技术,其市场应用响应相应比H.264要快速,目前互联上就有很多H.265压制的视频源,H.265解码性能优化就成为一件急迫的事。

本文先对H.265标准中的去方块滤波进行详细的介绍,分析在HM14.0现在的架构中不能并行化处理的原因,然后对HM14.0的软件结构进行设计,让H.265去块效应滤波能做到基于CU行并行处理,这样就可以充分利用移动终端多核并行处理,大大提升解码器的速度。在每个宏块行内每个像素行,进一步用ARMv7 SIMD汇编指令去优化,最后给出性能优化前后的数据。

2 H.265标准中的去方块效应滤波

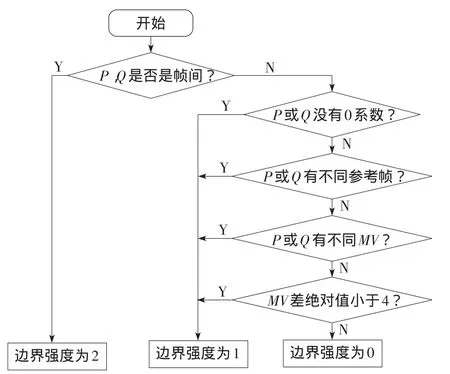

H.265去方块效应滤波采用与H.264/AVC类似的方法,但H.265边界情况比H.264要复杂,所以考虑所有边界条件的情况下,H.265整体去方块效应滤波复杂度比H.264高一点。H.265去方块效应滤波处理单元是CU,其处理顺序与解码过程一致,所有垂直边缘先做滤波处理,然后再做所有水平边缘的滤波处理。去方块效应滤波流程图如图1所示[2-4]。

图1 去方块效应滤波流程图

2.1 方块边缘检测

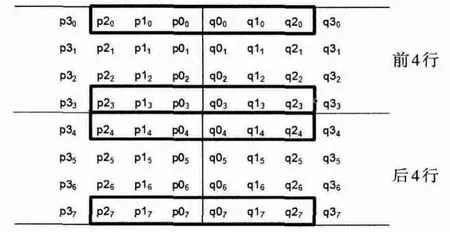

去方块效应滤波涉及到3类边界,分别是编码单元边界(CU boundary)、变换单元边界(TU boundary)和预测单元边界(PU boundary),这些边界都会直接影响到去方块效应滤波器的操作。例如有时CU的边界与PU或TU的边界重叠,边界确定后就是计算边界的强度,边界的强度直接影响边界滤波的选择。目前这些所有的边界信息解析和判断都是嵌入在解码过程中,往往要整个帧解码完成才能知道各个边界的消息,这样导致去方块效应滤波只能放到最后完整的去做,不利于帧内宏块行的并行操作。边界强度的计算流程图如图2所示。

2.2 滤波器关/开判断

引入2个阈值变量β和tC,这2个变量结合边界相邻的像素决定了滤波器的关开,强弱滤波器的选择以及弱滤波处理。β和tC的选择是根据相邻像素,然后查阅参数文献[4]。滤波器开关和强弱判断涉及到4行边界左右6个像素,如图3所示。

图2 边界强度计算流程图

图3 框中的像素用于滤波关开和强弱选择(截图)

2.3 滤波器[5]

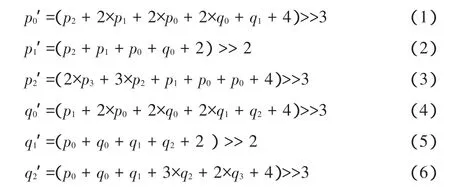

H.265去块效应滤波分强滤波和弱滤波,强滤波器会用到边界相邻块各4个像素值,通过如下方程式去更新边界相邻块各3个像素值。方程式如下

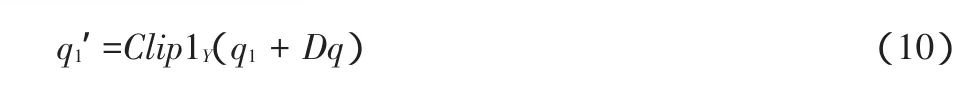

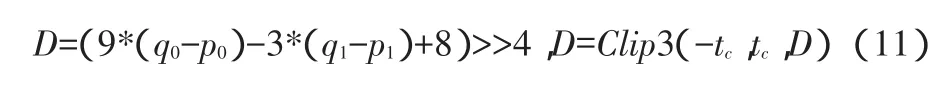

式(1)~(3)是强滤波更新垂直边界左边或水平边界上方相邻3个像素值,式(4)~(6)是强滤波更新垂直边界右边或水平边界下方相邻3个像素值。弱滤波器会用到边界相邻块各3个像素值,通过如下方程式去更新边界相邻块各2个像素值。方程式如下

式(7)、(8)是弱滤波更新垂直边界左边或水平边界上方相邻二个像素值,式(9)、(10)弱滤波更新垂直边界右边或水平边界下方相邻二个像素值。

其中

3 去方块效应滤波并行算法设计

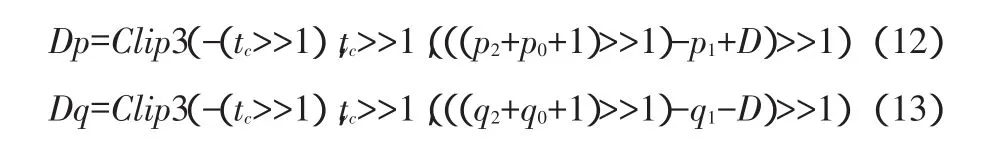

图4是HM14.0编解码器流程,以LCU为单元,采用递归的方式把整个个帧解码出来,然后整帧来进行后处理,包括去块效应滤波和自适应校点补偿处理。

图4 H.265算法框架图

这种结构导致无法做帧内基于LCU行的并行,去块效应滤波器没有基于LCU行并行,也会影响到自适应校点补偿(SAO)并行处理。去块效应滤波配合整个解码器的帧内按LCU行的并行处理进行修改,处理过程流程图如图5所示。

图5 解码器流程图

HM14.0结构就是先把一帧数据全部解码出来,然后整帧进入后处理模块,这个缺点是不能基于LCU行的并行处理,而基于LCU并行化处理,当一个线程在解码后面的LCU单元时,另一个线程就能处理已经做好准备LCU行的去块效应滤波和SAO。基于LCU并行化处理过程说明:解码器仍然是以LCU为单元进行解码,同时建立以4×4为最小块的结构数组用于存放当前最小处理宏块的边界情况。去块效应滤波较解码器要延迟一LCU行去做滤波处理,例如解码器第一LCU行解码完成,不会去做去块效应滤波,因为会影响第二行处理过程。当第二LCU解码完成后才进行去块效应处理。帧内基于LCU并行去做去块滤波要注意保留一些数据,例如帧间预测就要保留一行LCU的像素数据,以备帧间预测使用。

4 ARM平台性能优化[6]

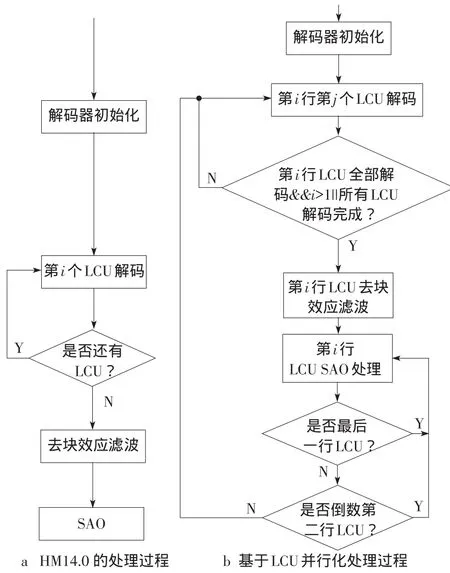

ARM Cortex系列的处理器,支持并行的高效指令集(NEON),Cortex-A系列增加了16个128 bit的Q寄存器单元,这些寄存器单元可以灵活当作 8 bit,16 bit,32 bit,64 bit和128 bit单元使用,NEON寄存器结构如图6所示。

与128 bit寄存器配对,NEON指令集有很多并行的加、减、乘和相关的逻辑指令,例如处理8 bit像素,通过NEON指令集可以一次性处理16个像素。通过SIMD指令优化,并行的处理指令数就会是原来的1/16。

图6 NEON寄存器结构图

从本文的第二部分详细分析了H.265去块效应滤波器,例如水平强滤波器会用到边界上下各4个像素点,然后通过一系列的并行运算后,最后更新边界上下各3个像素点,这种结构很利于应用NEON并行指令,其数据读取和存储如下:

vld1.32 {d6[0]},[r4],r1 @p10,p20,p30,p40

vld1.32 {d7[0]},[r4],r1 @p11,p21,p31,p41

vld1.32 {d8[0]},[r4],r1 @p12,p22,p32,p42

vld1.32 {d9[0]},[r4],r1 @p13,p23,p33,p43

vld1.32 {d10[0]},[r4],r1 @p14,p24,p34,p44

vld1.32 {d11[0]},[r4],r1 @p15,p25,p35,p45

vld1.32 {d12[0]},[r4],r1 @p16,p26,p36,p46

vld1.32 {d13[0]},[r4] @p17,p27,p37,p47

这几条指令就把4行,每行左右各4个共8个像素都取到寄存器中,接下来的所有运行都是一次处理4个像素,最后处理完用vst1.32一次存储4个像素,这样4个像素并行处理,所有的指令处理周期数是原来的1/4。

进一步优化,滤波器的关开和强弱是基于4行像素内容去判断,这样的结果是4×4的块间可能去块效应滤波器的强弱不致,如果在上面加个判断,如相邻的8行像素都是使用强滤波或都是弱滤波,这样就可以将上面的并行处理扩展到基于8行8个像素并行处理,这样处理速度会提升8倍。

5 对比分析

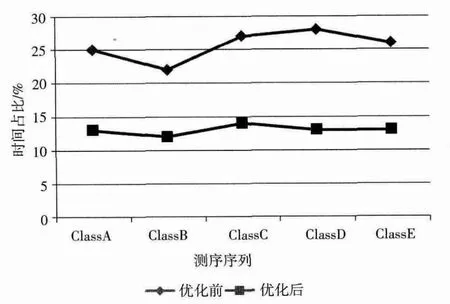

H.265主要应用场景是大视频和高帧率,算法复杂增加,同时处理数据量多,这样就要充分利用处理器多核并行去处理数据。本文就是阐述如何将原来在视频帧全部解码出来后整帧做去块效应滤波处理,通过解码处理过程中,并行化处理得到各个处理单元的边界信息,实现了帧内基于宏块行级的并行化处理。同时针对ARM平台进行了SIMD汇编优化,使得去块效应滤波在整个解码器算法复杂度降低了一半,大大提升了解码器处理能力。图7是优化前后,去块效应滤波在整个解码器复杂度的比例优化前后比较图。

图7 去块效应滤波占解码器时间比例

测试序列覆盖H.265 ClassA~ClassE,分析统计去块效应滤波在对应序列中占整个解码器优化前后比倒的变化。

从图7可以看出,并行化优化去块效应滤波性能能整体提升解码器近13%的性能,使得解码器能在移动设备上能实现更大分辨率的视频播放。

[1]FRANK B,BENJAMIN B,KARSTEN S,et al.HEVC complexity and implementation analysis[J].IEEE Trans.Circuits and Systems for Video Technoligy,2012,22(12):1685-1696.

[2] 唐添,王进,刘运强,等.去块效应方法的研究[J].电视技术,2008,32(2):16-18.

[3] SULLIVAN G J,OHM J R,HAN W J,et al.Overview of the high efficiency video coding(HEVC)standard[J].IEEE Trans.Circuits and System for Video Technology,2012,22(12):1649-1668.

[4] Recommendation ITU-T H.265,Audiovisual and multimedia systems,infrastructure of audiovisual services coding of moving vide,high efficiency video coding[S].2013.

[5]HAN W J,OHM J R,SULLIVAN G J,et al.High efficiency video coding(HEVC)text specification draft 6[C]//Proc.8th JCT-VC Meeting.San Jose,CA,USA:[s.n.],2012:56-59.

[6] Cortex-A8 Technical Reference Manual[EB/OL].[2014-09-28].http://www.docin.com/p-97569305.htm l.