一种900 V超结VDMOSFET器件的设计与仿真*

2015-10-19杨永念

杨永念

(重庆邮电大学光电工程学院,重庆 400065)

一种900 V超结VDMOSFET器件的设计与仿真*

杨永念

(重庆邮电大学光电工程学院,重庆 400065)

功率MOSFET在现代电子工业中已经得到了广泛的运用,然而在高压功率MOSFET器件中,如何平衡功率MOSFET的击穿电压与导通电阻的冲突一直是研究热点。结合超结理论和传统功率VDMOSFET的生产工艺设计了一款高压超结VDMOSFET器件,运用半导体器件仿真软件对器件结构进行优化,得到P柱区和N柱区掺杂浓度和厚度的最优值和工艺参数。仿真结果表明,设计的超结VDMOSFET器件击穿电压和导通电阻分别为946 V和0.83 Ω,很好地平衡了功率MOSFET击穿电压与导通电阻的冲突。

功率MOSFET;超结VDMOSFET;导通电阻;击穿电压

1 引言

功率MOSFET器件在低压环境中的运用已经占据主导地位,然而在高频高压环境中,由于击穿电压和导通电阻之间的矛盾一直未被很好地解决,功率MOSFET在高频高压环境中的运用受到很大限制[1]。尽管20世纪80年代初期提出的IGBT产品在一定程度上缓解了这个问题,但是由于IGBT引入的三极管结构中存储的少子电荷很难快速消除,导致其开关速度很大程度上低于MOSFET[2]。

1988年,飞利浦公司D J Coe将超结结构运用在高压横向MOSFET中,生产出横向高压超结功率MOSFET,以此生产出来的超结功率MOSFET在保持相同击穿电压的同时具有很小的导通电阻,超结功率MOSFET的概念开始进入人们的视线[3]。1993年,电子科技大学陈星弼教授将纵向功率MOSFET中漂移层用交叉的P/N柱区结构代替,形成纵向超结功率MOSFET[4]。目前VISHAY、INFENION等国外著名半导体制造公司已经有超结功率MOSFET的产品生产,如INFENION公司最新的CoolMOSTMC6、C7系列[5]。然而由于国内生产技术和工艺水平等原因限制,很少有公司可以生产出性能很好的超结功率MOSFET,相应的设计理论及制造工艺也很少有学者去研究与讨论。

论文设计了一款同时具有高击穿电压和低导通电阻的超结功率VDMOSFET,并且对超结VDMOSFET的结构、工艺制造和运作机理做了简单的分析,通过半导体模拟仿真软件SILVACO[6~7]对超结VDMOSFET模型结构参数进行优化,最终确定器件最优结构和相应的制造工艺,然后对所设计的超结VDMOSFET器件的核心电特性进行了仿真分析。

2 超结VDMOSFET的结构分析与工艺设计

图1为超结VDMOSFET的结构平面图,相对于传统VDMOSFET结构,此结构将传统VDMOSFET轻掺杂的N-外延层改为了P柱区和N柱区相互交叉的重掺杂区。以图1所示的P沟道超结VDMOSFET为例,当其正向导通时,电子从源区由沟道流过N柱区,进入衬底,最后流到漏极。当其接反向电压时,外延层中N/P柱区将形成横向的电场,平衡掉N柱区多余的载流子,能够极大地提高超结VDMOSFET的击穿电压。

图1 平面栅N型超结VDMOSFET平面结构图

与传统工艺相比,超结VDMOSFET的制造工艺流程主要多出了超结结构的形成[4]。超结结构的制造主要有两种方法:(1)多步外延与多步离子注入相结合;(2)深槽刻蚀与外延填槽相结合。方法(1)由于后面每次离子注入会对前面外延层区域掺杂浓度造成影响,使得形成的柱区浓度不均匀,并且由于离子相互扩散,形成类似“糖葫芦”状的柱区,致使P柱区和N柱区之间的电荷平衡很难维持。方法(2)可以直接控制填充物质的掺杂浓度,更加便于保持N/P柱区的电荷平衡。因此本次设计采用深槽刻蚀来制造。

超结VDMOSFET的沟道形成将采用与传统VDMOSFET相同的“自对准”双扩散工艺,利用源极和栅极多晶硅栅作为P阱和n+源区的掩模,通过双扩散差来得到沟道区域。

图2所示为一个P沟道超结VDMOSFET制造工艺平面图,具体核心工艺设置见表1。

图2 平面栅N型超结VDMOSFET工艺流程示意图

表1 关键工艺步骤参数设置

超结VDMOSFET主要设计参数指标:BV=900 V,RDS(on)=0.9 Ω,VGS=2~4 V,Ptot=150 W。为了使所设计的超结VDMOSFET有最小的导通电阻,设置N柱区和P柱区有相同的宽度。由超结理论确定所设计的超结VDMOSFET的结构参数[8~9]。超结VDMOSFET的几何参数:(1)

其中CP为N/P柱区宽度,tepi为N/P柱区的厚度。

通过目标参数BV=900 V计算N/P柱区的临界击

为了结构尺寸的合理化,选择所设计的超结VDMOSFET几何参数为0.1,将计算所得到的N/P柱区厚度带入式(1)得到N/P柱区的宽度。

N/P柱区掺杂浓度的计算:

其中ε为硅的相对介电常数,q为电子电荷量。计算可得EC=3.28×105V·cm-1,tepi=54.8 μm,CP=7.38 μm,Na=Nd=3.3×1015cm-3。由于超结VDMOSFET的击穿电压主要与P/N柱区厚度和P/N柱区的电荷平衡相关,而导通电阻的大小主要受到P/N柱区掺杂浓度的影响。为了确保目标参数设计达到指标,我们将首先对P/N柱区的厚度和掺杂浓度进行优化,然后对所设计的器件进行建模,最后对器件性能进行仿真分析。

3 仿真分析

在前面分析的基础上,可知道保持N柱区和P柱区的电荷平衡(CNNd=CPNa),能够最有效地提高超结VDMOSFET的击穿电压。假定N柱区和P柱区的宽度一样,则理论上只需确定N/P柱区有相同的掺杂浓度即可确保它们的电荷平衡。仿真过程将首先通过SILVACO仿真工具对N/P柱区厚度和浓度进行优化选择,然后将选定的参数重新建模,并且对其进行目标参数验证仿真。

3.1N柱区和P柱区厚度的选择

虽然前面已经通过计算得到了P/N柱区厚度为54.8 μm,但是在实际仿真和工艺中,超结VDMOSFDET高浓度掺杂的衬底会向P/N柱区扩散,导致有效P/N柱区厚度减小,所以需要对其厚度进行优化选择。仿真初始设置N柱区和P柱区的厚度和宽度分别为54.8 μm和7.4 μm,N/P柱区掺杂浓度为3.3×1015cm-3。其余参数设置以传统高压功率VDMOSFET的参数为依据设置[10]。

图3为P/N柱区沟槽深度与击穿电压和导通电阻的关系。通过图3可知器件击穿电压和比导通电阻都随着P/N柱区沟槽深度的增大而增大。为了满足器件设计目标的击穿电压900 V,由图3所示数据分析,经过折衷考虑,选择沟槽深度为56 μm。

图3 P/N柱区沟槽深度与击穿电压和比导通电阻的关系

3.2P柱区浓度优化

在优化选择好N/P柱区厚度后,虽然P/N柱区所设置的初始宽度和掺杂浓度相同,但是由于衬底、P阱与P/N柱区相互之间电荷扩散,会导致P柱区与N柱区掺杂浓度的不平衡,使得所设计的器件在被击穿时,P/N柱区电荷未被完全耗尽而影响所设计器件的击穿电压大小。所以需要对P柱区进行浓度优化仿真。设置P/N柱区厚度为56 μm,N柱区掺杂浓度为3.3×1015cm-3。图4为P柱区掺杂浓度与击穿电压和比导通电阻的关系。由图4可看到P柱区掺杂浓度的大小对比导通电阻的影响不大,而击穿电压随着P柱区掺杂浓度的升高而升高,直至达到电荷平衡,击穿电压开始下降。P柱区掺杂浓度在3.6×1015cm-3时,击穿电压最大。

图4 P柱区掺杂浓度与击穿电压和比导通电阻的关系

3.3仿真建模

通过上面的分析,最终选定N/P柱区厚度为56 μm,N柱区掺杂浓度为3.3×1015cm-3,P柱区掺杂浓度为3.6×1015cm-3,P/N柱区宽度为7.4 μm。

通过SILVACO软件仿真时的核心步骤参数设置如表1所示。

流程1和2确定N/P柱区厚度和宽度分别为56 μm、7.4 μm,掺杂浓度分别为3.3×1015cm-3、3.6×1015cm-3,比传统功率MOSFET的掺杂浓度要高1~2个数量级。高的柱区掺杂浓度有效地降低了器件的柱区电阻,使得寄生在超结VDMOSFET中的三级管更加难以导通,有效避免了寄生三极管导通所引起的二次击穿。流程3采用1 000~600 ℃均匀变温退火,更好地将淀积的P柱区与外延N柱区结合在一起,形成PN结。流程4保证P阱区高浓度的掺杂浓度,使P+区与多晶硅栅形成良好的欧姆接触。流程6中P-区2×1017cm-3的掺杂浓度,相对于P+区低浓度的掺杂,有效控制了器件的阈值电压。流程7高浓度的源区掺杂使得源区与金属电极形成良好的欧姆接触。

根据所设定的参数,对超结VDMOSFET建模如图5所示,P/N柱区厚度为56 μm,宽度为7.4 μm,P阱结深Xjp+=2.5 μm,沟道结深Xjp-=1.7 μm,源区结深Xjn=0.4 μm,沟道宽度约1.3 μm。

图5 超结VDMOSFET仿真平面二维图

表2 超结VDMOSFET结构参数

3.4目标参数验证仿真

对所设计超结VDMOSFET的工艺模型进行仿真,验证所设计模型的目标参数是否达到预期目标。仿真图形如图6~图8所示。

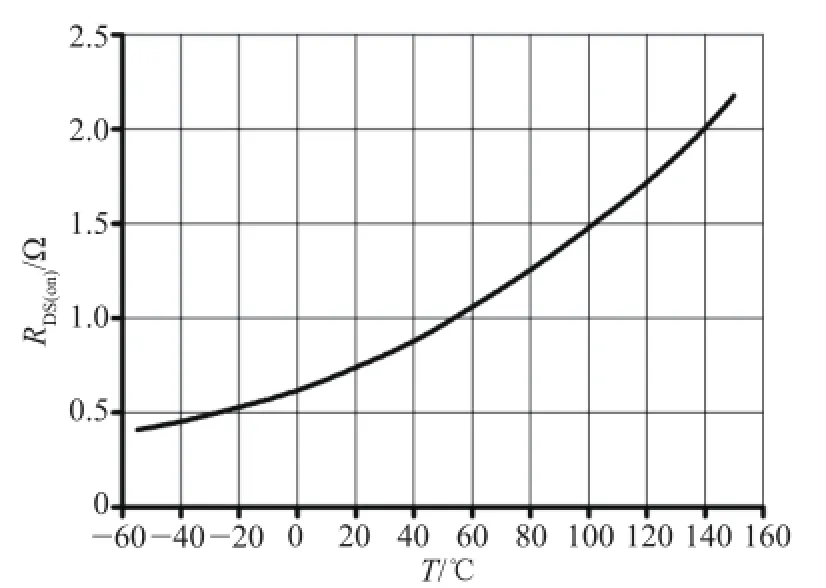

图6、图7、图8为超结VDMOSFET设计指标的仿真图。图6为超结VDMOSFET击穿电压图,截取击穿电压数值为946 V,大于目标设计参数BVDSS=900 V。超结VDMOSFET的击穿电压主要与N/P柱区深度和电荷平衡有关。在已经对P柱区电荷浓度进行优化完成的前提下,如果击穿电压没有达到预期的900 V,则适当增加N/P柱区的厚度,重新建模仿真。图7为超结VDMOSFET导通电阻随温度变化的曲线,截取T=25 ℃时,RDS(on)=0.83 Ω,比设计要求的导通电阻0.9 Ω小。对于击穿电压超过600 V的功率MOSFET,导通电阻主要汇集在外延层区,而超结VDMOSFET在外延层(N/P柱区)高出传统功率MOSFET外延层1~2个数量级的掺杂浓度,极大地降低了其导通电阻。图8是在不考虑超结VDMOSFET自加热特性时,耗散功率与环境温度的关系,图中显示,在室温T=25 ℃时,其耗散功率为153 W,满足设计要求。

图6 超结VDMOSFET击穿特性

图7 超结VDMOSFET导通电阻随温度变化曲线

图8 超结VDMOSFET耗散功率随温度变化曲线

3.5器件电特性参数的仿真

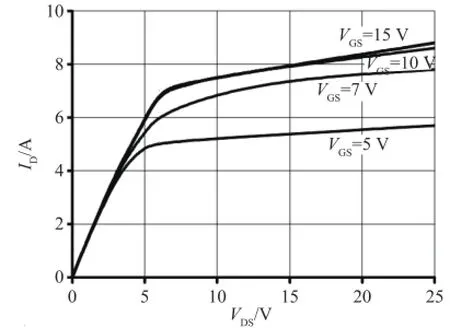

图9为所设计的超结VDMOSFET的I/V特性图,漏极电流ID随着VDS的增大而增大,当VDS<<2(VGS-VTH)时,超结VDMOSFET工作在深三极管区,此时电压与电流的函数近乎是一条直线,器件可等效为一个电阻。当VDS继续增大,直到VDS<VGS-VTH时,器件工作进入三极管区,此时沟道内自由电子数减少且沟道变薄,使得其沟道电阻增大,所以ID随着VDS增长速率变慢。当VDS>VGS-VTH,器件工作在饱和区,此时电子在耗尽区内的漂移速度达到饱和速度。而随着VDS的继续增大,使电子所需要通过的有效沟道长度逐渐减小,漏极电流会缓慢上升。相比于很多大电流的功率MOSFET,此超结VDMOSFET由于正向导通时P柱区不参与电子的流通,其额定电流会相对较小。

图9 超结VDMOSFET的I/V特性图

图10为超结VDMOSFET电容特性,随着电压的升高,器件内部寄生电容逐渐下降。将其与VISHAY公司型号为IRFPF40、900 V高压功率MOSFET的电容特性相比较,此超结VDMOSFET的输入电容Ciss和反向传输电容Crss比IRFPF40更低,尤其是输入和输出电容。这是由于超结VDMOSFET外延层区域插入的P柱区,使得寄生电容的等效极板有效面积减小,从而减小了寄生电容。而功率MOSFET的开关速率与输入电容的充放电速率密切相关,更低的输入电容确保了超结VDMOSFET的开关速率。反向传输电容的降低对MOSFET防止二次击穿和预防器件误导通有重大的意义。从图10中可以看到Coss在低压条件下,由于超结VDMOSFET外延层N/P柱区未被耗尽的缘故,漏源两端的寄生电容会相对很大,但当电压大于300 V以上时,漏源两端的寄生电压会降到很低,Coss变的只有十几皮法。所设计的超结VDMOS更加适合在高压高频领域环境使用。

由仿真结果,对超结VDMOSFET的部分核心参数与IRFPF40进行了对比,如表3所示。在同为900 V击穿电压级别的功率MOSFET器件中,所设计的超结VDMOSFET具有良好的U/I特性,阈值电压为3.1 V,电容特性在高压环境也明显优于IRFPF40,导通电阻只有IRFPF40的三分之一。

此次超结VDMOSFET的设计中,N/P柱区电荷平衡优化通过软件仿真完成,能够很好地确保所设计器件的良好性能。然而在实际工艺操作中,由于受到衬底对P柱区的反向扩散、沟道形成时多次离子注入工艺以及多次退火工艺等影响,如何维持N/P柱区的电荷平衡,将成为器件流片的一大难点。

图10 超结VDMOSFET电容特性

表3 核心参数对比

4 结论

本文较详细地分析了超结VDMOSFET的设计原理,并对其工艺实现进行了分析,借助半导体器件仿真软件对超结VDMOSFET结构参数进行仿真优化分析,给出了超结VDMOSFET具体核心工艺参数设置和简要的工艺流程图。然后对所设计器件的目标参数进行了仿真验证,并且将仿真得到的参数与传统VDMOSFET IRFPF40的参数进行比较。在同等级别击穿电压下,得到的超结VDMOSFET电容特性优于IRFPF40,且导通电阻约为IRFPF40的三分之一。

[1] 王锐,石会平,张学涛,等. 功率 MOSFET 技术发展概述[C]. 第二十五届中国(天津)2011'IT、网络、信息技术、电子、仪器仪表创新学术会议论文集. 2011.

[2] 周文定,亢宝位. 不断发展中的 IGBT 技术概述[J]. 电力电子技术,2007, 41(9): 115-118.

[3] Coe D J. High voltage semiconductor device: U.S. Patent 4,754,310 [P]. 1988-6-28.

[4] Chen X B, Mawby P A, Board K, et al. Theory of a novel voltage-sustaining layer for power devices [J]. Microelectronics journal, 1998, 29(12): 1005-1011.

[5] Hancock J, Stueckler F, Vecino E. CoolMOS™ C7:Mastering the Art of Quickness [J]. 2013. Ravel B.

[6] ATHENA user's guide [J]. Document Version, 2008.

[7] Muhr T Atlas ti. The Knowledge Workbench: V5. 0 User's Guide and Reference [M]. Scientific Software Development, 2004.

[8] Kondekar P N, Parikh C D, Patil M B. Analysis of breakdown voltage and on resistance of super junction power MOSFET CoolMOS TM using theory of novel voltage sustaining layer [C]. Power Electronics Specialists Conference, 2002. pesc 02. 2002 IEEE 33rd Annual. IEEE, 2002, 4: 1769-1775.

[9] Pravin N Kondekar, et al. Analysis of the breakdown voltage, the on resistance, and the charge compensation of super-junction power MOSFET [J]. Journal of Korean Physical Society, 2004, 44(6): 1565-1570.

[10] 严向阳,唐晓琦,淮永进. 高压VDMOSFET击穿电压优化设计[J]. 微纳电子技术,2008, 45(10): 577-582.

Design and Simulate of High Voltage S-J VDMOSFET

YANG Yongnian

(Chongqing University of Posts and Telecommunications, Chongqing 400065, China)

Power MOSFET in modern times has been widely used in electronic industry. In high-voltage power MOSFET device, it's still not solved that how to balance the contradiction of the breakdown voltage and the on resistance of power MOSFET. The article combine with super-junction theory and manufacturing process of the traditional power VDMOSFET to design a high voltage super-junction MOSFET, and using the semiconductor device simulation software to optimize the structure of device. Get column P and N column of doping concentration and thickness of the optimal value and process parameters. The simulation results show that the S-J VDMOSFET with breakdown voltage of 946 V and on resistance of 0.83 Ω. It solved the conflict of balance between the breakdown voltage and on resistance of the power MOSFET perfectly.

power MOSFET; super-junction VDMOSFET; on resistance; breakdown voltage

TN305

A

1681-1070(2015)03-0029-06

杨永念(1990—),男,硕士研究生,研究方向为半导体器件设计和制造。

2015-01-23

重庆市教委科学技术研究项目(KJ120505)