PVT恒定高精度亚阈值CMOS电压基准源

2015-10-19吴瑶,龚敏,高博

吴 瑶,龚 敏,高 博

(四川省微电子技术重点实验室,成都 610064)

PVT恒定高精度亚阈值CMOS电压基准源

吴瑶,龚敏,高博

(四川省微电子技术重点实验室,成都 610064)

提出一种基于SMIC 65 nm标准CMOS工艺库的高精度电压参考源电路。对3种不同类型偏置于亚阈值区的NMOSFET进行了讨论,采用无电阻温度补偿对温度进行高阶补偿,可以减小对工艺、电压、温度的敏感性。仿真结果表明:在不同工艺角下,电源电压、温度使基准电压Vref的变化仅为±1.36%。电压参考源的温度系数大约为4.5×10-6℃-1,电源线性调制率为2.1% mV·V-1,最小工作电压仅为0.56 V。

亚阈值MOSFET;电压基准源;PVT恒定;低工作电压

1 引言

电压基准源作为模拟电路基本模块,主要应用于ADC / DAC、锁相环等电路[1]。随着沟道尺寸的减小,深亚微米下器件耐压性能降低,同时为满足低压供电,电源电压不超过1 V[2],此时三极管不能正常工作(pn结压降0.7 V),因此低压低功耗高精度的亚阈值基准源电源管理芯片的设计与研究尤为重要。

PVT(工艺、电压、温度)的波动程度决定了基准源的性能,TC(温度系数)值、工作电压、线性调整率(直流电源抑制比)和功耗[1~2]均是衡量基准源好坏的重要参数。为了降低基准源对温度的敏感性,一般需要对电路进行高阶温度补偿。多数电路采用 PTC(正温度系数)热敏电阻和NTC(负温度系数)热敏电阻对基准源温度进行高阶补偿。然而,由于热敏电阻大小随工艺变化显著(±25%),而且温漂可达上千10-6℃-1[3],导致基准源稳定性降低。为保证芯片性能,流片后必须对电阻进行修调,而深亚微米工艺下,电阻修调难度变大,不仅增加工艺步骤、提高工艺难度而且还带来了成本的提高。

本文采用线性补偿机制代替电阻对温度高阶进行补偿,无需后续修调,减少工艺步骤,节约了成本。

基准源模块低压低功耗特性与低线性调整率存在折中关系。电路设计中通常采用折叠共源共栅结构来提高直流电源抑制比[4],同时MOS管类型与基准源工作电压密切相关,因此本文采用工作在饱和区的LVT(低阈值电压晶体管)代替NVT(正常阈值电压晶体管)保证电源抑制比,同时降低基准源工作电压。最后,深亚微米工艺由于沟道尺寸的减小,工艺影响器件特性从而影响电路性能,电路中基准源正负温度系数电路采用不同阈值电压MOS组合,以减小由工艺变化带来的影响。

2 PTAT和CTAT产生电路

基准源一阶基准电路是由与温度成正比(PTAT)模块和与温度成反比(CTAT)模块组合而成。把PTAT和CTAT电流(IPTAT,ICTAT)按M1和M2比例扩大或者减小再叠加起来产生一个基准电流[5]。然而,由于硅器件温度项的非线性性,一阶输出电压不可能与温度无关,并且一阶电路的输出电压温漂系数可达几十或者上百10-6℃-1,3.3节将通过高阶温度补偿得到一个精准基准电压源。最后,把电流输出到一个电阻得到基准电压Vref。

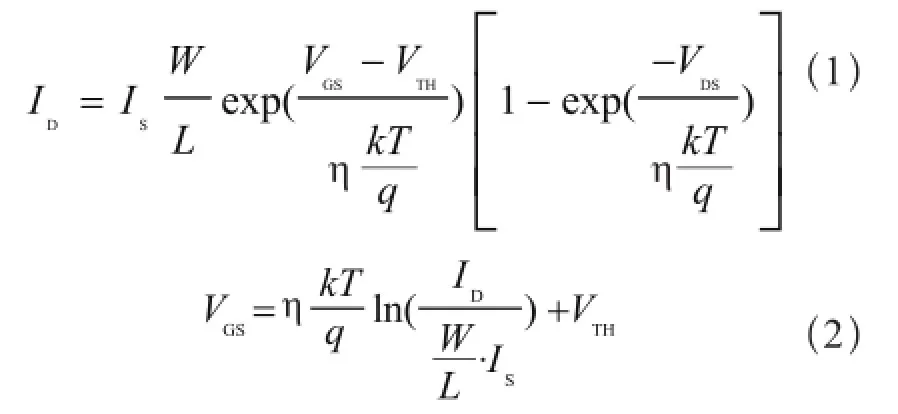

通常亚阈值CMOS基准电压源正温度电流系数都由MOS的栅源电压产生,当MOS工作在亚阈值区,漏电流和栅源电压表达式[6]如式(1)、式(2):

其中η为亚阈值斜率,是常数,IS是特定电流,表达式为[2]:

由式(1)、式(2)、式(3)表达式有:

根据式(4)Vout表达式,令,当μN1Cox.N1>μN2Cox.N2out,显然,V具有负温度特性;反之μN1Cox.N1<μN2Cox.N2时,Vout具有正温度特性。此外,如果N1、N2是相同类型的NMOS,则可改变其宽长比,得到不同温度系数的Vout。

对于任何尺寸的CMOS标准工艺库中的工艺参数,有:

(μCox)HVT<(μCox)NVT<(μCox)LVT由Vout表达式可知,当NMOS处于亚阈值区时,高阈值电压(NVT)NMOS的Vgs负温度系数最明显,其次是正常阈值Vgs电压(NTV)NMOS,低阈值电压(LVT)NMOS的负温度特性最弱。因此,PTAT和CTAT由两组不同阈值电压的NMOS组合而成。本电路中采用一对工作在亚阈值区的HVT和LVT管,通过它们的栅源电压差产生CTAT电压;同理再由一对HVT管栅源电压差和一对NVT管栅源电压差,两对管栅源对再取差得到PTAT电压。

如图1(a),当N1为LVT,N2为HVT,可以得到一个CTAT产生模块,同理在图1(b)中,令N11、 N12为HVT,N21、N22为NVT,从而得到PTAT 电压产生模块。

图1 CTAT、PTAT产生模块

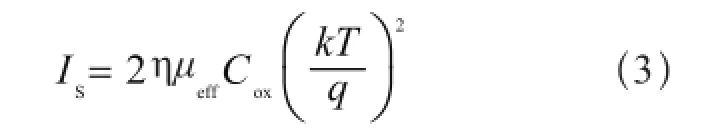

图2和图3分别基于MOS栅源差得到CTAT和PTAT电压与温度在不同工艺角下的仿真曲线。由图2可知在相同的温度范围内(-50~150 ℃),电压减小或者增大的幅度是一致的(约35 mV),即其正、负温度系数的绝对值相等。此外,VCTAT和VPTAT不同工艺角(ff、tt、ss)下的仿真曲线也一致。

图2 VCTATff、tt、ss 模型下仿真曲线

图3 VPTATff、tt、ss 模型下仿真曲线

3 抗PVT变化优化方案

本节的主要目的是获得高精度抗PVT(工艺、电压、温度)的亚阈值CMOS电压基准。图4显示核心电路不包括启动模块,启动电路可参考文献[7],补偿电路设计见第四节。

3.1抗工艺变化

深亚微米工艺下,工艺偏差会导致器件的参数偏差很大及非理想效应,从而影响基准电压源的精度稳定性。为了降低生产和不匹配因素带来的误差,本文提出了三种方法:当MOS工作在亚阈值区,Vth太小则会因工艺变化容易摆脱亚阈值区[8],导致电路状态不稳定,因此本文采用HVT和NVT组合产生正负温度电流。此外电流镜失配也可导致不匹配和错误,因此电流镜的MOS不采用最小尺寸[4]。最后,电阻的大小以及温漂随工艺变化十分明显,而标准CMOS工艺库中没有理想电阻,同时多晶硅电阻受工艺影响偏差比N阱电阻小[4],所以本文均采用多晶硅电阻。

3.2抗电源电压变化

基准源的电压特性不仅要满足高电源抑制比而且同时要满足低电压工作[9]。由图4可得:

Vref=(K1·ICTAT+K2·IPTAT)·R(5)

即:Vref只和ICTAT和IPTAT有关,如果IPTAT和ICTAT不随电源电压变化,则 Vref也保持不变。

共源共栅结构具有高输出电阻[9],因此本文采用共源共栅结构的放大器(V-I转换结构)来提高电路的电源抑制比。而共源共栅结构带来高电源抑制比的同时也会引起更高的工作电压,因而在基准电压源高电源抑制比以及低工作电压这两个参数之间存在一个折中[10]。在图4中,除了N1、N2、N11、N12、N21和N22等NMOS管偏置在亚阈值区,所有的器件都工作在饱和区,对处于饱和区的器件不采用最小沟道长度,不同工艺角下阈值电压的波动几乎不影响电路特性。此外最小的工作电压与器件的阈值电压大小密切相关[6]。而SMIC 65 nm标准CMOS工艺库中NMOS HVT(高阈值电压晶体管)的阈值电压约为0.43 V,而电源电压一般小于等于1.2 V,这样如果共源共栅结构采用HVT则不能保证其工作在饱和区,而采用NVT 和LVT能满足静态工作点要求。当处于饱和区时,HVT相当于长沟道器件,LVT相当于短沟道器件。同时由于LVT比NVT具有更低的阈值电压,因此可把基准源工作在饱和区的所有器件用低阈值电压器件替代,在保证高电源抑制比的同时也能达到低电压供电,第四节的仿真结果表明这种方法有效地把最低工作电压从0.89 V降到0.56 V。

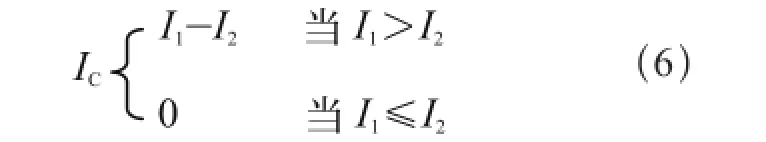

3.3温度补偿方案

通常基准源一阶电路温度系数可达几十或者上百10-6℃-1,图5为一阶核心电路仿真结果,因而需要一个高阶温度补偿电路来进一步减少由温度变化(-50~150 ℃)引起的误差。由于电阻补偿很容易受工艺变化影响[1],因此本文用分段线性补偿(原理图见图6)来对温度进行高阶补偿。

图5 基准电压源一阶电路ff、tt、ss模型温漂曲线

图6 分段线性补偿原理图[6]

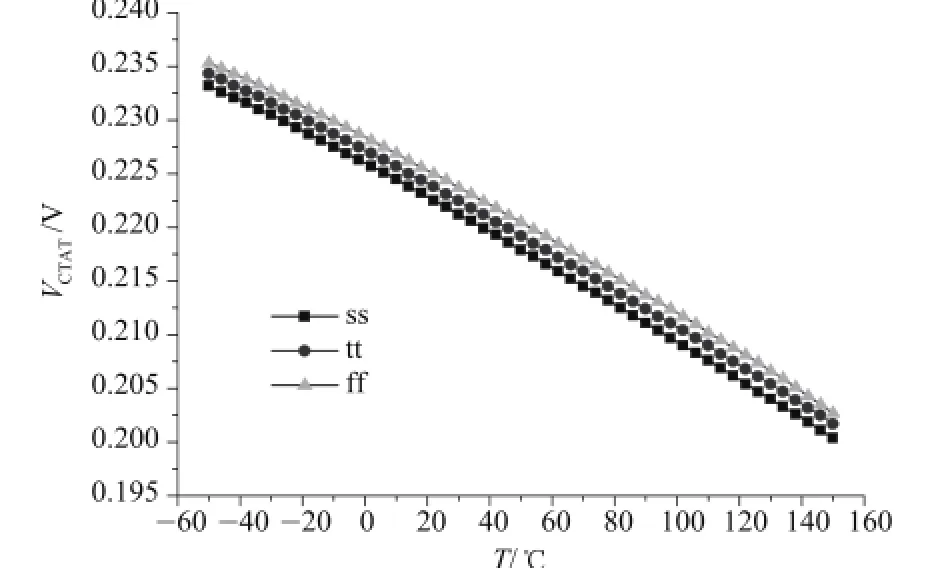

分段线性补偿原理为:

由式(6)可知,线性分段补偿模块能在特定温度下产生正负温度补偿电流,如图5所示,当T>50℃,K1·ICTAT>K2·IPTAT,Vref表现负温度特性电压,因而需要补偿一个正温度系数电流。因此图6中让I1= K21·IPTAT,I2=K11·ICTAT,同时满足K11·ICTAT<K21·IPTAT,最后得到正温度特性电流Ic。当T<50℃,Vref表现正温度特性电压,I1=K12·ICTAT,I2= K22·IPTAT,同时 K11·ICTAT>K21·IPTAT,得到一个负温度特性补偿电流Ic。

通过上述补偿机理,三阶电路可以由两个分段线性模块叠加到一阶电路得到,表达式为:

Iout=M1×IPTAT+M2×ICTAT+N1×Ic1+N2×Ic2(7)

很明显补偿阶数越高,基准源对温度敏感性能越低,此外分段线性补偿模块具有可复制性和叠加性,类推得到五阶补偿电路。数学表达式为:

Iout=M1×IPTAT+M2×ICTAT+N1×Ic1+N2×Ic2+N3×Ic1+N4×Ic2(8)

4 仿真结果与讨论

4.1仿真结果

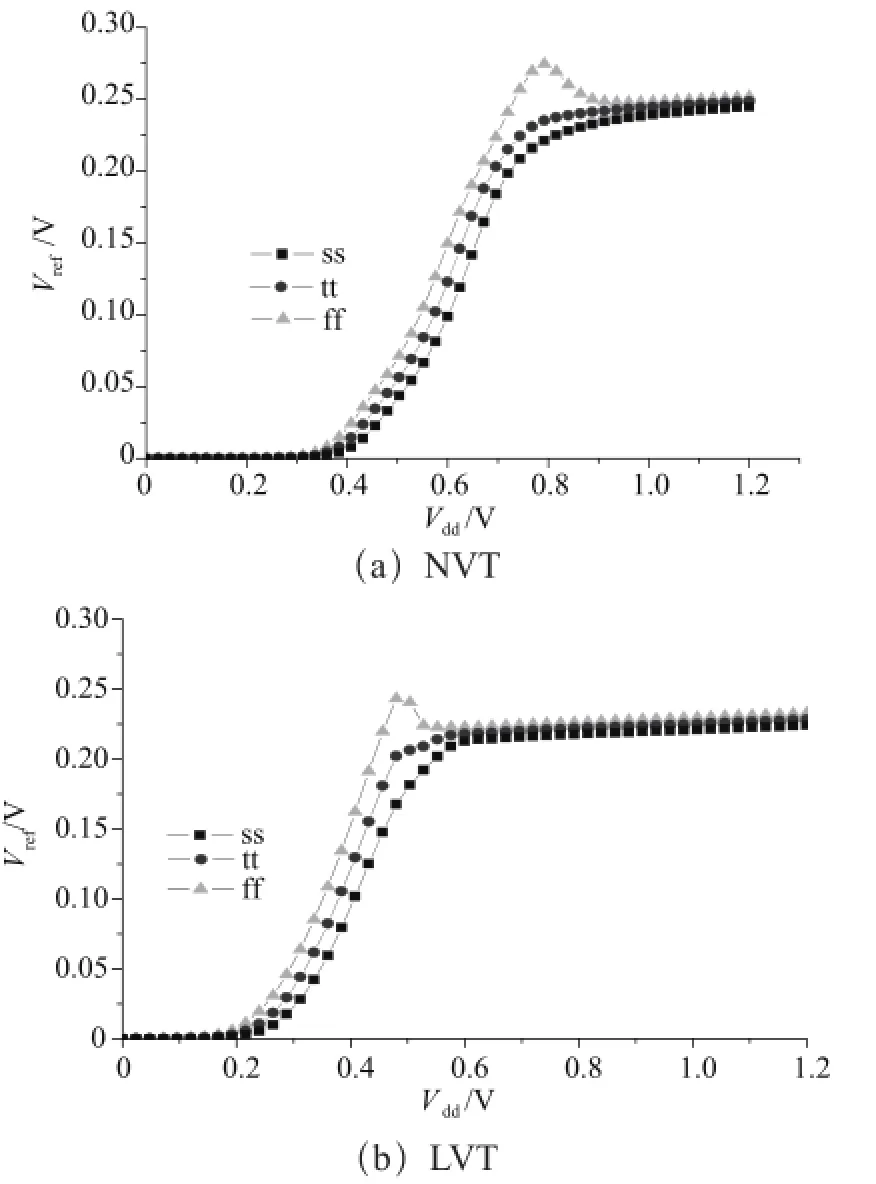

图7(a)、(b)所示为基准电压源同种结构下分别采用普通阈值电压MOS管和低阈值电压MOS管不同工艺角下对基准源的线性调整率的仿真结果。由图可知(a)、(b)线性调整率分别为4.7% mV·V-1和2.1% mV·V-1。同时,当全部采用工作在饱和区的NVT晶体管设计时,如图7(a),电路的最低工作电压约为0.9 V。当用LVT晶体管替代时,最低工作电压显著下降,如图7(b),仅为0.56 V。

图7 NVT和LVT不同工艺角下线性调整率曲线

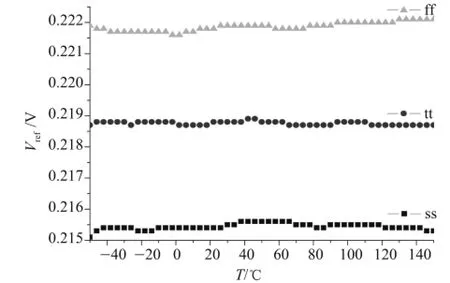

图8为基准源五阶补偿电路不同工艺角下温度特性曲线。仿真结果表明,在-50~150℃温度范围内,tt模型下温漂大小约为4.5×10-6℃-1,ff、ss模型下温漂也均不超过10×10-6℃-1,此外不同工艺角下Vref变化量仅为±1.36%,对工艺变化敏感度低。图9为基准电压源一阶、三阶、五阶温漂的蒙特卡诺图(取3000样本,横坐标表示温度系数,纵坐标表示区间内样本数),进一步验证了本文设计的亚阈值基准电压源低温漂特性。

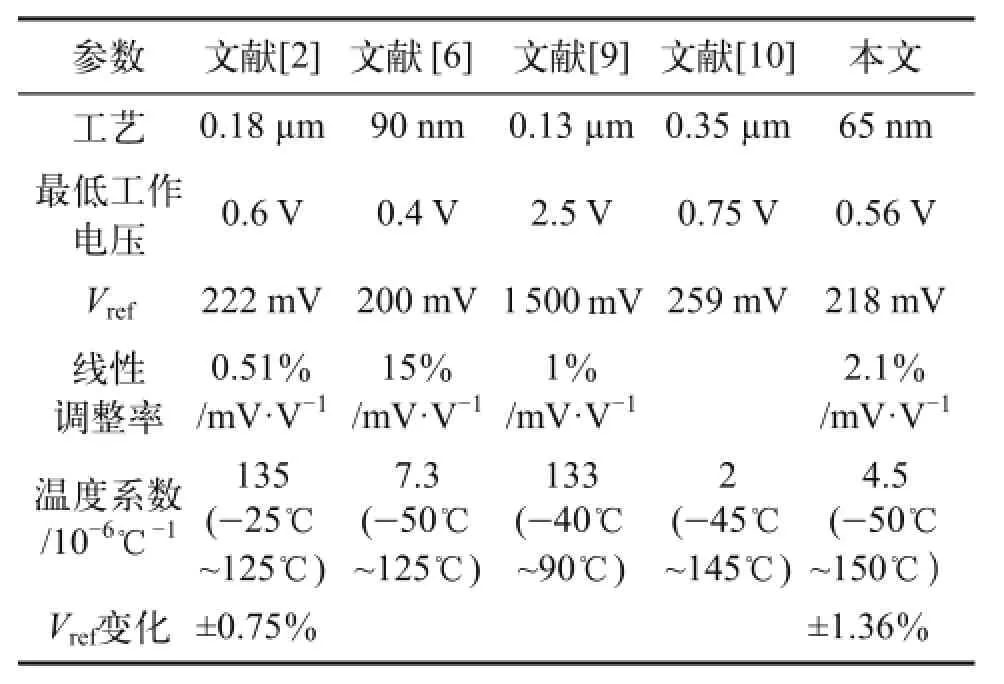

4.2结果分析

将本文与其他参考文献进行对比,结果如表1所示。参考文献[10]的结构是利用多晶硅电阻对温度进行补偿,尽管温漂低,但流片后需要修调。参考文献[2]缺乏高阶温度补偿。文献[9]只采用普通阈值电压MOS共源共栅结构,因此尽管保证了线性调整率低但是其最小工作电压大。文献[6]只使用微电流镜,尽管保证工作电压低但是易受电源电压影响。在本文中,共源共栅模块组成的LVT用来保证低的线性调整率和工作电压。此外,提出采用分段线性温度补偿电路(无电阻)进行高阶补偿。仿真结果表明本文设计的亚阈值CMOS基准电压源综合性能最优。

图8 基准电压源五阶电路ff、tt、ss模型温漂曲线

5 总结

本文基于SMIC 65 nm标准CMOS工艺设计了一种抗PVT变化的亚阈值基准电压源,用饱和区低阈值电压的MOS管全部代替普通阈值电压MOS管,在保证线性调整率(2.1% mV·V-1)的同时也能达到低压工作(0.56 V)。此外,高阶电路采用分段线性(无电阻)补偿使得电路在很宽温度范围(-50~150 ℃)内依旧保持极低的温度敏感性(TC=4.5×10-6℃-1)。最后,基准源采用工作在亚阈值区不同阈值电压的MOS阈值电压差产生正负温度电流,从而降低了工艺对单个MOS的影响,Vref偏差仅为±1.36%。

图9 基准电压源一阶、三阶、五阶温漂的蒙特卡诺图

表1 本文与其他文献的对比

[1] Gupta, Vishal. An accurate, trimless, high PSRR, lowvoltage, CMOS bandgap reference IC [D]. Ph.D Dissertation, Georgia Institute of Technology, 2007.

[2] Anvesha A, Maryam Shojaei Baghini. A Sub-1 V 32 nA Process, Voltage and Temperature Invariant Voltage Reference Circuit [C]. VLSI Design and 2013 12th International Conference on Embedded Systems(VLSID),2013 , 136.

[3] S T Rudenko, V Kilchytska, J P Colinge, V Dessard, D Flandre. On the high-temperature subthreshold slope of thin-film SOI MOSFETs [J]. IEEE Electron Device Letters, 2002, 23(3): 148.

[4] S Sengupta, K Saurabh, P E Allen. A process, voltage, and temperature compensated CMOS constant current reference [J]. ISCAS Circuits and Systems, 2004, 1: 325.

[5] K N Leung, P K T Mok. A CMOS Voltage Reference Based on Weighted Difference of Gate-Source Voltage between PMOS and NMOS Transistors for Low Dropout Regulators [C]. ESSCIRC Conference, 2001, 61.

[6] Michael David Cave. Scalable Voltage Reference for Ultra Deep Submicron Technologies [D]. Ph.D dissertation, the University of Texas at Austin, 2005.

[7] Windels J, Van Praet C, De Pauw H, Doutreloigne J. Comparative study on the effects of PVT variations between a novel all-MOS current reference and alternative CMOS solutions [C]. Circuits and Systems, 52nd IEEE International Midwest Symposium, 2009, 49.

[8] Yilei Li, Yu Wang, Na Yan, Xi Tan, Hao Min. A Subthreshold MOSFET Bandgap Reference with Ultra-Low Power Supply Voltage [C]. 2011 IEEE 9thInternational Conference, 2011, 862.

[9] E Boufouss, P Gérard, P Simon, L A Francis, D Flandre. High Temperature and Radiation Hard CMOS SOI Subthreshold Voltage Reference [C]. SOI-3D-Subthreshold Microelectronics Technology Unified Conference(S3S),2013, 1.

[10] Andreou C M, Georgiou J. An all-subthreshold, 0.75 V supply, 2×10-6℃-1, CMOS Voltage Reference [C]. Circuits and Systems(ISCAS), 2013 IEEE International Symposium,2013, 1477.

High-precision Sub-threshold CMOS Voltage Reference with PVT Invariant

WU Yao, GONG Min, GAO Bo

(Key Laboratory of Micro-Electronics Technology of Sichuan Province, Chengdu 610064, China)

The paper presents a pure CMOS high precision voltage reference circuit based on the subthreshold MOSFETs with the SMIC 65 nm standard CMOS process technique. Three different types of NMOSFETs and further resister-less temperature compensation are used to reduce process, voltage and temperature(PVT)sensitivity. Simulation result shows that voltage and temperature varies have little effect on the current according different process corners(Vrefvariation is only ±1.36%). Temperature and power supply sensitivity of the reference voltage is 4.5×10-6℃-1(-500~1 500℃)and 2.1% mV·V-1. In addition, the supply voltage is about 0.56 V.

sub-threshold MOSFETS; voltage reference; PVT invariant; low supply voltage

TN402

A

1681-1070(2015)03-0009-05

吴瑶(1990—),女,江西南昌人,四川大学硕士研究生,研究方向为超大规模集成电路设计。

2015-01-22