电荷泵锁相环环路滤波器的设计与优化

2015-10-15廉吉庆陈大勇翟浩

廉吉庆,陈大勇,翟浩

(1.兰州空间技术物理研究所,兰州 730000;2.空间量子频标技术核心专业实验室,兰州 730000;3.真空技术与物理重点实验室,兰州 730000)

电荷泵锁相环环路滤波器的设计与优化

廉吉庆1,2,3,陈大勇1,2,3,翟浩1,2,3

(1.兰州空间技术物理研究所,兰州 730000;2.空间量子频标技术核心专业实验室,兰州 730000;3.真空技术与物理重点实验室,兰州 730000)

环路滤波器是锁相环电路的重要部分,其性能好坏直接决定了电路输出信号的质量。以二阶无源环路滤波器为例介绍了电荷泵锁相环环路滤波器的设计方法,讨论了基于相位裕度和设计参数γ的环路滤波器优化设计,并且给出了仿真结果。结果证明这种环路滤波器设计方法正确,优化方法切实可行。

环路滤波器;锁相环;电荷泵;相位裕度;参数优化

0 引言

频率源广泛应用于现代电子设备中,其指标好坏直接影响电子系统的性能,因此频率源被许多人称为电子系统的“心脏”。常用的频率源有自激振荡源和合成频率源,其中合成频率源使用灵活、控制方便、性能优越,越来越受到人们的重视。

常用的频率合成技术中,锁相环是非常重要的一种,在高速通信、导航定位和航空航天等方面都有应用。环路滤波器是锁相环的重要组成部分,它连接在鉴相器和压控振荡器之间,起到维持环路稳定性、控制环路带内外噪声、抑制参考边带杂散干扰等重要作用,是锁相环频率合成器设计的关键[1]。目前已有许多文章对环路滤波器设计方法进行了讨论,但在关于滤波器性能的一些细节优化设计方面,并未深入探讨。本文在环路滤波器设计基础上,探讨针对环路锁定时间和输出噪声等方面的优化设计,并通过仿真验证优化设计的正确性。目前,该优化设计方法已用于部分项目的频率源设计,对频率源输出信号的相位噪声等有一定的改善作用。

1 锁相环频率合成原理

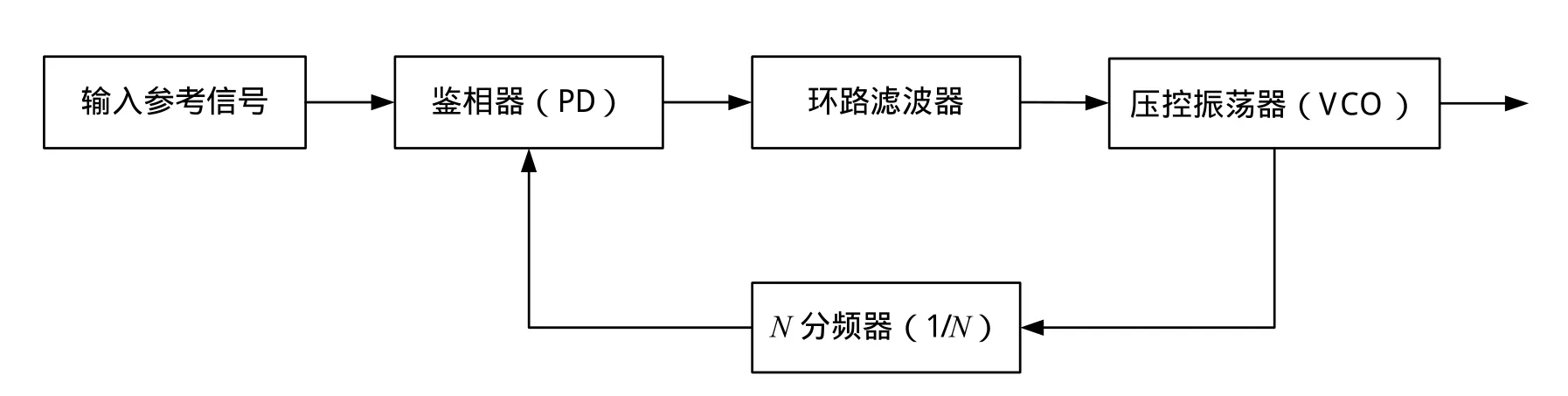

基本的电荷泵锁相环由鉴相器(PD)、分频器、环路滤波器和压控振荡器(VCO)等部分组成,其中鉴相器的输出端为电荷泵。目前常用的整数型电荷泵锁相环基本原理如图1所示。

图1 电荷泵锁相环工作原理图

输入参考信号与VCO输出信号的N分频通过鉴相器进行相位比较,鉴相器会输出一个和这2个信号的相位差相关的控制信号;控制信号控制电荷泵输出电流对环路滤波器的电容充放电,从而产生VCO压控端的控制电压。当环路达到稳定后,VCO输出频率稳定在输入参考频率的N倍[2]。

2 环路滤波器设计

由于无源环路滤波器引入的噪声少,因此应用非常多。一般地,当电荷泵对环路滤波电容充放电所提供的压控电压能达到VCO压控端要求时都采用无源环路滤波器;当该压控电压达不到VCO压控端控制要求的时候才用有源环路滤波器,因此我们讨论无源环路滤波器的设计。

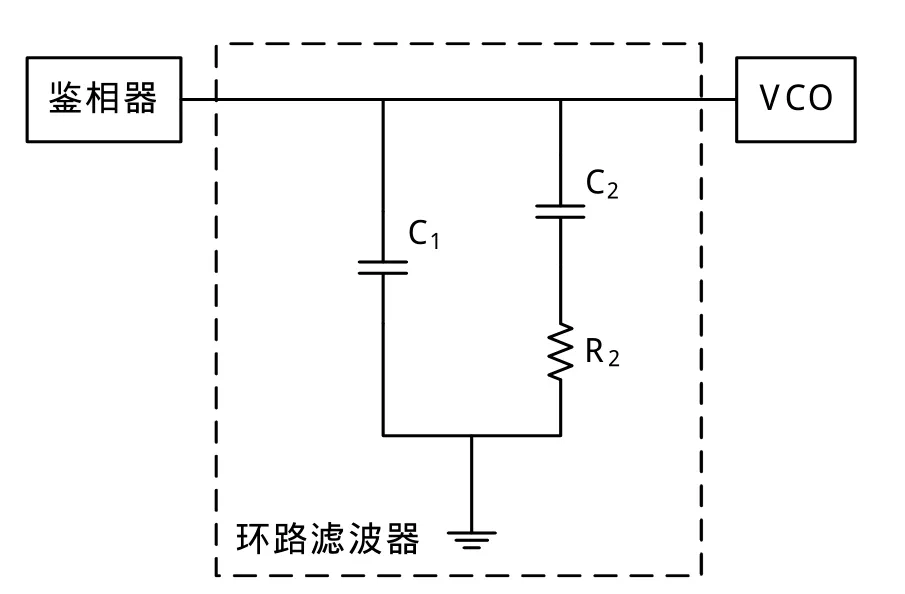

环路滤波器的最低阶数为二阶,二阶无源环路滤波器的电阻很小,可以获得较小的热噪声,同时其末端电容比较大,可以忽略VCO输入电容的影响,能够很好地满足一般设计的要求。三阶及三阶以上的无源环路滤波器是在二阶滤波器后端加入一阶或多阶RC滤波,这样对距输出信号中心频率超过10倍环路带宽的杂散有更好的抑制。在滤波器电路设计时,二阶无源环路滤波器与三阶及三阶以上无源环路滤波器的器件值计算方法基本相同,不同的是后者较前者由于有后端RC电路的加入而增加了一个或多个时间常数。在此我们以二阶无源环路滤波器为例推导环路滤波器设计方法。二阶无源环路滤波器电路形式如图2所示。

图2 二阶无源环路滤波器

二阶无源环路滤波器电路传递函数为

相位裕度φ是环路滤波器设计中一个非常重要的参数,它是锁相环开环传递函数在伯德图上形成的性能参数,是用于考核锁相环稳定性的依据。其定义是锁相环开环增益为0 dB时所在频点对应的相位值减去-180°,如果该值大于0,则环路稳定;该值小于0则环路不稳定。根据相位裕度的定义可以获得其计算式[4]:

至此,环路滤波器的元件值计算完毕。

3 优化设计

在上述的环路滤波器设计中,在计算前还有2个量需要设定:环路带宽ωc和相位裕度φ。

环路带宽ωc一般为鉴相频率的1/5~1/20,其值与环路输出信号的噪声和锁定时间有关,取值时主要考虑噪声因素。锁相环环路对输入参考信号、鉴相器和分频器的噪声是低通的,对VCO的噪声是高通的,因此ωc的值较小时可以很好地抑制输入参考信号、鉴相器和分频器的噪声,ωc的值较大时则对VCO的噪声有效抑制。在设计环路滤波器时,环路带宽ωc应根据对不同噪声的抑制需要综合分析选取[5]。

相位裕度φ的取值主要关系到环路锁定时间,通常取45°~50°。仿真表明当φ取48°左右时按照上一节的计算方法所获得的环路锁定时间达到最小,因此若锁定时间为主要考虑因素则相位裕度的初值可设为48°[4]。而根据反馈系统理论可知,φ的值越大环路越稳定,于是我们对φ取大于48°时的锁相环路进行仿真分析。

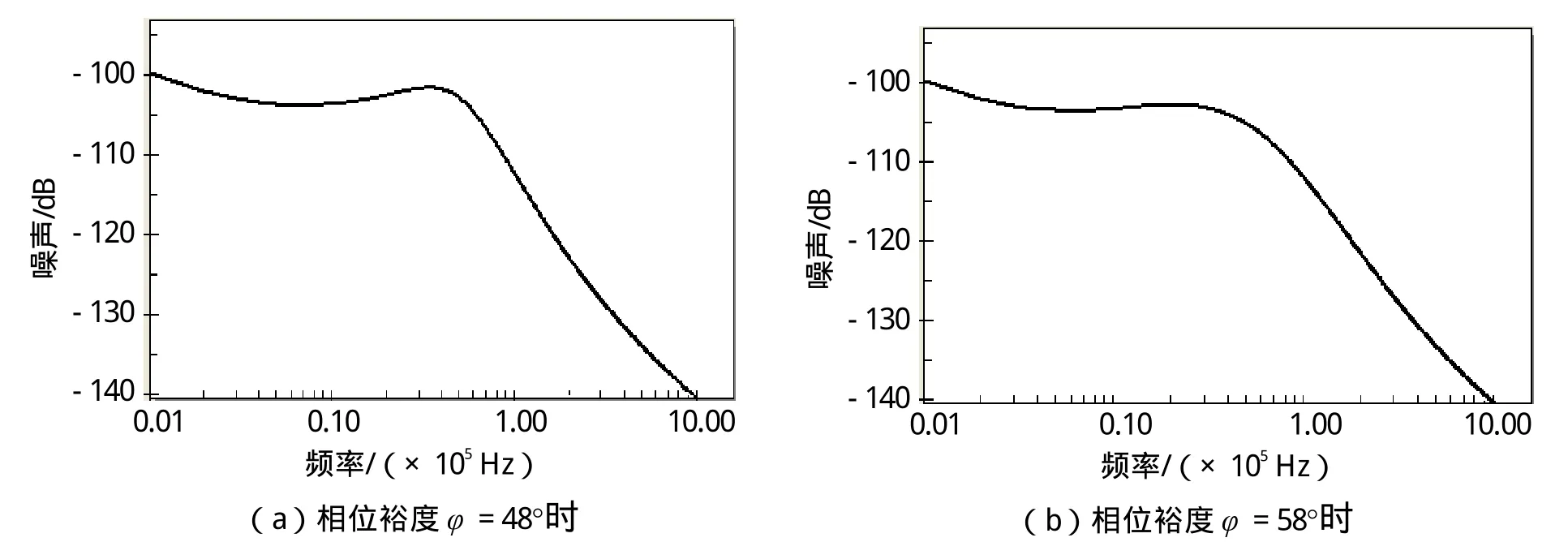

以一个锁相环电路为例,其参数为:鉴相频率为1 MHz,输出信号频率为800 MHz,电荷泵输出电流为4 mA,VCO的压控系数为50 MHz/V,环路带宽为40 kHz。当相位裕度分别为48°和58°时,按照上一节的方法设计出环路滤波器后,通过仿真可以得到锁相环闭环传递函数曲线分别如图3(a)和(b)所示。

图3 相位裕度不同的闭环传递曲线

从图3中的曲线可以看到环路的相位裕度为58°时与相位裕度为48°时相比,闭环传递函数曲线在环路带宽附近变得平滑。此外对两个不同相位裕度的锁相环进行噪声仿真(输出信号噪声曲线如图4所示)还可以看到相位裕度为58°时,输出信号的噪声在环路带宽附近也会有一些优化,约5 dB。

图4 相位裕度不同的VCO输出噪声

所以在锁定时间不是主要考虑因素的时候可以通过把φ的值设计得大一些从而对环路进行优化。例如采用锁相环技术设计原子频标倍频电路时,相位噪声和环路稳定性是首要因素,另外为了降低调制信号的引入对频谱纯度的影响[6]需闭环频率响应曲线尽可能平滑[4],可适当增大相位裕度进行优化设计。

增大相位裕度对环路带来的负面影响是增大了环路锁定时间。而在有的锁相环电路设计中,锁定时间也是需要考虑的一个重要因素。下面讨论提高环路相位裕度的同时,如何兼顾锁定时间的优化。

第2节中引入式(4)计算环路滤波器时,假定环路的开环相位在环路带宽处取得最大值。这种假定在相位裕度φ=48°时可以获得最小的环路锁定时间,但当φ≠48°时,虽然计算得到的环路仍有较小的锁定时间,但不是最小锁定时间。因此引入一个新的参数γ对式(4)稍加改变以优化锁定时间[4]。

显然,相位裕度φ=48°时,γ取1则环路具有最小锁定时间。当φ≠48°时,γ初值可设为1,上下调节选取具体值。图5是对之前设计的相位裕度为48°、γ为1的锁相环和相位裕度为58°、γ分别为0.8,1和1.2的锁相环进行锁定时间的仿真结果。

图5 锁相环锁定时间的仿真结果

仿真结果显示,φ=48°,γ=1的锁相环锁定时间最短,为63.20 µs;γ=1而φ=58°的锁相环锁定时间明显增加;保持φ=58°,γ变为1.2后锁定时间进一步增加;保持φ=58°不变,而γ变为0.8后,锁相环的锁定时间变小,虽然没有达到φ=48°时的最短锁定时间,但已十分接近,为69.10 µs。

进一步仿真可以得到,当φ<48°时,最小锁定时间对应的γ>1;当φ>48°时,最小锁定时间对应的γ<1。

由上述分析可以知道,适当调整相位裕度φ和设计参数γ,可以完成兼顾相位噪声和锁定时间的优化。当设计的频率源环路锁定时间也是需要考虑的主要因素时,利用上述方法改变相位裕度φ和设计参数γ可在保证环路接近最优锁定时间的前提下完成对相位噪声和环路稳定性的优化。

4 结论

输出信号的相位噪声和环路稳定性是采用锁相环设计频率源时需要考虑的重要因素,因此在环路滤波器设计时,需要注意对其优化设计。本文从环路滤波器传递函数出发推导了二阶无源环路滤波器设计方法并讨论了其优化设计。仿真结果显示,增大环路相位裕度可以使环路闭环环路更加稳定、环路增益曲线更平滑、环路带宽附近的噪声也更小,但同时锁定时间增加;而适当调整设计参数γ可以减小锁定时间,弥补相位裕度增大后的缺陷。因此,通过对相位裕度φ和设计参数γ的优化,可以在环路锁定时间接近最小值时使环路的闭环频率相应曲线更平滑、环路带宽附近的输出噪声更小。

[1] 远坂俊昭.锁相环(PLL)电路设计与应用[M].何希才, 译.北京: 科学出版社, 2006.

[2] 谢亮, 芦旭, 吴成英, 等.基于ADF4360-8的锁相环频率合成器的设计与实现[J].时间频率学报, 2013, 36(2): 75-83.

[3] 杨坡, 黄显核, 夏丹丹.电荷泵锁相环环路滤波器设计[J].声学技术, 2011, 30(4): 369-372.

[4] BANERJEE D.PLL Performance, Simulation and Design[M].Indianapolis: Dog Ear Publishing, 2006.

[5] 毕胜兰, 戴宇杰, 张小杰, 等.电荷泵锁相环系统相位噪声分析[J].南开大学学报, 2008, 41(3): 101-104.

[6] 黄良玉,张涤新, 陈江, 等.磁选态铯钟内辐射频移及其对准确度的影响[J].真空与低温, 2011, 17(1): 13-16.

Design and optimization of charge pump PLL′s loop filter

LIAN Ji-qing1,2,3,CHEN Da-yong1,2,3,ZHAI Hao1,2,3

(1.Lanzhou Institute of Physics,Lanzhou 730000,China;2.Core Professional Laboratory of Quantum Frequency Standard Technology,Lanzhou 730000,China;3.Science and Technology on Vacuum Technology and Physics Laboratory,Lanzhou 730000,China)

A loop filter that directly influences the performance of the PLL(phase-locked loop) circuit plays a critical role in the design of PLL frequency synthesizer.Taking the passive second order loop filter as an example,we introduced a design of charge pump PLL′s loop filter.Moreover we discussed an optimization design of the loop filter based on the phase margin and design parameter γ.The simulation results show the correctness and effectiveness of the design and optimization method.

loop filter; PLL(phase-locked loop); charge pump; phase margin; parameter optimization

TN74

A

1674-0637(2015)01-0038-06

10.13875/j.issn.1674-0637.2015-01-0038-06

2014-02-24

廉吉庆,男,硕士研究生,主要从事原子频标技术方面的研究。