The Implementation of CRC Algorithm Based on FPGA

2015-10-13ZHANGYanRENYongfengQILeiYAOZong

ZHANG Yan,REN Yongfeng,QI Lei,YAO Zong

(Science and Dynamic Testing of Ministry and Education Key Laboratory Instrument of North University of China,Taiyuan 030051,China)

The Implementation of CRC Algorithm Based on FPGA

ZHANG Yan,REN Yongfeng*,QI Lei,YAO Zong

(Science and Dynamic Testing of Ministry and Education Key Laboratory Instrument of North University of China,Taiyuan 030051,China)

As FPGA is high speed,high efficiency,flexible and stable,high integration,etc.,so the use of FPGA in serial communications to achieve serial communication is essential.Due to the uncertainty in communication transmission and interference,serial communication often appears abnormal situation.Thus,adding the CRC in serial communication,can greatly improve the reliability of communication.On the basis of the discussion about the principles of the CRC,we present with the principle of hardware achievement and uses VHDL hardware description language to achieve CRC check,to verify the feasibility of the program.

electron;FPGA;CRC check;serial communication;VHDL

信息在传递过程中,可能因某种原因使传输的数据发生错误。为减少和避免这类错误的发生,除提高硬件的可靠性外,在数据的编码上也应提供检错和纠错的支持。具体做法是:在要传送的数据代码中加入若干个校验位,使之在传送过程中若发生错误则会生成非法代码而被发现,甚至能根据非法代码确定错误的位置而给予纠正,这种具有检错或纠错能力的编码即校验码[2]。CRC码也叫循环冗余校验码,它是一种高效能的检错和纠错码,它可以把99.997%以上的各种错误都检查出来,是数据通信领域中最常用的一种差错校验码;其特征是信息字段和校验字段的长度可以任意选定[3]。

1 CRC校验原理

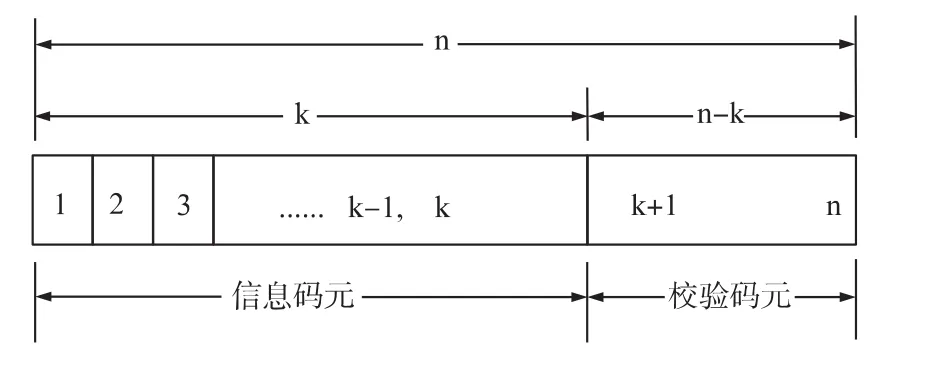

CRC校验码是一种典型的分组码,码组的构成如图1所示,由k个信息码元和n-k个检验码元构成,CRC码也称为('n,k)码。

图1 CRC校验码

现以图2为例说明CRC校验原理:CRC校验原理类似于算数中的除法运算,其中用到的减运算相当于CRC校验中的XOR(异或)运算;在本例中,原始数据为1111,“除数”1001为生成多项式,也称为POLY,常用G(x)表示;得到的“余数”110即为CRC校验码[4]。

图2 CRC校验原理框图

校验步骤为:

(1)首先将发送端要发送的数据进行扩展(扩展位数=生成多项式的位数-1);数据位进行扩展,是为了所有的数据位都可以处理到;

(2)按图2中(a)所示的步骤,计算CRC码;

(3)发送端将CRC码加到原始数据之后,一起发送出去;

(4)接收端用接收到的数据,除以与发送端相同的POLY值,如果计算得到的余数为0,说明接收到的数据正确,如图2(b)所示;反之则不正确[5]。

2 硬件实现

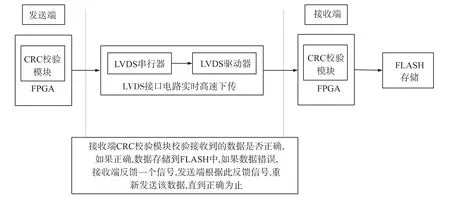

在数据通信中,采用CRC校验方法,可使通信的误码率大为降低,确保了数据通信的可靠性。其原理图框图如图3所示。

图3 CRC校验硬件实现原理框图

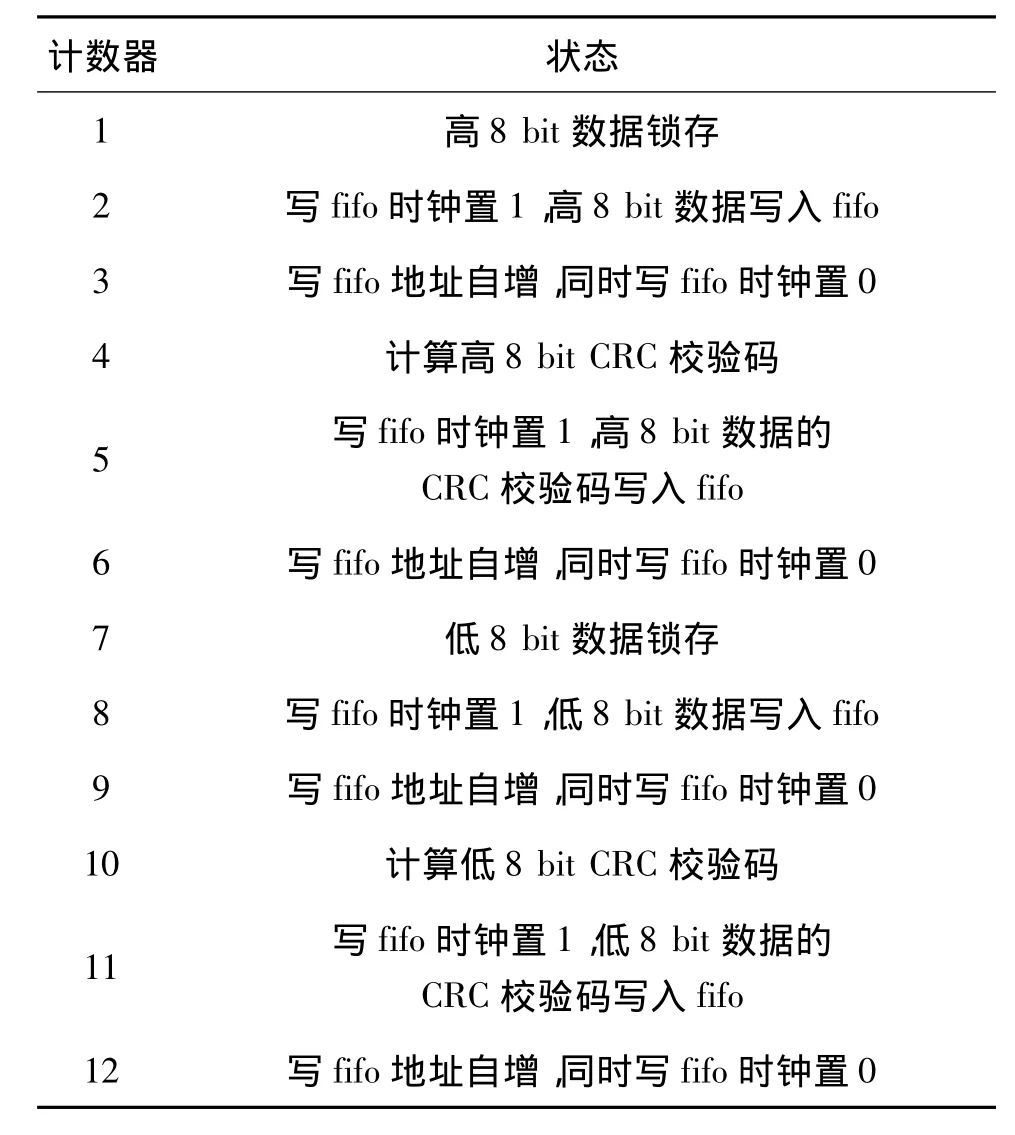

本设计采用Xilinx公司Spartan-3系列XC3S400 FPGA作为主控制器,使用36.864 MHz晶振,通过VHDL语言对FPGA编程;采用的ADC转换芯片为16 bit精度的AD7621,为了节省FPGA的I/O口资源,AD7621采用8 bit并行口工作模式,模拟量转换成数字量后,由BYTE信号控制AD7621向FPGA输出高8 bit和低8 bit。基于此,设计思想总结为:先将模拟量数据高8 bit锁存,同时将高8 bit数据作为CRC校验模块的输入并计算其CRC校验码,并将CRC校验码转存入下一级的FIFO中,低8 bit模拟量数据同理,详见表1。

表1 发送端原始数据及CRC校验码的锁存与计算

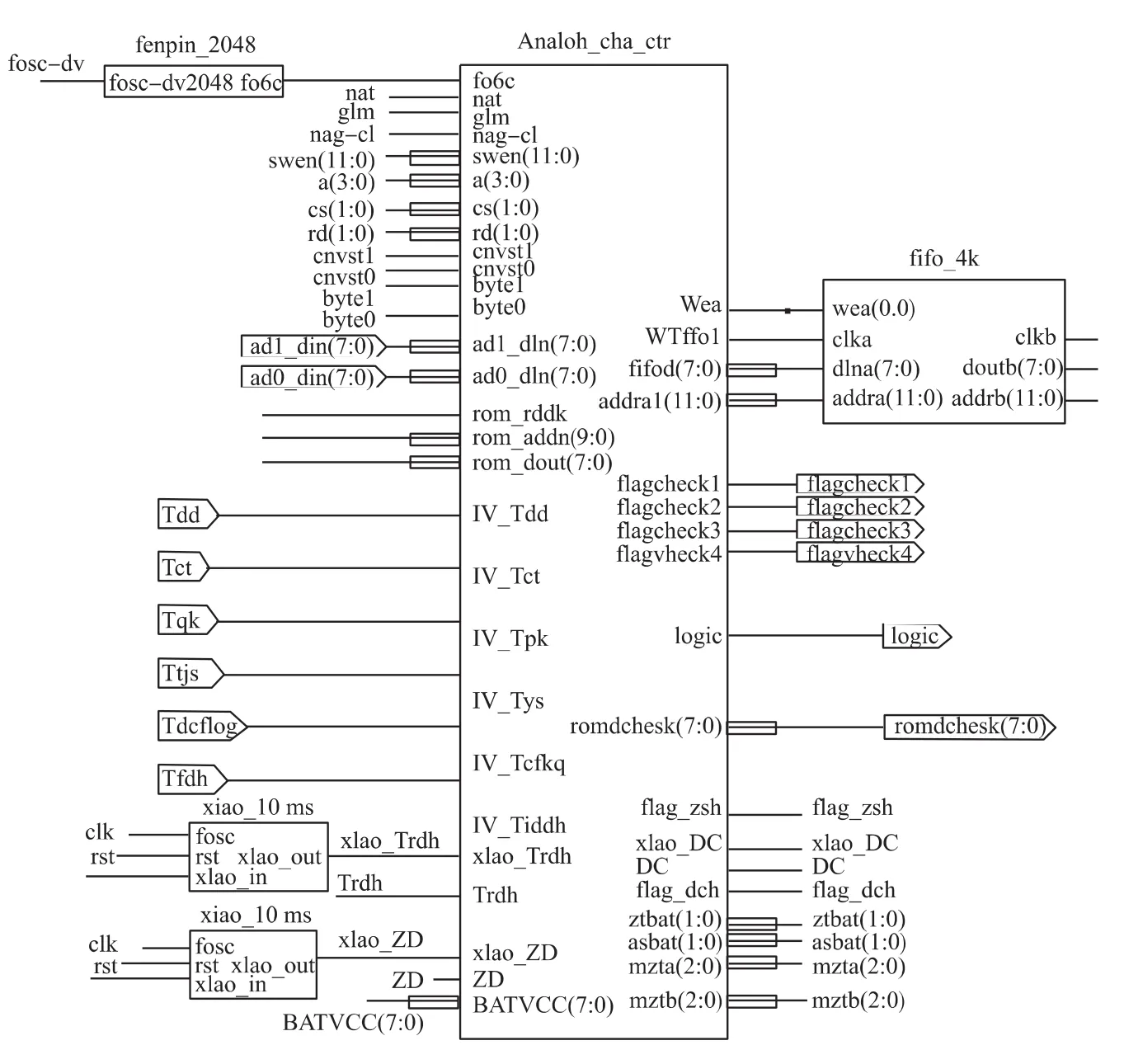

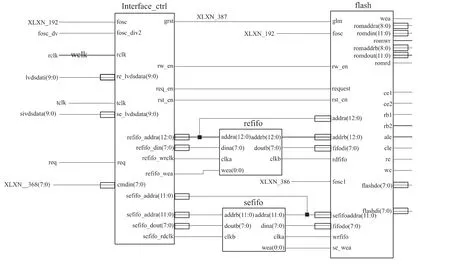

因此,发送模块、接收模块的FPGA内部原理图分别如图4、图5所示,Analog_cha_ctr模块主要用于数据帧的接收,实现模拟量数据流的控制并分别计算高8 bit CRC码、低8 bit CRC码,然后将接收到的数据帧转存到下一级FIFO中。Interface_ctrl模块用于接收数据,并将接收到的数据与接收到的CRC码进行异或运算,如果运算结果为“0000000”,则说明接收到的数据正确,反之,则反馈给接收端一个信号,接收端重新发送数据[6]。

图4 发送端FPGA实现CRC校验原理图

图5 接收端FPGA实现CRC校验原理图

3 VHDL逻辑设计

CRC校验原理对应算法的实现主要由一个r bit的移位寄存器和一些可控异或单元组成,其硬件实现示意框图如图6所示。

图6中由R0、R1、…、Rr-1构成的CRC寄存器是一个r bit移位寄存器组,用来存储r bit的CRC校验码R(x)。运算控制开关g1、g2、…、gr-1的位置与生成多项式G(x)的系数相关,对应系数1的开关接通反馈支路(上端),否则接地(右侧)。

这种算法简单,容易实现,对任意长度生成多项式的g(x)都适用。因为这种算法一次只能处理一位数据,故主要用于串行通信中。

具体算法如下:

图6 VHDL逻辑设计实现原理图

(1)初始化寄存器;

(2)将寄存器中的数据左移一位,读入1个新的数据位并置于寄存器的最低位;如果移出的数据位为0,不做处理,如果为1,则将寄存器中的数据与POLY项进行异或运算;

(3)重复步骤2,直至将所有的数据位处理完;

(5)寄存器的内容即为CRC校验码[7];

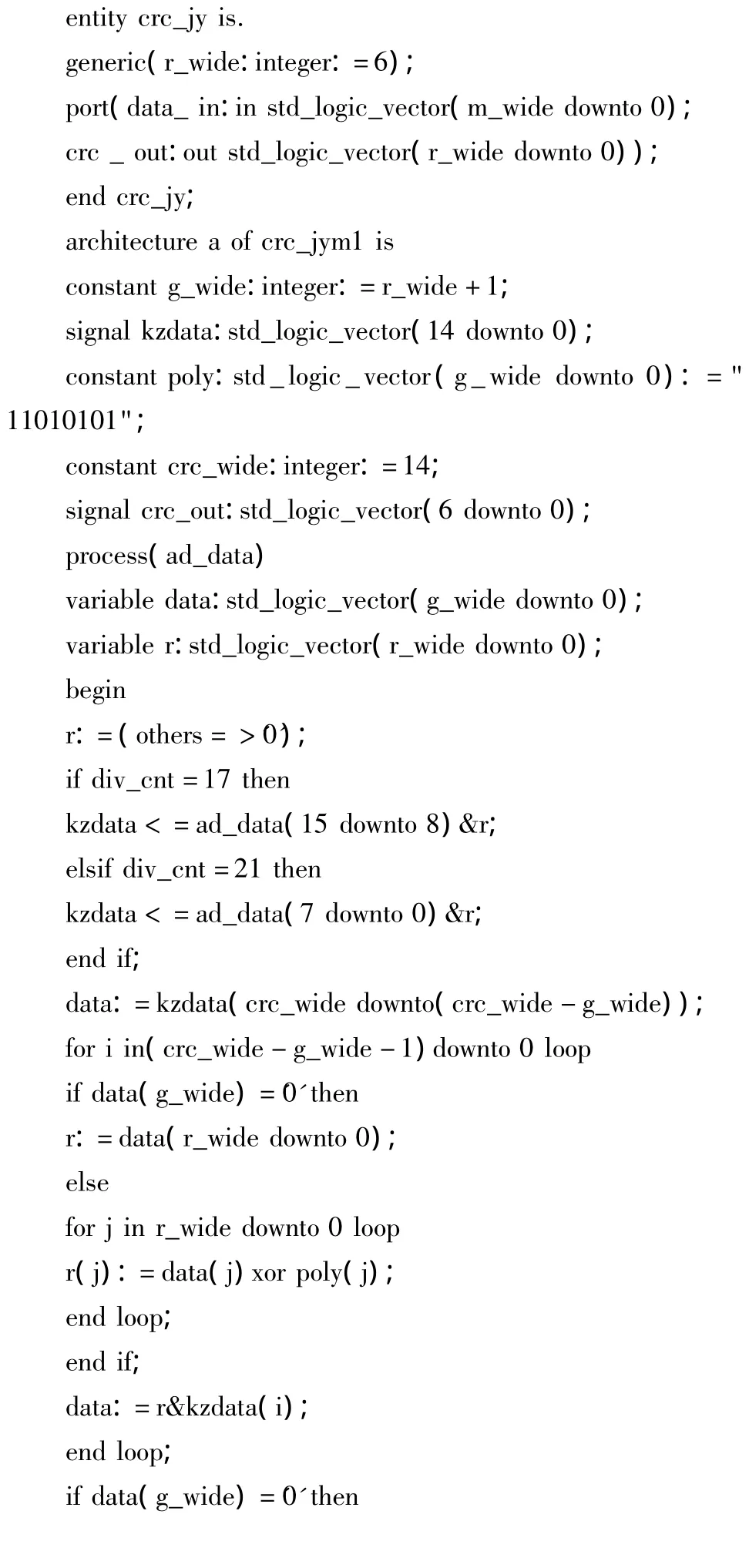

逻辑如下:

4 仿真

首先利用Xilinx ISE 13.1对计算CRC校验码的模块进行了仿真,利用软件提供的VHDL Test Bench模块,可以对代码进行动态的全面测试。因Xilinx ISE 13不支持使用波形生成仿真向量的方法,须使用HDL语言建立测试向量进行仿真向量行为的描述。测试向量文件如下:

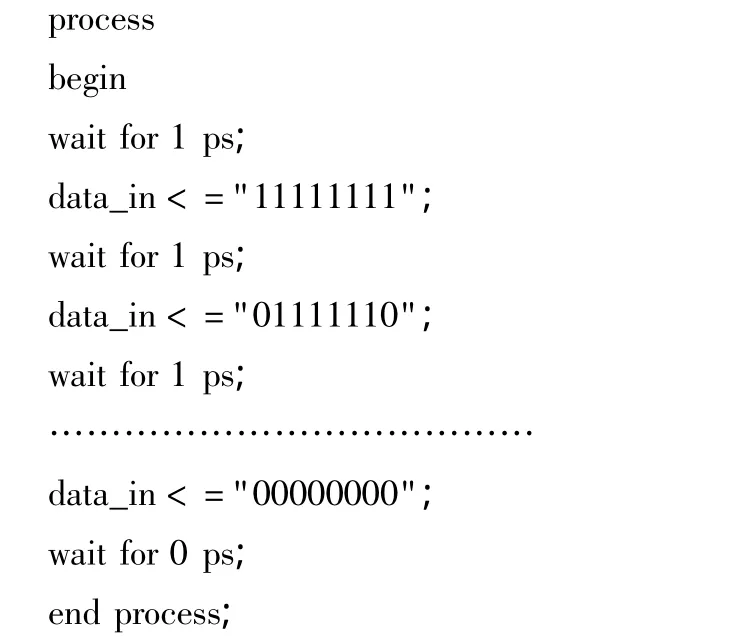

其仿真结果如图7所示,图中data_in即为程序设定的原始数据,crc_out为计算出的对应的CRC码,Poly项为:11010101。例如:原始数据11111111的CRC码即为0001110。

图7 CRC校验码生成模块仿真

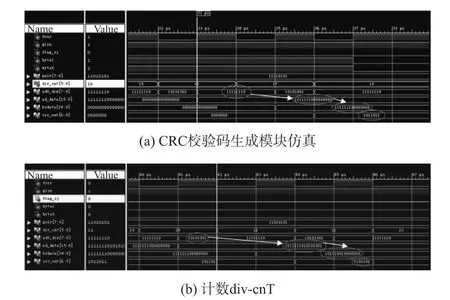

图8为将CRC模块加入到源程序中的时序仿真图,其中fosc为时钟信号,glrn为复位信号,flag_cj为采集信号,byte1、byte0用于控制数据的高8 bit、低8 bit切换,poly为选定的生成多项式,div_cnt为计数器,ad0_din即为采集到的16 bit模拟量数据,ad_data用于锁存数据的高8 bit、低8 bit,kzdata为将原始数据进行扩展后的数据,crc_out即为计算出的CRC校验码。

图8(a)所示为:当计数器div_cnt为16时,ad0 _din为采集到的原始数据的高8 bit,首先将数据锁存到ad_data,ad_data为1111111000000000;当计数器为17时,将ad_data的高8 bit数据进行扩展,并计算其CRC码,计算结果为1011011。

图8(b)所示为:当计数器div_cnt为20时,ad0 _din为采集到的原始数据的低8 bit,首先将数据锁存到ad_data,ad_data为1111111010101001;当计数器为21时,将ad_data的高8 bit数据进行扩展,得到扩展后的数据为:101010010000000,再计算其CRC码,计算结果为1101101。

图8 发送端CRC时序仿真

5 总结

本文基于CRC校验原理,详细介绍了CRC校验的硬件实现原理;在实现了串口通信数据的采集、处理与发送的基础上,加入了CRC检验码的生成过程及具体校验过程,在接收端将数据存储到FLASH中之前,总是先判断接收到的数据是否正常,若有误码,可通过CRC校验及时发现,接收端通过收到的反馈信号重新发送数据,使得误码的概率得到大幅度的降低[8];通过Xilinx ISE 13.1自带的仿真软件进行了仿真,从而验证了该设计的可行性。该方案的特点是实现容易,速度快,效率高,实用性强。

[1]姚七栋,张春玉.CRC校验及其软件实现[J].现代电子技术,2006,29(13):67-68.

[2]张树刚,张遂南,黄士坦.CRC校验码并行计算的FPGA实现[J].计算机技术与发展,2007,17(2):56-58.

[3]同晓荣.基于FPGA的PCM基群设备串行通讯CRC校验的实现[J].河南科学,2012,30(2):231-234.

[4]季鹏辉,孟丁,任勇峰.基于FPGA的16 bit CRC校验查表法设计[J].电子器件,2013,36(4):580-584.

[5]金志超,张磊,黄莉莉.远程地面测发控系统在PLC中嵌入CRC代码校验[J].航天控制,2009,27(2):81-83.

[6]周泰荚,王新梅,葛嫦.在CRC校验中扩展缩短码的设计与性能分析[J].西北工业大学学报,2001,22(5):640-642.

[7]林凯宏,游林儒,王立松.CRC校验算法在I/O扩展上的应用[J].控制与检测,2009(12):69-77.

[8]张增波,陈仲林,肖刘.基于FPGA的内置并行CRC校验的UART[J].总线与网络,2013,28(2):30-32.

张焱(1989-),女,汉族,山西平遥人,中北大学电路与系统专业在读研究生,研究方向为电路与系统,1039224079@ qq.com;

任勇峰(1968-),男,汉族,山西中阳人,博士,教授,现从事动态测试、高速数据采集等领域的研究。

EEACC:621010.3969/j.issn.1005-9490.2015.01.047

基于FPGA的CRC校验算法的实现

张焱,任勇峰*,齐蕾*,姚宗

(中北大学仪器科学与动态测试教育部重点实验室,太原030051)

由于FPGA具有速度快、效率高、灵活稳定、集成度高等优点,所以在串行通信中采用FPGA来实现串口通信是十分必要的。由于通信传输的不确定性以及干扰等原因,串行通信经常会出现异常情况[1]。因此,在串行通信中添加CRC校验,可大幅度提高通信的可靠性。在论述了CRC校验原理的基础上,提出了硬件实现原理,并用VHDL硬件描述语言实现CRC校验,验证了方案的可行性。

电子;FPGA;CRC校验;串行通信;VHDL

TN919.3

A文献标识码:1005-9490(2015)01-0222-05

2014-03-17修改日期:2014-04-30

猜你喜欢

杂志排行

电子器件的其它文章

- The Implementation of DDFS by Using Six Segments QLA Algorithm

- A Power Optimization Strategy of Directive Cache on DSP*

- Design of Intelligent Indoor Air Purification System*

- Design of Oxygen Concentration Detection Based on WiFi and Cloud Intelligent*

- Design of the Efficient Control System of Automatic Meteorological Station*

- Design and Implementation of Robust Smart Agricultural Control System*