基于电快速脉冲群发生器主电路的建模和设计

2015-09-18吴仕兵

朱 武,吴仕兵

(上海电力学院 电子与信息工程学院,上海 200090)

0 引言

电快速瞬变脉冲群发生器模拟脉冲干扰信号用于检验电子设备抗瞬变脉冲的能力,是电子产品脉冲抗扰度试验的重要设备。因此,电快速瞬变脉冲群发生器在电子工业中得到广泛应用。电快速脉冲群发生器主电路输出波形性能的好坏对整个电快速瞬变脉冲群抗干扰度的试验效果至关重要。在IEC61000-4-4标准中给出了电压归一化情况下单个高压脉冲的要求,高压脉冲波形的上升沿为5×(1±30%)ns,脉冲波形的半宽在 50×(1±30%)ns范围内,当发生器设定电压为Up时,在50 Ω负载上测量的输出电压应为 0.5Up(1±10%)[1-2]。 可查资料中缺乏对脉冲形成主电路的设计进行系统的研究论证[3-6],为适应试验标准的修订和补充[7],本文基于脉冲群发生器工作原理,采用电网络分析方法,建立主电路的数学模型,确立发生器主电路的结构参数,并考虑寄生参数对输出波形的影响,系统地研究主电路结构参数和寄生参数对脉冲波形的影响。在此基础上设计合理的波形形成主电路,通过搭建试验平台对脉冲波形进行测试,对提高电快速瞬变脉冲群发生器输出波形的质量有重大意义。

1 建模过程

1.1 脉冲群主电路的工作原理

图1 主回路原理图Fig.1 Schematic diagram of main circuit

电快速瞬变脉冲群发生器主电路的原理如图1所示,包括储能电路模块、放电开关K、信号形成电路模块和脉冲群输出模块。其中储能电路主要元件有充电电阻Rc和储能电容Cc,信号形成电路主要包括阻抗匹配电阻Rm、隔直电容Cd、脉冲持续时间形成电阻Rs。脉冲通过50 Ω的同轴衰减器输出。

电快速瞬变脉冲群发生器的工作过程如下:首先,高压电源通过充电电阻对储能电容Cc进行充电,一定时间之后,放电开关K闭合,储能电容Cc中的能量会通过脉冲形成电路进行释放,在输出端口形成高压纳秒级的脉冲。当储能电容Cc中的能量释放一定时间之后,放电开关K断开,储能电容Cc停止释放能量,高压电源对储能电容进行充电。在下一次驱动信号作用下,放电开关K再次闭合,重复前述动作,通过50 Ω的同轴衰减器输出连续的高压脉冲群信号。

1.2 电快速脉冲群发生器等效电路及参数

电快速脉冲群发生器输出的高压脉冲上升沿为5 ns,脉冲半宽为50 ns,考虑高压线路和电子开关的寄生电感的作用,本文建立的脉冲群发生器主电路等效电路模型如图2所示。为了简化模型,Us为电子开关之后即阻抗匹配电阻Rm前的电压值,其中L为电子开关和线路的寄生电感[8],开关闭合前高压电源给电容充满电,开关闭合后电容放电,在电感L和脉冲形成电阻Rs的作用下,形成纳秒级脉冲Us。在理想状态下建立模型,传输线路无分布电容,负载对整体电路无影响,开关闭合前电容充满电,Cc两端电压Uc初始值为U,Us初始值为0。

图2 发生器等效电路Fig.2 Equivalent circuit of generator

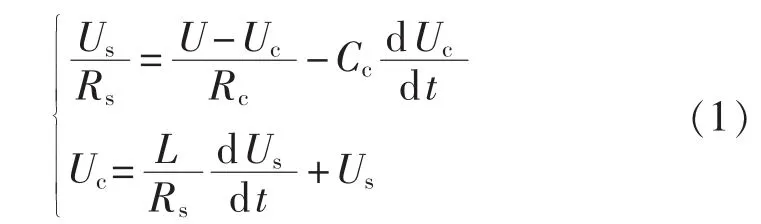

首先利用网络分析法建立时域下求解网络的微积分方程组如下:

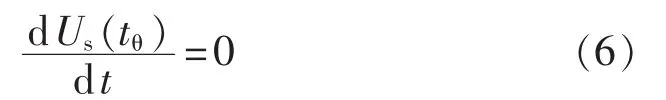

求解方程组(1)得到关于Us的解析式:

将方程组两边取拉普拉斯变换,得到复变数s为自变量的象函数代数方程并对方程求解得Us(s)为:

对所求得的象函数取拉普拉斯反变换,得到输出波形的解析表达式:

Us(t)具有双指数曲线的特征,与标准中的要求曲线特征相符。

IEC61000-4-4标准规定了隔直电容Cd=10 nF,确保脉冲群发生器的输出波形中没有直流分量,隔离负载电路对脉冲群发生器工作的影响。标准中提出阻抗匹配电阻Rm为50 Ω,决定了脉冲群发生器的输出阻抗。Cc、L、Rs和Rc配合决定了单个脉冲的上升沿和脉冲半宽,单个脉冲能量由储能电容Cc决定,文献[9]中提出在2 kV的高压电源下,脉冲能量小于 4 mJ,由

得到储能电容Cc小于2000 pF,取1200 pF。取电路中波形测试点前的电感L为100 nH,为了使电容快速充满电,Rc为150 Ω。标准中脉冲上升沿为5 ns,利用双曲线解析式(4),由双曲线最大值处导数为0,脉冲达到最大值时间为 5 ns,即 tθ=5 ns,由

得到 Rs≈159 Ω。

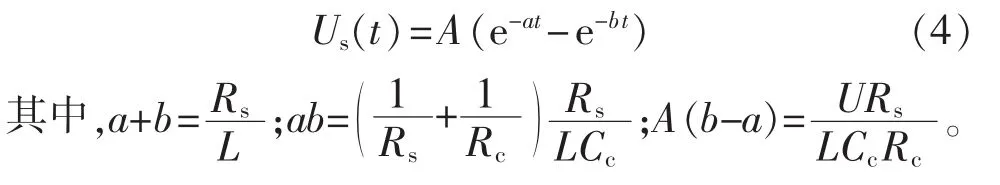

1.3 主电路模型的仿真

在求解出高压脉冲波形输出解析式和确定结构参数的基础上,本文在Pspice中建立仿真模型,其中充电电阻Rc为150 Ω,储能电容Cc为1200 pF,阻抗匹配电阻Rm为50 Ω,隔直电容Cd为10 nF,脉冲持续时间形成电阻Rs为159Ω,直流电源元件提供的直流电压为2 000 V,方波输出源和电压控制开关构成程控开关。为保证高压电源通过Rc给电容Cc充满电,设置开关在1000 ns时第一次闭合,模拟负载阻抗Reft为50 Ω。在50 Ω负载上测量输出波形如图3所示,脉冲幅值为918.27 V,上升沿达到5 ns,脉冲半宽为51 ns,脉冲波形的时间特性符合标准的要求。

图3 主电路仿真图Fig.3 Simulative curve of main circuit

2 主电路模型的优化

2.1 脉冲幅值特性的优化

在建模过程中,确定了电路的结构参数,Pspice仿真表明时间特性符合IEC61000-4-4标准的要求。仿真中输出电压为918.27 V,与标准中理论值相对误差为8.17%。为了使输出端电压更符合标准,采用单一变量法,其他结构参数不变,在放电开关后面并联陡化电容[10-11]提高脉冲幅值,与实际应用相对应,陡化电容Cp分别取10 pF、100 pF和1000 pF,仿真结果如图4所示。从结果可知,当陡化电容为10 pF时,幅值和波形与未置陡化电容时基本相同,当陡化电容为100 pF和1000 pF时幅值分别增大到1.2 kV和1.6 kV,波形半宽分别减小为35 ns和28 ns。由此可知,陡化电容的设置会影响脉冲幅值的大小,陡化电容越大,幅值增加越多,同时脉冲半宽有所减小。

图4 陡化电容仿真图Fig.4 Simulative curve for different sharpening capacitances

在电压设定值为2000V的情形下,经多次仿真取最优陡化电容为31.7 pF,高压脉冲峰值为1000.2 V,同时脉冲上升沿为4.1 ns,脉冲半宽为54 ns,均符合标准要求。

确定陡化电容后,采用单一变量法保持电路参数不变,改变发生器电压设定值,仿真结果如图5所示,波形的特征参数如表1所示。从仿真结果显示,脉冲峰值与电压设定值成线性关系,脉冲上升沿基本不变,脉冲半宽的变化也在标准要求范围内。

图5 不同电压输出脉冲波形图Fig.5 Waveform of output pulse for different voltages

表1 脉冲特征参数Table 1 Characteristic parameters of pulse for different voltages

因而在实际设计电路中,陡化电容的设置要综合考虑陡化电容大小对波形幅值特性和时间特性的影响。

2.2 寄生电感对脉冲波形的影响

脉冲群信号发生器需要输出稳定的纳秒级脉冲波,就要对发生器的结构参数和寄生参数进行严格的选取。标准中脉冲上升沿时间为t=5 ns,根据电快速瞬变脉冲信号的频谱宽度表达式(7)得到脉冲的频谱宽度约为63.5 MHz。

传送脉冲的导线较长,就可能导致高频成分溢出。一旦有信号溢出,传送的脉冲就会发生畸变。而且所有导体都是感性的,在高频率的情况下,非常小的一段导线或者电路板上线路的寄生电感都有可能造成很大的影响[12-13]。考虑到电子元件在电路中位置对波形输出的影响,假设高压放电主回路的导线在高频高压下形成的寄生电感只存在于负载的前后,且取值为200 nH,在Pspice仿真中分别在负载前、后置电感元件L1和L2,仿真效果如图6所示。

图6 模拟电感仿真图Fig.6 Simulative curve for different inductances

从仿真结果图可知,线路寄生电感对脉冲半宽基本没有影响,负载前置的电感使脉冲波峰变平缓,负载后置电感使波形更陡峭。总体而言,线路电感对脉冲半宽基本没有影响,主要影响了脉冲的上升沿时间。因此,设计高压主回路时传送高频脉冲导线的长度要尽可能的短,实际应用中直接使用PCB内嵌导体连接,减小电感影响。

电路设计中影响寄生电感的主要因素是电路板内嵌导体的几何尺寸,设带状导体模型是一个长方体。则带状导体电感量如下式所示[14]:

其中,u0为真空磁导率;l、w、h 分别为导体长、宽、高。经过实际测量所得PCB内嵌连接导体电感参数如表2所示。

表2 PCB内嵌导体线参数Table 2 Parameters for different embedded conductor lines of PCB

为了研究实际线路寄生电感对脉冲群发生器输出波形的影响,在Pspice软件中进行仿真研究。仿真模型如图7(a)所示,L1—L4为线路寄生电感,取表2所计算的值,Reft为模拟负载。仿真结果如图7(b)所示。

图7 线路电感仿真Fig.7 Simulation of circuitry inductance

脉冲形成主回路的内嵌导体寄生电感对波形影响不大,采用内嵌导体线连接的方式设计的主回路仿真输出的高压波形符合标准要求。

2.3 电快速瞬变脉冲群的实现

电快速瞬变脉冲群抗扰度试验机理是基于连续的脉冲干扰序列对受试设备的累积充电效应,为了达到连续的脉冲群序列,本文在Pspice建模中使用PWM电压控制开关(PWM脉冲源对应图7中的V1;电压控制开关对应图7中S)。

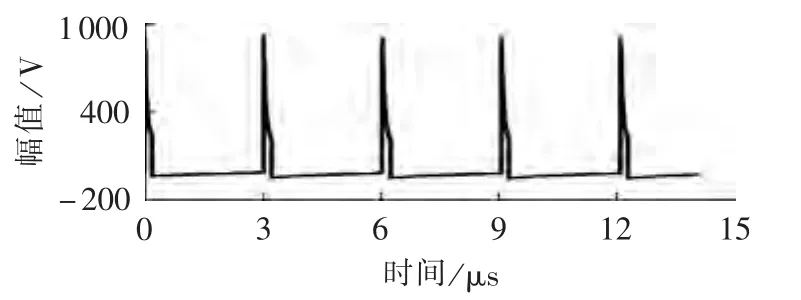

开关在PWM源的控制下有序地闭合与导通,储能电容有序地充放电,在脉冲形成电路的作用下形成高压脉冲群,如图8所示。

图8 脉冲群仿真图Fig.8 Simulative pulse train

3 主电路的设计与试验

综合考虑IEC61000-4-4标准的要求、实际元件的选择和对实际输出波形的优化[15-16],设计的主电路见图9。其中,R1为充电限流电阻,控制高压电源对储能电容的充电速度,限制回路电流;电容C1—C6为波形发生电路的主电容,采用瓷片电容,具有高频特性好、频率一致性较好等特点,其大小决定了单个脉冲的能量;波形形成电阻R3与储能电容相配合,决定了脉冲的形状;电容C7和R2组成积分电路,让波形前沿变缓,控制前沿参数。

图9 主电路设计图Fig.9 Design of main circuit

C9和R4的组合主要有2个作用:一是阻抗匹配;二是隔直作用,串接在电路中起微分作用。C10并接在波形回路输出极起积分作用,抬高波形输出尾部,增加波形能量以加强信号的干扰强度。因为脉冲群发生器产生波形为高压纳秒级脉冲,故所采用的电阻和电容要求相对较高。电阻值的大小应与电压、频率无关,寄生电感以及分布电容都要尽可能小。本设计中采用金属膜电阻,具有固有电感小、高频响应好等优点;电容在满足耐压的条件下,固有电感要尽可能的小,本设计中采用无感电容。

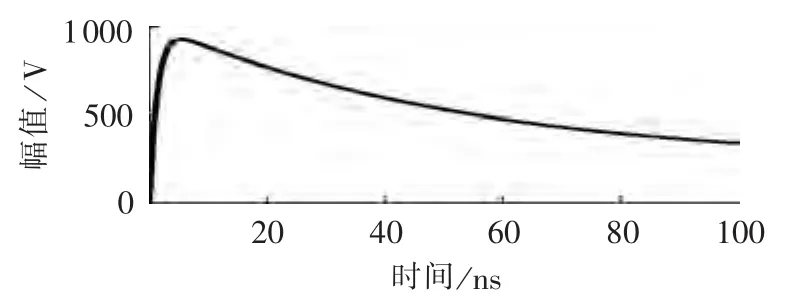

基于脉冲群发生器的主电路的模型,设计高压主回路PCB并进行脉冲波形测试试验。在2000 V的供电情形下,示波器测量脉冲曲线如图10所示,单个脉冲波峰值为956 V,脉冲上升沿为4.8 ns,半宽为41.0 ns,脉冲群下降沿有负值的跳变,与理论仿真相符,均符合技术标准的要求。

图10 主电路试验图Fig.10 Test of main circuit

4 结论

基于数学分析方法建立了脉冲群发生器主电路模型,并研究寄生参数对脉冲的影响。在此基础上结合Pspice仿真结果和实际电路需要,完成主电路的设计,并通过主回路试验进行结构参数验证,主电路输出波形上升沿达到4.8 ns,脉冲半宽达到41.0 ns,脉冲波峰幅度参数满足标准IEC61000-4-4的技术要求。电快速脉冲群发生器主电路的建模和设计是发生器总体设计的基础,同时为研究具有更快前沿的脉冲群发生器提供了设计经验。